# **CA-IS1305 5kV<sub>RMS</sub> Isolated Sigma-Delta Modulator**

#### 1 Key Features

- Differential Input Voltage Range: ±250 mV

- Ultra-Low Input Offset Voltage and Drift

- ±150µV(max) @ 25°C input offset voltage

- Low Gain Error and Drift

- ±0.3%(max) @ 25°C gain error

- ±40ppm/°C(max) gain drift

- Excellent AC Performance

- SNR: 85dB (typ)

- THD: -93dB (typ)

- 16-Bit Resolution with No Missing Codes

- Robust Isolation Barrier

- High lifetime: >40 years

- Up to 5000V<sub>RMS</sub> isolation rating

- ±150 kV/µs typical CMTI

- Fault Diagnostic Functions Improve System Safety

- Wide Operating Temperature Range: -40°C to 125°C

- 16-pin wide-body SOIC package

- Safety Regulatory Approvals(Pending)

- 7070 V<sub>PK</sub> isolation per DIN V VDE V 0884-11 (VDE V 0884-11): 2017-01

- 5000 V<sub>RMS</sub> isolation for 1 minute per UL 1577

- CQC and TUV certification approvals

#### 2 Applications

- Industrial Motor Controls and Drives

- Uninterruptible Power Supplies(UPS)

- Isolated Power Supply

#### 3 Description

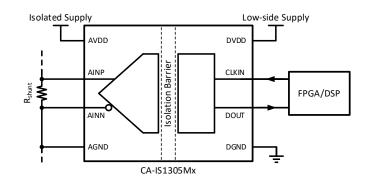

The CA-IS1305x family of devices is series of precision isolated sigma-delta ( $\Sigma$ - $\Delta$ ) modulator and optimized for shunt resistor-based current sensing or other small signal measurement applications. The input current-sense amplifier monitors current flow through a shunt (sense) resistor and the sigma-delta modulator converts the analog input to a digital bit stream of 1's and 0's at a much higher frequency. The digital output stage of CA-IS1305x provides uncoded bit-stream.

The analog input-side (high-side) and digital output-side (low-side) are separated by unique silicon oxide (SiO<sub>2</sub>) capacitive isolation barriers that provide up to  $5kV_{RMS}$  galvanic isolation per UL1577 certification, and isolator drivers transfer the output of the modulator across this isolation barrier. In systems with different voltage domains, this isolation technical is typically used to protect the low voltage side from the high voltage side in case of any faults. These devices also feature up to  $150kV/\mu s$  common mode transient immunity and enable efficient bit-stream transmission in noisy environments.

The CA-IS1305x devices' ultra-low input voltage range (±250mV) allows the use of small sense resistor to reduce power dissipation and a very low, 0.3% gain error ensures measurement accuracy. This family of devices also features fail-safe output to support high safety system design. The CA-IS1305x devices specified for operation with 5MHz to 21MHz clock input. The internal sigma-delta modulator combined with an external digital decimation sinc<sup>3</sup> filter can achieve 85 dB signal-to-noise ratio (SNR) at 78.1 Ksps.

The CA-IS1305x family is specified over the -40°C to +125°C operating temperature range and is available in 16-pin SOIC wide body package.

#### **Device Information**

| Part Number | nber Package Body Size(NOM |                    |

|-------------|----------------------------|--------------------|

| CA-IS1305x  | SOIC16-WB (W)              | 10.30 mm × 7.50 mm |

# **Simplified Schematic**

### 4 Ordering Information

### Table 4-1. Valid Parts Ordering Information

| Ordering Part Number                                                                                                                              | Specified Input Range | Galvanic Isolation (±V) | Differential Input<br>Resistance | Digital Output Encoded Mode |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|----------------------------------|-----------------------------|--|--|--|

| CA-IS1305AM25W                                                                                                                                    | ±250 mV               | 5000                    | 22 kΩ                            | Uncoded CMOS                |  |  |  |

| CA-IS1305M25W                                                                                                                                     | ±250 mV               | 5000                    | 22 kΩ                            | Uncoded CMOS                |  |  |  |

| Note:<br>The only difference between CA-IS1305M25W and CA-IS1305AM25W is pin arrangement. See Pin Configuration and Descriptions for more detail. |                       |                         |                                  |                             |  |  |  |

# **Table of Contents**

| 1 | Key F    | eatures                               | 1  |

|---|----------|---------------------------------------|----|

| 2 | Appli    | ications                              | 1  |

| 3 |          | ription                               |    |

| 4 | Orde     | ring Information                      | 2  |

| 5 |          | sion History                          |    |

| 6 |          | Configuration and Descriptions        |    |

| 7 |          | ifications                            |    |

|   | •<br>7.1 | Absolute Maximum Ratings <sup>1</sup> |    |

|   | 7.2      | ESD Ratings                           | 6  |

|   | 7.3      | Recommended Operating Conditions      |    |

|   | 7.4      | Thermal Information                   | 6  |

|   | 7.5      | Power Ratings                         | 6  |

|   | 7.6      | Insulation Specifications             | 7  |

|   | 7.7      | Safety-Related Certifications         | 7  |

|   | 7.8      | Electrical Characteristics            | 8  |

|   | 7.9      | Switching Characteristics             | 10 |

|   | 7.10     | Typical Characteristics and Waveforms | 11 |

| 8 | Deta     | iled Description                      | 16 |

|   | 8.1      | Overview                              | 16 |

|    | 8.2 | Ana      | log Input (High-side)               | 16 |

|----|-----|----------|-------------------------------------|----|

|    | 8.3 | Sign     | al Isolation                        | 17 |

|    | 8.4 | Digi     | tal Output (Low-side)               | 17 |

|    |     | 8.4.1    | Bit stream output                   | 17 |

|    |     | 8.4.2    | Over-range Output                   | 18 |

|    |     | 8.4.3    | Fail-Safe Output                    | 19 |

| 9  | Ар  | plicatio | n Information                       | 19 |

|    | 9.1 | Турі     | cal Application for Current Sense   | 19 |

|    |     | 9.1.1    | Typical Application Circuit         | 19 |

|    |     | 9.1.2    | Choosing the Current Sense Resistor | 20 |

|    |     | 9.1.3    | Analog Input Filter                 | 20 |

|    |     | 9.1.4    | Digital Output Filter               | 20 |

|    | 9.2 | Volt     | age Measurement                     | 21 |

|    | 9.3 | Pow      | er supply and PCB layout            | 22 |

| 10 |     | Packa    | ge Information                      | 24 |

| 11 |     | Solde    | ring Temperature (reflow) Profile   | 25 |

| 12 |     | Tape a   | and Reel Information                | 26 |

| 13 |     | •        | tant Notice                         |    |

|    |     |          |                                     |    |

# 5 Revision History

| <b>Revision Number</b> | Description                                                              | Page Changed |

|------------------------|--------------------------------------------------------------------------|--------------|

| Version 1.00           | Revised the CA-IS1305x specs.                                            | 7 - 9        |

| version 1.00           | Added typical characteristics and waveforms.                             | 10 - 13      |

|                        | Updated CMRR、PSRR、INL data;                                              | 9            |

| Version 1.01           | Updated IDVDD data and typical curves                                    | 10, 15       |

|                        | Added INL,DNL,CMRR and PSRR typical curves                               | 16           |

| Version 1.02           | Updated CA-IS1305M25 Pin description : PIN 1connected to AVDD internally | 5            |

# CA-IS1305x Version 1.03,2023/05/04

# 6 Pin Configuration and Descriptions

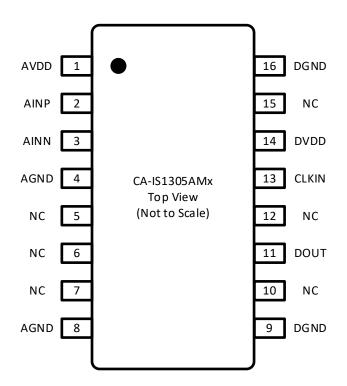

| Table 6-1. CA-IS1305AM25W Pin | <b>Configuration and Description</b> |

|-------------------------------|--------------------------------------|

|-------------------------------|--------------------------------------|

| NAME  | Pin #      | ТҮРЕ   | DESCRIPTION                                                                                         |  |

|-------|------------|--------|-----------------------------------------------------------------------------------------------------|--|

| AVDD  | 1          | Power  | Power supply input for the input-side (analog input-side), 4.5V to 5.5V.                            |  |

| AINP  | 2          | Input  | Noninverting analog input. External shunt resistor connection input (power-side) for current sense. |  |

| AINN  | 3          | Input  | Inverting analog input. External shunt resistor connection input (load-side)for current sense.      |  |

| AGND  | 4, 8       | Ground | High-side (input-side) ground.                                                                      |  |

| DGND  | 9, 16      | Ground | .ow-side (output-side) ground.                                                                      |  |

| DOUT  | 11         | Output | Modulator bit-stream output.                                                                        |  |

| CLKIN | 13         | Output | Modulator clock input(5 MHz to 21 MHz) with internal 1.5-M $\Omega$ pulldown resistor.              |  |

| DVDD  | 14         | Power  | Low-side (digital output-side) power supply. Bypass DVDD to DGND                                    |  |

| NC    | 5, 6, 7    | _      | No connection. Leave them open or connect to AVDD or AGND.                                          |  |

| NC    | 10, 12, 15 | -      | No connection. Leave them open or connect to DVDD or DGND.                                          |  |

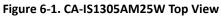

Figure 6-2. CA-IS1305M25W Top View

| NAME  | Pin #      | ТҮРЕ   | DESCRIPTION                                                                                         |  |

|-------|------------|--------|-----------------------------------------------------------------------------------------------------|--|

| AVDD  | 7          | Power  | Power supply input for the input-side (analog input-side), 4.5V to 5.5V.                            |  |

| AINP  | 2          | Input  | Noninverting analog input. External shunt resistor connection input (power-side) for current sense. |  |

| AINN  | 3          | Input  | Inverting analog input. External shunt resistor connection input (load-side)for current sense.      |  |

| AGND  | 4, 8       | Ground | High-side (input-side) ground.                                                                      |  |

| NC    | 1, 5, 6    |        | No connection. Leave them open or connect to AVDD or AGND.                                          |  |

| DGND  | 9, 16      | Ground | Low-side (output-side) ground.                                                                      |  |

| NC    | 10, 12, 15 |        | No connection. Leave them open or connect to DVDD or DGND.                                          |  |

| DOUT  | 11         | Output | Modulator bit-stream output.                                                                        |  |

| CLKIN | 13         | Output | Modulator clock input(5 MHz to 21 MHz) with internal 1.5-MΩ pulldown resistor.                      |  |

| DVDD  | 14         | Power  | Low-side (digital output-side) power supply, 3.0V to 5.5V.                                          |  |

|       | 1*         | -      | No connection. But connected to AVDD internally Leave it open or connect to AVDD                    |  |

| NC    | 5,6        | -      | No connection. Leave them open ,connect to AVDD or AGND                                             |  |

|       | 10, 12, 15 | -      | No connection. Leave them open ,connect to DVDD or DGND                                             |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>1</sup>

|                  | PARAMETER                                   | MIN    | MAX                         | UNIT |

|------------------|---------------------------------------------|--------|-----------------------------|------|

| AVDD, DVDD       | Supply voltage <sup>2</sup>                 | -0.5   | 6.5                         | V    |

| AINP, AINN       | Analog input voltage                        | AGND - | -6 6.5                      | V    |

| CLKIN, DOUT      | Digital input or output voltage             | DGND – | 0.5 DVDD + 0.5 <sup>3</sup> | V    |

| I <sub>IN</sub>  | Input current to any pin except supply pins | -10    | 10                          | mA   |

| Tj               | Junction Temperature                        |        | 150                         | °C   |

| T <sub>STG</sub> | Storage Temperature                         | -65    | 150                         | °C   |

Notes:

1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

- 1. All voltage values are with respect to the local ground terminal (AGND or DGND) and are peak voltage values.

- 2. Maximum voltage must not exceed 6.5V.

# 7.2 ESD Ratings

|                                          |                           |                                                                                        | VALUE | UNIT |

|------------------------------------------|---------------------------|----------------------------------------------------------------------------------------|-------|------|

| V <sub>FSD</sub> Electrostatic discharge |                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>1</sup>              | ±4000 | V    |

| VESE                                     | Electrostatic discharge   | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>2</sup> | ±2000 | v    |

| Not                                      | es:                       |                                                                                        |       |      |

| 1.                                       | Per JEDEC document JEP155 | , 500V HBM allows safe manufacturing of standard ESD control process.                  |       |      |

| 2.                                       | Per JEDEC document JEP157 | , 250V CDM allows safe manufacturing of standard ESD control process.                  |       |      |

### 7.3 Recommended Operating Conditions

|                | PARAMETER                                                      | MIN | NOM | MAX | UNIT |

|----------------|----------------------------------------------------------------|-----|-----|-----|------|

| AVDD           | High-side (analog input) supply voltage, with respect to AGND  | 4.5 | 5.0 | 5.5 | V    |

| DVDD           | Low-side (digital output) supply voltage, with respect to DGND | 3.0 | 3.3 | 5.5 | V    |

| T <sub>A</sub> | Operating ambient temperature range                            | -40 |     | 125 | °C   |

#### 7.4 Thermal Information

|                  | THERMAL METRIC                         |      |      |  |  |  |

|------------------|----------------------------------------|------|------|--|--|--|

| R <sub>θJA</sub> | Junction-to-ambient thermal resistance | 86.5 | °C/W |  |  |  |

#### 7.5 Power Ratings

|                 | PARAMETER                                | TEST CONDITIONS     | VALUE  | UNIT |

|-----------------|------------------------------------------|---------------------|--------|------|

| P <sub>D</sub>  | Maximum power dissipation for both sides | AVDD = DVDD = 5.5 V | 129.25 | mW   |

| P <sub>D1</sub> | Maximum power dissipation for high-side  | AVDD = 5.5 V        | 90.75  | mW   |

| P <sub>D2</sub> | Maximum power dissipation for low-side   | DVDD = 5.5 V        | 38.50  | mW   |

|                   | PARAMETR                                          | TEST CONDITIONS                                                                 | VALUE              | UNI             |

|-------------------|---------------------------------------------------|---------------------------------------------------------------------------------|--------------------|-----------------|

| CLR               | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                              | 8                  | mm              |

|                   | External groopage 1                               | Shortest terminal-to-terminal distance across the                               | 0                  |                 |

| CPG               | External creepage <sup>1</sup>                    | package surface                                                                 | 8                  | mm              |

| ITC               | Distance through the insulation                   | Minimum internal gap (internal clearance)                                       | 19                 | μm              |

| CTI               | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                           | > 600              | V               |

|                   | Material group                                    | According to IEC 60664-1                                                        | I                  |                 |

|                   |                                                   | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                      | I-IV               |                 |

|                   | Overvoltage category per IEC 60664-1              | Rated mains voltage ≤ 400 V <sub>RMS</sub>                                      | I-IV               |                 |

|                   |                                                   | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                      | -                  |                 |

| DIN V VC          | DE V 0884-11:2017-01                              | · · · · ·                                                                       |                    |                 |

| / <sub>IORM</sub> | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                            | 1414               | VPK             |

|                   |                                                   | AC voltage; Time dependent dielectric breakdown                                 | 1000               | V               |

| V <sub>IOWM</sub> | Maximum working isolation voltage                 | (TDDB) Test                                                                     | 1000               | V <sub>RM</sub> |

|                   |                                                   | DC voltage                                                                      | 1414               | V <sub>DO</sub> |

|                   |                                                   | V <sub>TEST</sub> = V <sub>IOTM</sub> ,                                         |                    |                 |

| VIOTM             | Maximum transiant isolation voltage               | t = 60 s (qualification);                                                       | 7070               | v               |

| IOTM              | Maximum transient isolation voltage               | $V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}}$                                  | 7070               | VPI             |

|                   |                                                   | t= 1 s (100% production)                                                        |                    |                 |

| ,                 |                                                   | Test method per IEC 60065, 1.2/50 μs waveform,                                  | 6250               |                 |

| IOSM              | Maximum surge isolation voltage <sup>2</sup>      | $V_{\text{TEST}} = 1.6 \times V_{\text{IOSM}}$ (qualification)                  | 6250               | V <sub>PI</sub> |

|                   |                                                   | Method a, After input/output safety test subgroup 2/3,                          |                    |                 |

|                   |                                                   | V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60 s;                 | ≤ 5                |                 |

|                   |                                                   | $V_{pd(m)} = 1.2 \times V_{IORM}, t_m = 10 \text{ s}$                           |                    |                 |

|                   |                                                   | Method a, After environmental tests subgroup 1,                                 | ≤ 5                |                 |

|                   | Apparent charges                                  | V <sub>ini</sub> = V <sub>IOTM</sub> , t <sub>ini</sub> = 60 s;                 |                    |                 |

| pd                | Apparent charge <sup>3</sup>                      | $V_{pd(m)} = 1.6 \times V_{IORM}, t_m = 10 s$                                   |                    | pC              |

|                   |                                                   | Method b1, At routine test (100% production) and                                |                    |                 |

|                   |                                                   | preconditioning (type test)                                                     | ≤ 5                |                 |

|                   |                                                   | $V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1$ s;                              | 20                 |                 |

|                   |                                                   | V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> , t <sub>m</sub> = 1 s           |                    |                 |

| Cio               | Barrier capacitance, input to output <sup>4</sup> | $V_{10} = 0.4 \times sin (2\pi ft), f = 1 MHz$                                  | ~ 1                | pF              |

|                   |                                                   | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                  | > 10 <sup>12</sup> |                 |

| RID               | Isolation resistance <sup>4</sup>                 | $V_{10} = 500 \text{ V}, \ 100^{\circ}\text{C} \le T_A \le 125^{\circ}\text{C}$ | > 10 <sup>11</sup> | Ω               |

|                   |                                                   | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                               | > 10 <sup>9</sup>  |                 |

|                   | Pollution degree                                  |                                                                                 | 2                  |                 |

| JL 1577           |                                                   | · · · · ·                                                                       |                    |                 |

| ,                 | Movies with stop disc is lation with a            | $V_{TEST} = V_{ISO}$ , t = 60s (qualification),                                 | F000               |                 |

| V <sub>ISO</sub>  | Maximum withstanding isolation voltage            | $V_{\text{TEST}} = 1.2 \times V_{\text{ISO}}$ , t = 1s (100% production)        | 5000               | V <sub>RM</sub> |

means of suitable protective circuits.

2. Devices are immersed in oil during surge characterization.

3. The characterization charge is discharging charge (pd) caused by partial discharge.

4. Capacitance and resistance are measured with all pins on high-side and low-side tied together.

#### 7.7 Safety-Related Certifications

| VDE (Pending)                            | UL                                    | TUV (Pending)                                |

|------------------------------------------|---------------------------------------|----------------------------------------------|

| Certified according to DIN V VDE V 0884- | Recognized under UL 1577 Component    | Certified according to EN 61010-1: 2010 (3rd |

| 11:2017-01                               | Recognition Program                   | Ed) and EN 60950-                            |

|                                          |                                       | 1: 2006/A2: 2013                             |

|                                          | SOIC16-WB: 5000 V <sub>RMS</sub>      |                                              |

| Certification number:                    | Certification number:E511334-20200520 | Certification number:                        |

# CA-IS1305x Version 1.03,2023/05/04

Shanghai Chipanalog Microelectronics Co., Ltd.

# 7.8 Electrical Characteristics

All minimum/maximum specs are at  $T_A = -40^{\circ}$ C to 125°C, AVDD = 4.5 V to 5.5 V, DVDD = 3.0 V to 5.5 V, AINP = -250 mV to 250 mV, AINN = AGND = 0V, and sinc<sup>3</sup> filter output configured to 16 bits with OSR = 256 (unless otherwise noted). All typical values are at 25°C with CLKIN = 20 MHz, AVDD = 5 V, and DVDD = 3.3 V (unless otherwise noted).

|                       | PARAMETER                                            | TEST CONDITIONS                                           | MIN      | ТҮР    | MAX           | UNIT  |  |  |

|-----------------------|------------------------------------------------------|-----------------------------------------------------------|----------|--------|---------------|-------|--|--|

| ANALOG I              | NPUT                                                 |                                                           | -        |        |               |       |  |  |

| V <sub>Clipping</sub> | Maximum input voltage before clipping output         | AINP – AINN                                               |          | ±320   |               | mV    |  |  |

| V <sub>FSR</sub>      | Specified linear full-scale input range              | AINP – AINN                                               | -250     |        | 250           | mV    |  |  |

| V <sub>CM</sub>       | Operating common-mode input voltage                  | (AINP + AINN) / 2 to AGND                                 | -0.16    |        | AVDD –<br>2.1 | V     |  |  |

| V <sub>CMOV</sub>     | Common-mode overvoltage threshold                    | (AINP + AINN) / 2 to AGND                                 | AVDD – 2 |        |               | V     |  |  |

| V <sub>CMOV_HYS</sub> | Hysteresis of common-mode over-<br>voltage threshold |                                                           |          | 100    |               | mV    |  |  |

| CIN                   | Single-ended input capacitance                       | f <sub>IN</sub> = 270 kHz, AINN = AGND                    |          | 2      |               | pF    |  |  |

| CIND                  | Differential input capacitance                       | f <sub>IN</sub> = 270 kHz                                 |          | 1      |               | pF    |  |  |

| R <sub>IN</sub>       | Single-ended input resistance                        | AINN = AGND                                               |          | 19     |               | kΩ    |  |  |

| R <sub>IND</sub>      | Differential input resistance                        |                                                           |          | 22     |               | kΩ    |  |  |

| I <sub>IN</sub>       | Input current                                        | AINP = AINN = AGND,<br>$I_{IN} = (I_{INP} + I_{INN}) / 2$ | -41 -30  |        | -24           | μA    |  |  |

| TCIIN                 | Input current drift                                  |                                                           | ±1       |        |               | nA/°C |  |  |

| I <sub>INOS</sub>     | Input offset current                                 | $I_{\rm INOS} = I_{\rm INP} - I_{\rm INN}$                |          | ±5     |               | nA    |  |  |

|                       | Input common mode rejection ratio                    | DC, AINP = AINN                                           |          | -85    |               | dB    |  |  |

| CMRRIN                | Input common-mode rejection ratio                    | f <sub>IN</sub> = 10 kHz, AINP = AINN                     |          | -85    |               |       |  |  |

|                       |                                                      | At AVDD, DC, AINP = AINN = AGND                           |          | -98    |               |       |  |  |

| PSRR                  | Power supply rejection ratio                         | At AVDD, 100-mV and 10-kHz ripple,<br>AINP = AINN = AGND  |          | -98    |               | dB    |  |  |

| BWIN                  | –3 dB input bandwidth                                |                                                           |          | 1000   |               | kHz   |  |  |

| CMTI                  | Common-mode transient immunity                       | AGND – DGND  = 1.5 kV                                     | 100      | 150    |               | kV/μs |  |  |

| MODULAT               | OR ACCURACY                                          |                                                           |          |        |               | •     |  |  |

| DNL                   | Differential nonlinearity                            | Resolution: 16 bits                                       | -0.99    |        | 0.99          | LSB   |  |  |

| INL                   | Integral nonlinearity <sup>1</sup>                   | Resolution: 16 bits                                       | -6       | ±2     | 6             | LSB   |  |  |

| Eo                    | Offset error                                         | Initial, at $T_A = 25^{\circ}C$ ,<br>AINP = AINN = AGND   | -150     | ±4.5   | 150           | μV    |  |  |

| TCEo                  | Offset drift                                         |                                                           | -3.5     | ±0.5   | 3.5           | μV/°C |  |  |

| E <sub>G</sub>        | Gain error                                           | Initial, at T <sub>A</sub> = 25°C                         | -0.3%    | ±0.05% | 0.3%          |       |  |  |

| TCEG                  | Gain drift                                           |                                                           | -40      | ±20    | 40            | ppm/° |  |  |

| SNR                   | Signal-to-noise ratio                                | f <sub>IN</sub> = 1 kHz, BW = 10 kHz                      |          | 85     |               | dB    |  |  |

| SINAD                 | Signal-to-noise-and-distortion ratio                 | f <sub>IN</sub> = 1 kHz, BW = 10 kHz                      |          | 84     |               | dB    |  |  |

| THD                   | Total harmonic distortion                            | f <sub>IN</sub> = 1 kHz, BW = 10 kHz                      |          | -93    |               | dB    |  |  |

| SFDR                  | Spurious-free dynamic range                          | f <sub>IN</sub> = 1 kHz, BW = 10 kHz                      |          | 94     |               | dB    |  |  |

#### Note:

1. The INL is defined as the maximum deviation from a straight line passing through the end-point of the ideal ADC transfer function once the gain and offset errors have been nullified and expressed as number of LSBs over the specified linear full-scale input range.

# **Electrical Characteristics (Continued)**

All minimum/maximum specs are at  $T_A = -40^{\circ}C$  to 125°C, AVDD = 4.5 V to 5.5 V, DVDD = 3.0 V to 5.5 V, AINP = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = AGND = -250 mV to 250 mV, AINN = -250 mV to 250 mV to 250 mV, AINN = -250 mV to 250 mV 0V, and sinc<sup>3</sup> filter output configured to 16 bits with OSR = 256 (unless otherwise noted). All typical values are at 25°C with CLKIN = 20 MHz, AVDD = 5 V, and DVDD = 3.3 V (unless otherwise noted).

|                                                | PARAMETER                       | TEST CONDITIONS                                            | MIN    | ТҮР  | MAX    | UNIT |

|------------------------------------------------|---------------------------------|------------------------------------------------------------|--------|------|--------|------|

| DIGITAL                                        | INPUT                           |                                                            |        |      |        |      |

| l <sub>in</sub>                                | Input current                   | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ | 0      |      | 7      | μA   |

| CIN                                            | Input capacitance               |                                                            |        | 4    |        | pF   |

|                                                |                                 |                                                            | 0.7 ×  |      | DVDD + | v    |

| V <sub>IH</sub> Logic high-level input voltage |                                 |                                                            | DVDD   |      | 0.3    | v    |

| V                                              |                                 |                                                            | 0.2    |      | 0.3 ×  | v    |

| VIL                                            | Logic low-level input voltage   |                                                            | -0.3   |      | DVDD   | v    |

| DIGITAL                                        | Ουτρυτ                          | •                                                          |        |      |        |      |

| CL                                             | Output load capacitance         |                                                            |        | 30   |        | pF   |

| V <sub>он</sub>                                | lau                             | I <sub>он</sub> = –20 µА                                   | DVDD – |      |        |      |

|                                                | Logic high-level output voltage |                                                            |        |      | V      |      |

| ∙он                                            | Logic high-level output voltage | I <sub>он</sub> = -4 mA                                    | DVDD – |      |        | v    |

|                                                |                                 | 10H4 11A                                                   | 0.4    |      |        |      |

| Vol                                            | Logic low-level output voltage  | I <sub>OL</sub> = 20 μA                                    |        |      | 0.1    | v    |

| VOL                                            | Logic low-level output voltage  | I <sub>OL</sub> = 4 mA                                     |        |      | 0.4    | v    |

| POWER S                                        | SUPPLY                          |                                                            |        |      |        |      |

| AVDD <sub>UV</sub>                             | AVDD undervoltage threshold     | AVDD rising                                                |        | 2.5  | 2.7    | V    |

| AVDD                                           | High-side supply current        | 4.5 V ≤ AVDD ≤ 5.5 V                                       |        | 11.5 | 16.5   | mA   |

|                                                | Low-side supply current         | 3.0 V ≤ DVDD ≤ 3.6 V                                       |        | 3.3  | 5.3    |      |

| DVDD                                           | with $C_L = 15 \text{ pF}^1$    | 4.5 V ≤ DVDD ≤ 5.5 V                                       |        | 4.0  | 7.0    | mA   |

| Note:                                          |                                 |                                                            |        |      |        |      |

# CA-IS1305x Version 1.03,2023/05/04

#### Shanghai Chipanalog Microelectronics Co., Ltd.

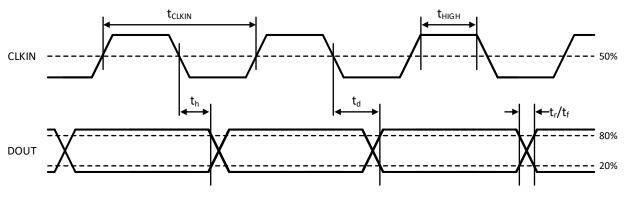

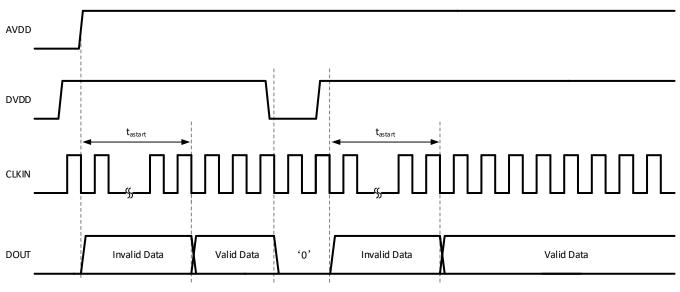

#### 7.9 Switching Characteristics

All minimum/maximum specs are at  $T_A = -40^{\circ}$ C to 125°C, AVDD = 4.5 V to 5.5 V, DVDD = 3.0 V to 5.5 V, AINP = -250 mV to 250 mV, AINN = AGND = 0V, and sinc<sup>3</sup> filter output configured to 16 bits with OSR = 256 (unless otherwise noted). All typical values are at 25°C with CLKIN = 20 MHz, AVDD = 5 V, and DVDD = 3.3 V (unless otherwise noted).

|                     | PARAMETER                                                     | TEST CONDITIONS                                          | MIN   | ТҮР | MAX   | UNIT |

|---------------------|---------------------------------------------------------------|----------------------------------------------------------|-------|-----|-------|------|

| f <sub>clkin</sub>  | CLKIN clock frequency                                         | 4.5 V ≤ AVDD ≤ 5.5 V                                     | 5     |     | 21    | MHz  |

| Duty<br>Cycle       | CLKIN clock duty cycle                                        | $t_{HIGH} / t_{CLKIN}$ , 4.5 V $\leq$ AVDD $\leq$ 5.5 V  | 42.5% | 50% | 57.5% |      |

| t <sub>h</sub>      | Hold time of DOUT after rising edge of CLKIN <sup>1</sup>     | C <sub>L</sub> = 15 pF <sup>2</sup> ; <i>See Figure</i>  | 3.5   |     |       | ns   |

| t <sub>d</sub>      | Delay time of DOUT after rising edge of<br>CLKIN <sup>1</sup> | C <sub>L</sub> = 15 pF <sup>2</sup> ; <i>See Figure</i>  |       |     | 16    | ns   |

| t <sub>r</sub>      | Rise time of DOUT (10%–90%)                                   | C <sub>L</sub> = 15 pF <sup>2</sup>                      |       | 1.8 | 5.0   | ns   |

| t <sub>f</sub>      | Fall time of DOUT (90%–10%)                                   | C <sub>L</sub> = 15 pF <sup>2</sup>                      |       | 1.8 | 5.0   | ns   |

| t <sub>astart</sub> | Analog startup time                                           | AVDD step to 4.5 V with 3.0 V $\leq$ DVDD;<br>See Figure |       | 500 |       | μs   |

### Figure 7-1. CA-IS1305x Digital Output Timing

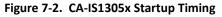

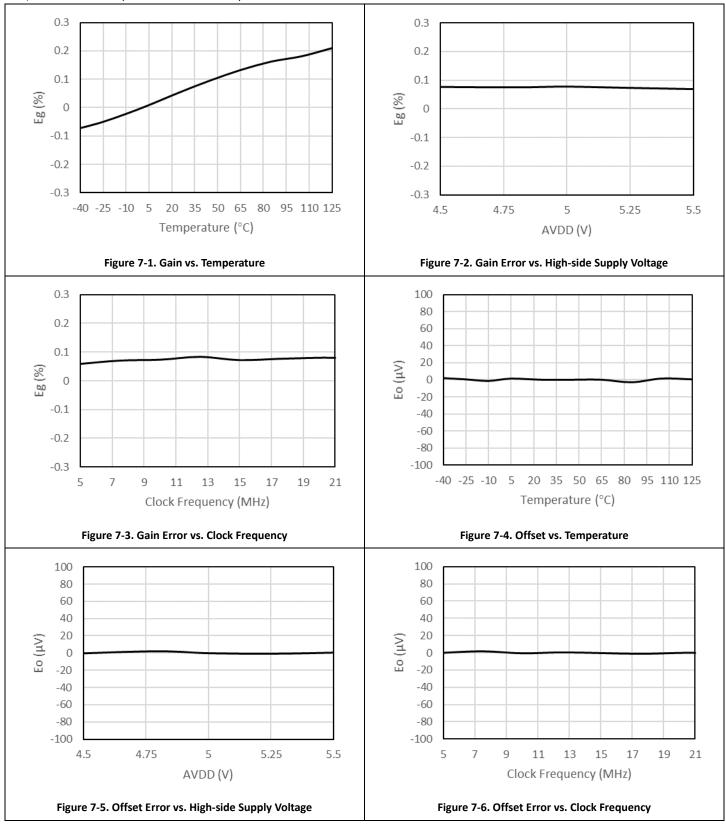

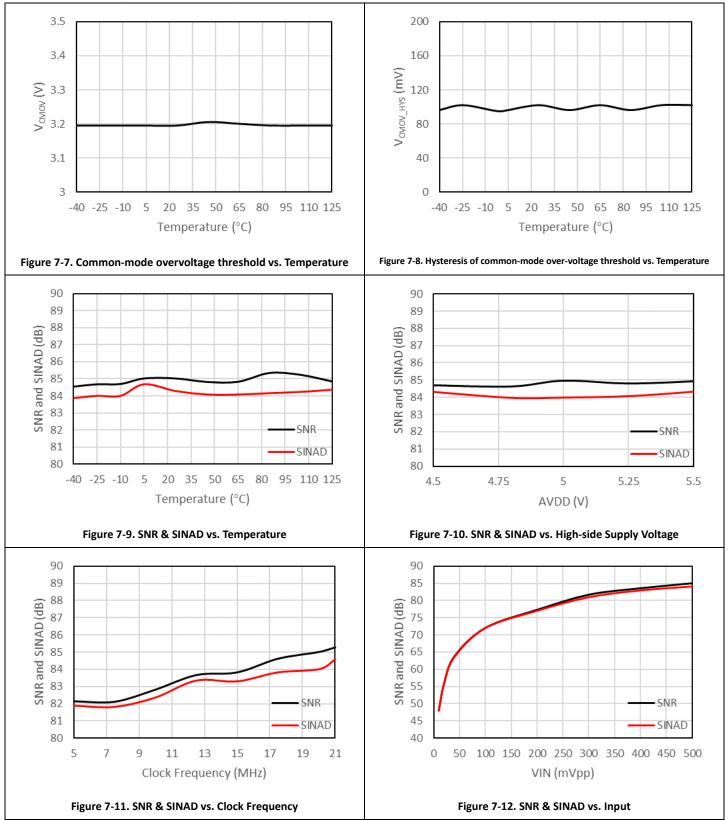

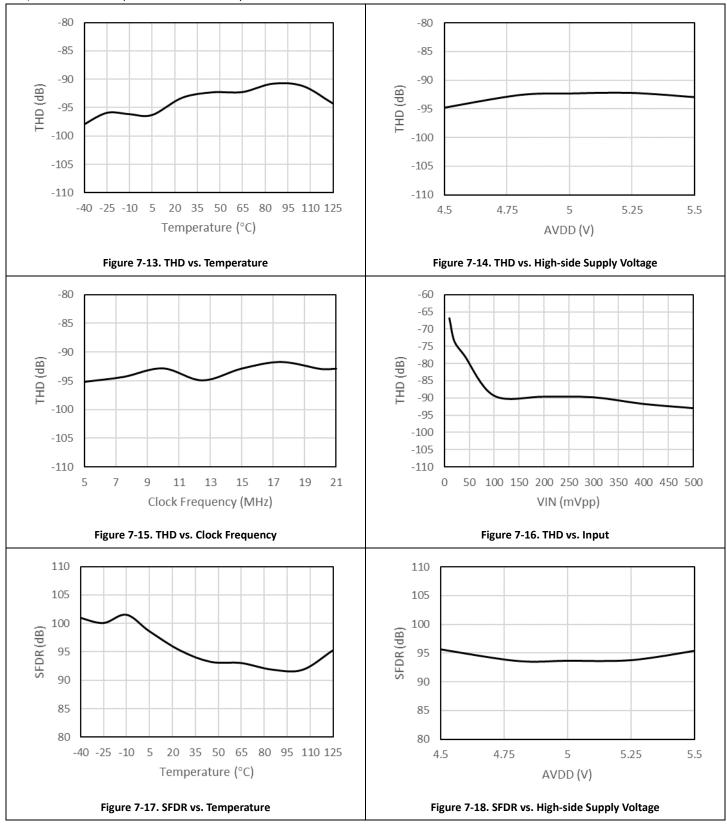

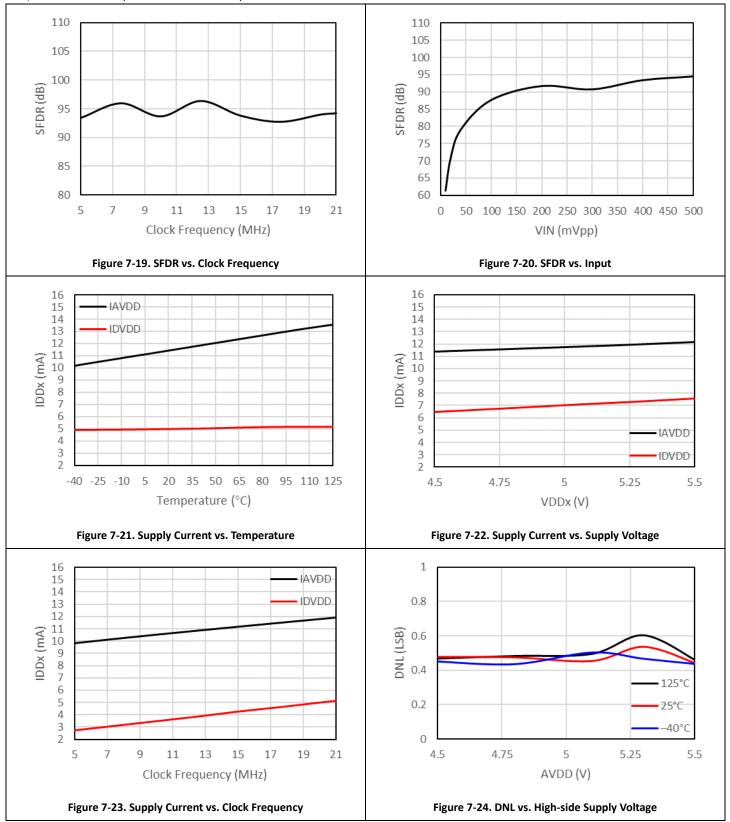

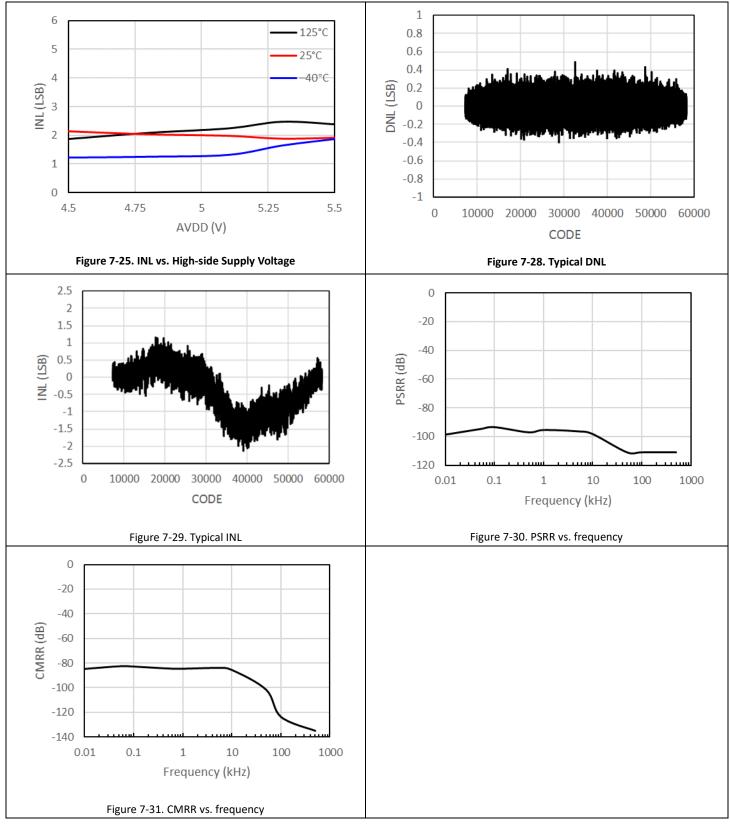

# 7.10 Typical Characteristics and Waveforms

# CA-IS1305x Version 1.03,2023/05/04

### Typical Characteristics and Waveforms (Continued)

# **Typical Characteristics and Waveforms (Continued)**

# CA-IS1305x Version 1.03,2023/05/04

### **Typical Characteristics and Waveforms (Continued)**

# Typical Characteristics and Waveforms (Continued)

# 8 Detailed Description

# 8.1 Overview

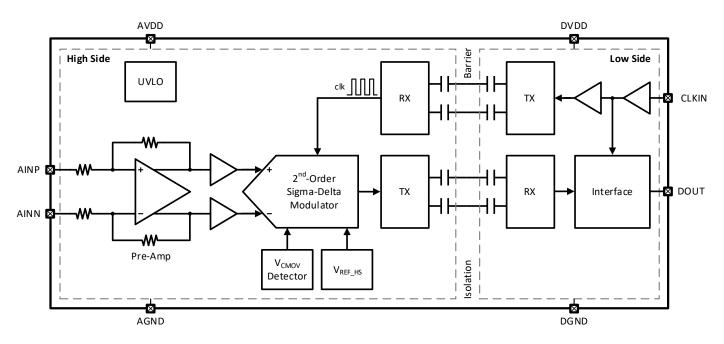

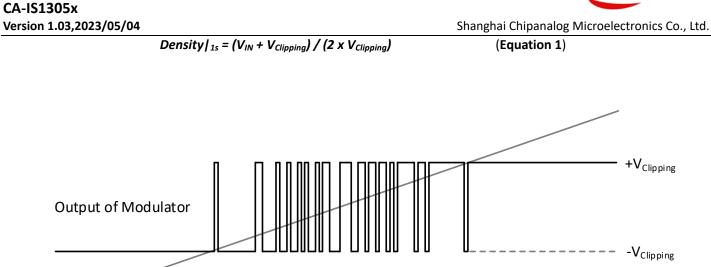

The CA-IS1305x devices are series of precision isolated sigma-delta ( $\Sigma\Delta$ ) modulators optimized for shunt resistor-based current sensing and small signal measurement applications. The functional block diagram of these devices is shown in Figure. This family of devices performs fully differential analog input to digital output conversion using a single-bit, second-order, switched-capacitor modulator. A single comparator within the modulator quantizes the input signal at a much higher sample rate than the bandwidth of the signal to be measured. The quantizer then presents a stream of 1s and 0s to the digital isolator driver and the driver transmit the bit stream across a SiO<sub>2</sub>-based capacitive isolation barrier to provide up to 5kV<sub>RMS</sub> isolation rating. The modulator is fully differential for maximum signal-to-noise ratio and minimum susceptibility to power-supply noise. On the digital output-side or low-side, the receiver demodulates the signal after advanced signal conditioning and produces the output at DOUT. The density of 1s in the DOUT bit stream output is proportional to the analog input voltage.

To synchronize the entire system operation, the device provides an external clock input CLKIN on the low-side and feeds the clock back to the high-side through digital isolation for the synchronous sigma-delta modulator operating. The input clock frequency range is from 5MHz to 21MHz, much higher than the analog input bandwidth.

Figure 8-1. Functional Block Diagram of the CA-IS1305x

# 8.2 Analog Input (High-side)

The analog input of CA-IS1305x series devices utilizes a full differential preamplifier to amplify the voltage of current sense resistor  $R_{shunt}$ . The gain of the input amplifier is fixed and set by internal precision resistors. The internal fixed gain of the CA-IS1305M25W/CA-IS1305AM25W is 4x, and the corresponding full-scale input voltage range is ±250mV, the differential input impedance is 22k $\Omega$  (see the Electrical Characteristics for more details). Considering of the lower input impedance of the CA-IS1305x devices, large gain and offset errors could be introduced when used with high-impedance signal resources. It is very important to select a reasonable current sense resistor and carefully layout the PCB.

The internal ESD protection of the CA-IS1305x can withstand (AGND–6V) to (AVDD+0.5V) absolute maximum analog input. To guarantee the long-term reliability and devices performance, the differential analog input voltage and the input common-

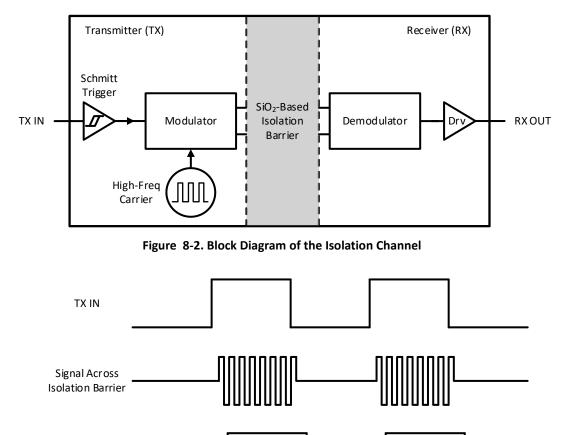

### 8.3 Signal Isolation

The CA-IS1305x family of devices utilizes Chipanalog's full differential capacitive isolation technology, as shown in Figure , that contains an ON-OFF keying (OOK) modulation scheme to transfer digital signals across the SiO<sub>2</sub> based isolation barrier between circuits with different power domains. The transmitter sends a high frequency carrier across the barrier to represent one digital state and sends no signal to represent the other digital state. The isolation receiver demodulates the signal and recovery input signal at output through a buffer stage, see Figure for more details. With this OOK architecture, the CA-IS1305x devices build a robust data transmission path between different power domains and support up to  $5kV_{RMS}$  galvanic isolation between the analog input side and digital output side.

Figure 8-3. OOK Modulation

# 8.4 Digital Output (Low-side)

#### 8.4.1 Bit stream output

The CA-IS1305x devices perform fully differential analog input to digital output conversion using a sigma-delta modulator. The sigma-delta modulator converts the input signal into a digital pulse train whose average duty cycle represents the digitized signal information. Figure shows the relationship between the bit stream output vs. analog input (AINP – AINN). The analog input of 0 V ideally produces to a digital bit-stream of "1" and "0" with high 50% of the time. For the analog input voltage within full-scale input range (±320 mV), the digital output maintains a linear relationship with the analog input, and the density of 1s in the digital output bit-stream can be calculated as following equation:

# 8.4.2 Over-range Output

Analog Input

For CA-IS1305x devices, the maximum input voltage before clipping output is  $\pm$ 320mV. If the analog input less than or equal to -320mV, the CA-IS1305x modulator will clip the bit-stream at "0", and generate a single "1" every 128 clocks; If the analog input grater than or equal to +320mV, the CA-IS1305x modulator will clip the bit-stream at "1", and generate a single "0" every 128 clocks, see Figure 8-5.

Figure 8-5. CA-IS1305x Over-range Output Waveforms

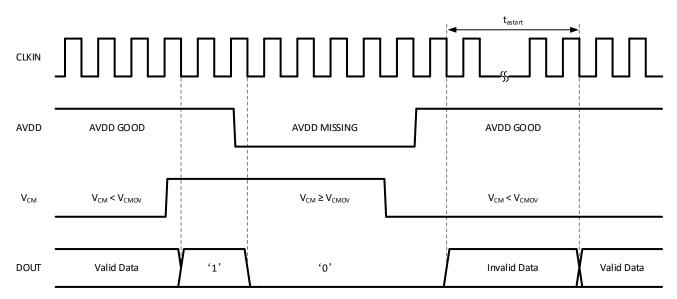

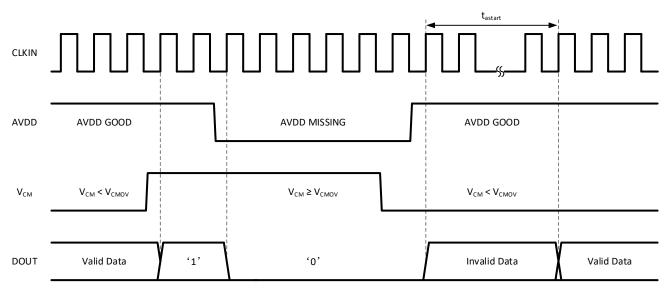

# 8.4.3 Fail-Safe Output

The CA-IS1305x devices feature fail-safe output indication which means the devices guarantee a logic-low on the digital output (DOUT) when the high-side power supply (AVDD) is off or loss, or a logic-high at DOUT when the common-mode input voltage V<sub>CM</sub> exceeds the common-mode overvoltage threshold V<sub>CMOV</sub>. When both cases occur at the same time, the priority of high side supply voltage (AVDD) loss is higher, so DOUT output will remain logic 0, see Figure 8-6 for more details. In the case of a missing high-side supply voltage AVDD, the output of  $\Sigma$ - $\Delta$  modulator is not defined and can cause a system fault or indeterminacy. The fail-safe output provides a fault indication for system and helps to improve system reliability. Also, in this way, differentiating between the AVDD loss and the over range input signal is possible on the system level.

Figure 8-6. CA-IS1305x Fail-Safe Output

# 9 Application Information

#### 9.1 Typical Application for Current Sense

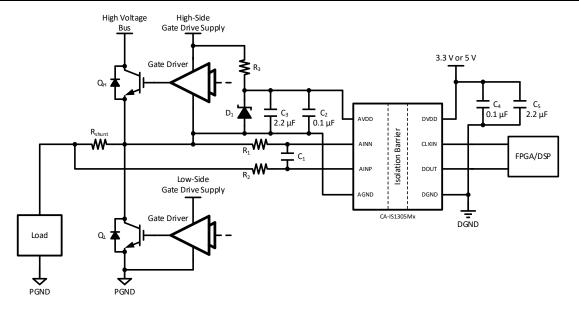

#### 9.1.1 Typical Application Circuit

The CA-IS1305x precision isolated sigma-delta ( $\Sigma$ - $\Delta$ ) modulators are optimized for shunt resistor-based current sensing applications. A typical application circuit is shown in Figure, the CA-IS1305x device is used to amplify the voltage across the shunt resistor (R<sub>shunt</sub>) with fixed gain (4x), and the internal sigma-delta modulator converts the amplified analog signal into digital bit-stream. The isolated bit stream output is then processed by an external digital decimation filter which can be implemented by FPGA or DSP, resulting in a conversion accuracy up to 16 bits. Robust isolation coupled with up to 150kV/µs typical CMTI enables accurate small signal measurement in noisy environments, making these devices ideal for motor drives, photovoltaic inverters, uninterruptible power supplies(UPS) etc. industrial applications. Figure shows the CA-IS1305x in one motor phase current sense circuit design.

Figure 9-1. Typical Application for 1-phase Current Sensing

# 9.1.2 Choosing the Current Sense Resistor

The shunt resistor selection should be a trade off between power dissipation and measurement accuracy. Small value resistors minimize power dissipation, while large value resistors take advantage of the full performance input range of the sigma-delta modulator. Choose the shunt resistor based on the following criteria:

# • Accuracy:

A high  $R_{shunt}$  value allows lower currents to be measured more accurately. This is because offsets become less significant when the sense voltage is larger. For best performance, select  $R_{shunt}$  to provide approximately  $V_{FSR}$  (±250mV) of sense voltage for the nominal full-scale current in each application. And the voltage drop at  $R_{shunt}$  caused by the maximum current should be less than  $V_{Clipping}$  (±320mV).

# • Power dissipation

At high current levels, the  $I^2R$  losses in  $R_{shunt}$  can be significant. Take this into consideration when choosing the resistor value and its power dissipation rating. Also, the sense resistor's value might drift if it is allowed to heat up excessively.

Due to the high currents that may flow through R<sub>shunt</sub>, take care to eliminate solder and parasitic trace resistance from causing errors in the sense voltage. Either use a four-terminal current sense resistor or use Kelvin (force and sense) PCB layout technique. The Kelvin-sense traces should be as close as possible to the current-sense resistor's solder contact pads. If the Kelvin-sensing contact pads are spaced wider relative to the sense resistor, error is introduced from the additional trace resistance.

# 9.1.3 Analog Input Filter

To improve signal-to-noise performance of the CA-IS1305x's signal path, an external 1<sup>st</sup>-order RC filter is recommended in front of the amplifier, as shown in the typical application circuit, selecting  $R_1 = R_2 = 10\Omega$  and  $C_1 = 20$ nF, the input bandwidth of the analog front-end of the device can be limited within 400kHz.

# 9.1.4 Digital Output Filter

The CA-IS1305x modulator provides 2<sup>nd</sup>-order frequency shaping of the quantization noise resulting from the single bit quantizer. To remove the frequency shaped quantization noise, a digital decimation filter is required. For the CA-IS1305x 2<sup>nd</sup>

order modulator circuit design, a sinc<sup>3</sup> filter is recommended because of the low cost hardware design and better performance. A FPGA or DSP can be used to implement this filter to provide the transfer function of a sinc<sup>3</sup> filter as below.

$$H(Z) = \left[\frac{1}{DR} \frac{(1 - Z^{-DR})}{(1 - Z^{-1})}\right]^{3}$$

(Equation 2)

Where DR is the decimation rate, it is the ratio of modulator clock frequency  $f_{CLKIN}$  and throughput rate of the sinc<sup>3</sup> filter  $f_{DATA}$ , which is also called oversampling rate (OSR).

$$DR = OSR = f_{CLKIN}/f_{DATA}$$

(Equation 3)

The output data width is shown in below equation.

(Equation 4)

All of the characterization in section of Electrical Characteristics is done with a sinc<sup>3</sup> filter with an oversampling ratio(OSR) of 256 and an output word width of 16 bits.

The characteristics of the sinc<sup>3</sup> filter are summarized in Table 9-1. As the decimation rate increased, the output data width from sinc<sup>3</sup> filter increased as well, while the throughput rate decreased, resulting higher SNR performance. Thus, designers can trade off between data rate and conversion accuracy based on the application requirements.

| Decimation Rate (DR) | f <sub>DATA</sub> (kHz) | Output Data Width (Bits) | Filter Response (kHz) |

|----------------------|-------------------------|--------------------------|-----------------------|

| 32                   | 625                     | 15                       | 163.7                 |

| 64                   | 312.5                   | 18                       | 81.8                  |

| 128                  | 156.2                   | 21                       | 40.9                  |

| 256                  | 78.1                    | 24                       | 20.4                  |

| 512                  | 39.1                    | 27                       | 10.2                  |

Table 9-1. Characteristics of sinc<sup>3</sup> Filter at 20MHz f<sub>CLKIN</sub>

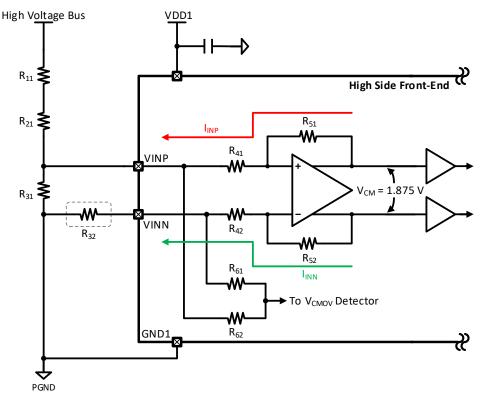

#### 9.2 Voltage Measurement

The CA-IS1305x current sense amplifiers, along with a voltage divider, can be used as an isolated voltage measurement solution, see Figure 9-2 typical application circuit. The resistors of R<sub>41</sub>, R<sub>42</sub>, R<sub>51</sub>, R<sub>52</sub>, R<sub>61</sub> and R<sub>62</sub> are the internal resistors of the CA-IS1305x device, where R<sub>41</sub>, R<sub>42</sub>, R<sub>51</sub>, and R<sub>52</sub> are used to setup the amplifier gain, R<sub>41</sub> = R<sub>42</sub> = 12.5 k $\Omega$ , R<sub>51</sub> = R<sub>52</sub> = 50 k $\Omega$ ; R61 and R62 are the common-mode voltage detector, R<sub>61</sub> = R<sub>62</sub> = 100 k $\Omega$ . The voltage-divider (R<sub>21</sub>+R<sub>11</sub> and R<sub>31</sub>) reduces the input voltage from the power supply bus voltage to ±250mV to match the input range of the CA-IS1305x. Thus, for the high-voltage power supply bus, (R<sub>21</sub>+R<sub>11</sub>) >> R<sub>31</sub>.

Also, the bias current  $I_{INP}$  caused by  $V_{CM}$  (1.875V, typ.) passing through the voltage sense resistor  $R_{31}$  will cause significant offset error as well. To reduce the gain error and offset error, select  $R_{31}$  as small as possible. However, to limit the current consumption of the voltage-divider, choosing large resistance values for  $R_{21}+R_{11}$  and  $R_{31}$  will minimize overall power consumption. Designers need to balance the choice of divider resistance.

In order to cancel out the offset error introduced by the bias current  $I_{INP}$  flowing through  $R_{31}$ , the resistor  $R_{32}$  is added at VINN input. As the error compensating resistor, the ideal  $R_{32}$  should be the parallel resistance of  $(R_{21}+R_{11})/(R_{31})$ , see below  $R_{32}$

calculation equation,

$$R_{32} = \frac{R_{31}x(R_{21} + R_{11})}{R_{31} + R_{21} + R_{11}} \cong R_{31}, \ (R_{11} + R_{21} \gg R_{31})$$

Adding  $R_{32}$  can remove the offset error caused by  $I_{INP}$ , but there will be an expected difference between the modulator's differential input voltage (AINP – AINN) and the voltage drop on  $R_{31}$  given by the resistor divider. This discrepancy can be expressed as a gain error, as shown in below equation,

$$G_{ERROR} = \frac{R_{31}}{R_{31} + R_{41}}$$

Choosing appropriate R<sub>31</sub> to balance gain error and power consumption, combine with offset compensating resistor R<sub>32</sub>, the voltage measurement performance shown in Figure 9-2 typical application circuit is acceptable for most applications.

Figure 9-2. Typical Application Circuit for Voltage-Measurement

# 9.3 Power supply and PCB layout

The CA-IS1305x devices require dual power supply to provide supply for analog input-side and digital output-side in the different voltage domain. The supply range of AVDD is 4.5V to 5.5V; for DVDD, the supply range is 3.0V to 5.5V. To reduce system-level cost, the power supply of AVDD can be derived from the system main power supply by using a Zener diode( $D_1$  in Figure 9-1) to limit the voltage to 5V (±10%). Alternatively a low-cost low-drop regulator (LDO) can be used to produce a stable supply voltage level for AVDD and minimize noise on the power-supply as well.

Good layout technique optimizes performance by decreasing the amount of stray capacitance at the high-side, current-

# CA-IS1305x Version 1.03,2023/05/04

sense-amplifier, common-mode inputs etc. Capacitive decoupling across the supply voltage AVDD to AGND(C<sub>2</sub>), DVDD to DGND(C<sub>4</sub>) of low-ESR  $0.1\mu$ F is recommended as shown in Figure 9-1. If better filtering is required, an extra bulk capacitor (2.2 $\mu$ F to 10 $\mu$ F) can be added(C<sub>3</sub>, C<sub>5</sub>). Since the CA-IS1305x devices feature ultra-low input offset voltage, board leakage and thermocouple effects can easily introduce errors in the input offset voltage readings when used with high-impedance signal sources. In order to dissipate sense-resistor heat from large sense currents, solder the AINP and the AINN pins to large copper traces. Keep the part away from other heat-generating devices. For accurate measurement of V<sub>shunt</sub>, the Kelvin method is recommended. For noisy digital environments, keep digital signals far away from the sensitive analog inputs. The use of a multilayer PCB with separate ground and power-supply planes is recommended.

CA-IS1305x Version 1.03,2023/05/04

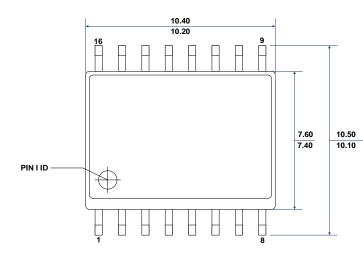

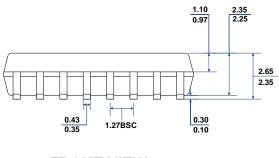

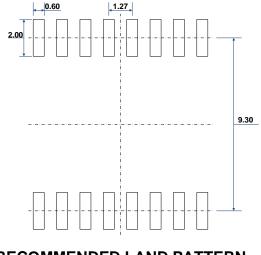

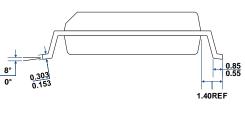

10 Package Information

16-Pin Wide Body SOIC Package

**TOP VIEW**

FRONT VIEW

# **RECOMMENDED LAND PATTERN**

**LEFT-SIDE VIEW**

Note: All dimensions are shown in millimeters.

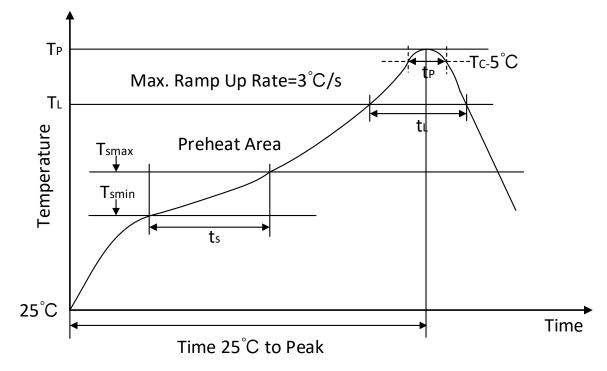

# 11 Soldering Temperature (reflow) Profile

| Figure 11-1. Soldering Tempera | ature (reflow) Profile |

|--------------------------------|------------------------|

|--------------------------------|------------------------|

| Profile Feature                              | Pb-Free Assembly  |

|----------------------------------------------|-------------------|

| Average ramp-up rate(217 °C to Peak)         | 3°C /second max   |

| Time of Preheat temp(from 150 °C to 200 °C ) | 60-120 second     |

| Time to be maintained above 217 °C           | 60-150 second     |

| Peak temperature                             | 260 +5/-0 °C      |

| Time within 5 °C of actual peak temp         | 30 second         |

| Ramp-down rate                               | 6 °C /second max. |

| Time from 25°C to peak temperature           | 8 minutes max     |

# 12 Tape and Reel Information

Version 1.03,2023/05/04

CA-IS1305x

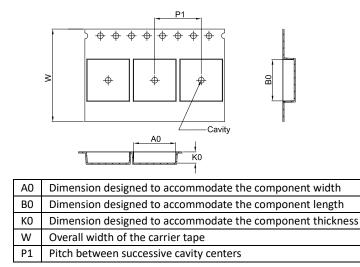

TAPE DIMENSIONS

Shanghai Chipanalog Microelectronics Co., Ltd.

OG

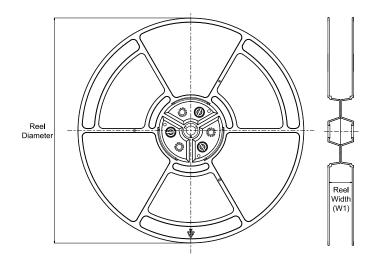

**REEL DIMENSIONS**

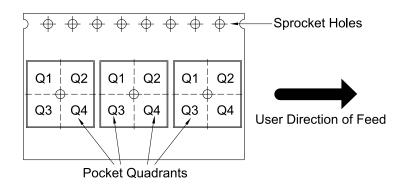

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IS1305M25W  | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.8       | 10.7       | 2.9        | 12.0       | 24.0      | Q1               |

| CA-IS1305AM25W | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.8       | 10.7       | 2.9        | 12.0       | 24.0      | Q1               |

## 13 Important Notice

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

#### **Trademark Information**

Chipanalog Inc.<sup>®</sup>, Chipanalog<sup>®</sup> are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com