## 21 W $\times$ 4-Channel BTL Power IC

# HITACHI

ADE-207-107 1st. Edition

#### Description

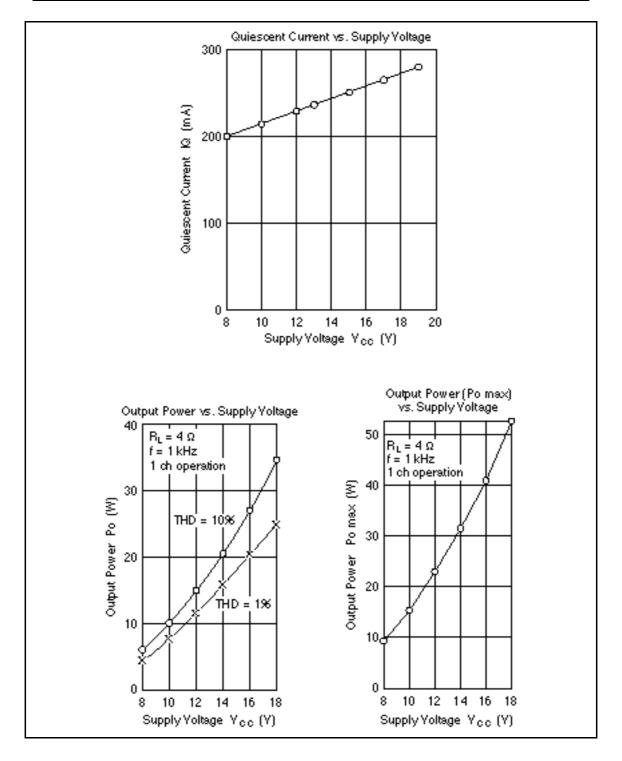

HA13150A is a four-channel BTL amplifier IC designed for car audio, featuring high output and low distortion, and applicable to digital audio equipment. It provides 21 W output per channel, with a 14.4 V power supply and at 10% distortion.

#### Functions

- Built-in standby circuit

- Built-in muting circuit

- Built-in protection circuits (surge, TSD, and ASO)

#### Features

- Requires few external parts

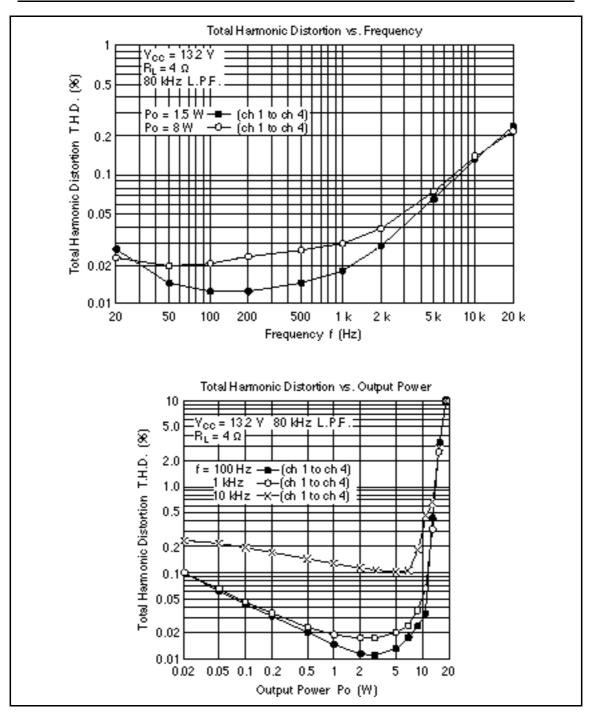

- Low distortion (total harmonic distortion = 0.01% at 3 W)

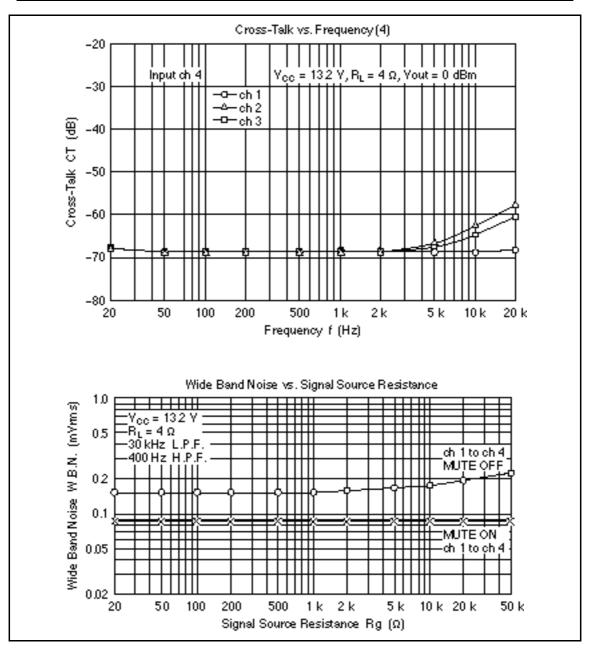

- Low noise (at Rg = 620 , noise is 0.15 mV (muting off) or 0.1 mV (muting on))

- Popping noise minimized

- Highly reliable current-limiting ASO protector keeps speakers safe from all kinds of trouble. Reliability is further enhanced by a fast-acting thermal shutdown protection circuit with on/off hysteresis.

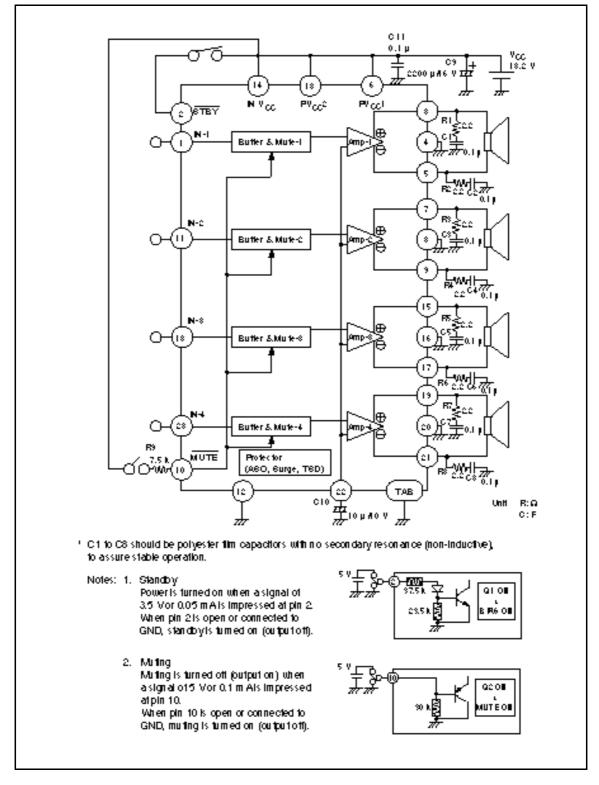

#### **Block Diagram**

#### **Absolute Maximum Ratings** ( $Ta = 25^{\circ}C$ )

| Item | Symbol | Rating | Unit | Remarks |

|------|--------|--------|------|---------|

|      |        |        |      |         |

| Operating supply voltage         | V <sub>cc</sub>        | 18          | V  |

|----------------------------------|------------------------|-------------|----|

| Supply voltage when no signal *1 | V <sub>cc</sub> (DC)   | 26          | V  |

| Peak supply voltage *2           | V <sub>cc</sub> (PEAK) | 50          | V  |

| Output current *3                | I <sub>o</sub> (PEAK)  | 4           | A  |

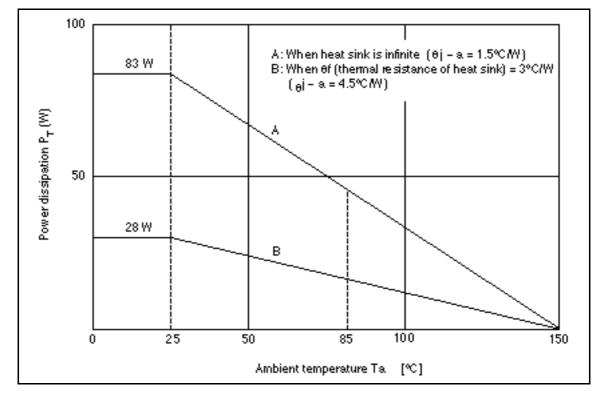

| Power dissipation *4             | P <sub>T</sub>         | 83          | W  |

| Junction temperature             | Тј                     | 150         | °C |

| Operating temperature            | Topr                   | -30 to +85  | °C |

| Storage temperature              | Tstg                   | –55 to +125 | °C |

Notes: 1. Tolerance within 30 seconds

- 2. Tolerance in surge pulse waveform

- 3. Value per 1 channel

4. Value when attached on the infinite heat sink plate at  $Ta = 25^{\circ}C$ .

The derating carve is as shown in the graph below.

Electrical Characteristics (V $_{\rm CC}$  = 13.2 V, f = 1 kHz,  $R_{\rm L}$  = 4  $\,$  , Rg = 620  $\,$  , Ta = 25°C)

| Item                             | Symbol           | Min  | Тур  | Мах             | Unit  | Test Conditions                              |

|----------------------------------|------------------|------|------|-----------------|-------|----------------------------------------------|

| Current when no signal           | lq1              | _    | 240  |                 | mA    | Vin = 0                                      |

| Output offset voltage            | Vq               | -250 | 0    | +250            | mV    |                                              |

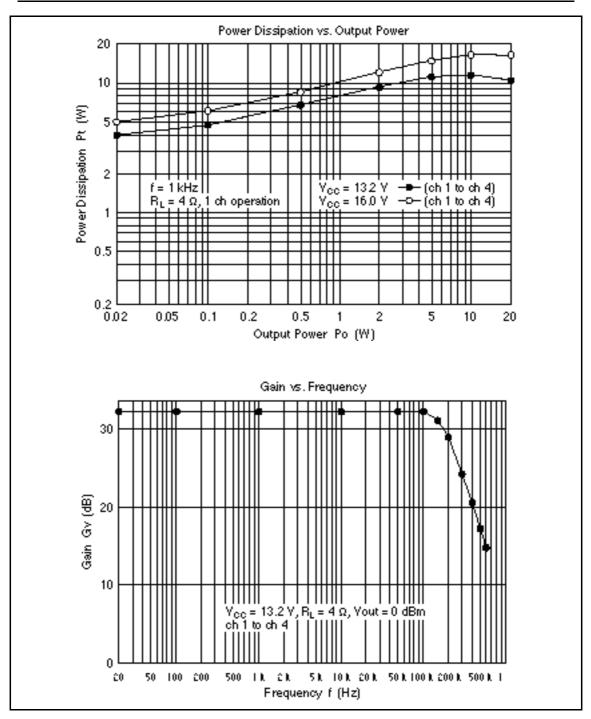

| Gain                             | Gv               | 30.5 | 32   | 33.5            | dB    |                                              |

| Gain difference between channels | Gv               | -1.5 | 0    | +1.5            | dB    |                                              |

| Rated output power               | Po               | —    | 18   | —               | W     | $V_{cc} = 13.2 V$<br>$R_{L} = 4$ , THD = 10% |

| Max output power                 | Pomax            | —    | 30   | —               |       | $V_{cc} = 13.7 V$<br>$R_L = 4$ , THD = Max   |

| Total harmonic distortion        | T.H.D            | _    | 0.01 |                 | %     | Po = 3 W                                     |

| Output noise voltage             | WBN              | —    | 0.15 | 0.5             | mVrms | Rg = 0<br>BW = 20 to 20 kHz                  |

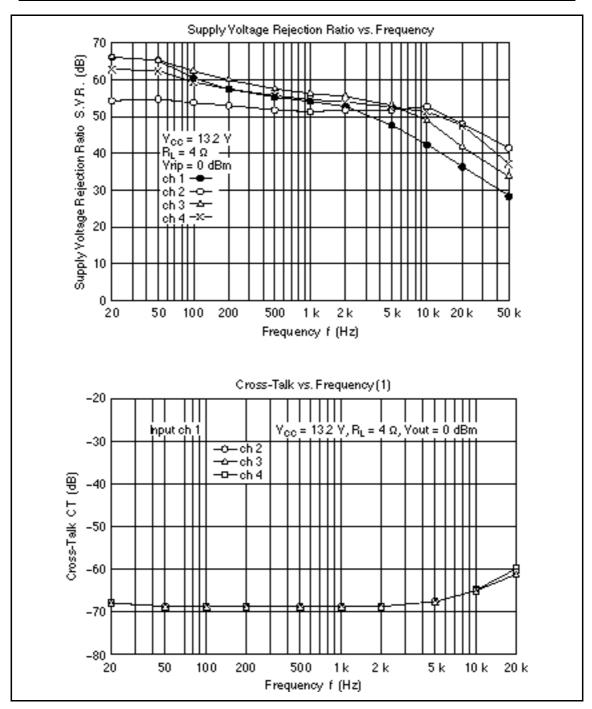

| Ripple rejection                 | SVR              | —    | 55   | —               | dB    | Rg = 600<br>f = 120 Hz                       |

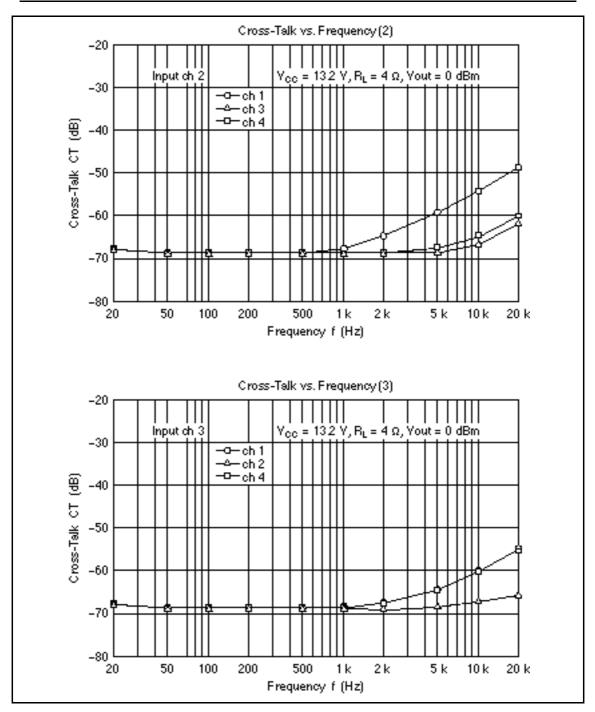

| Channel crosstalk                | C.T              | —    | 70   | —               | dB    | Rg = 600<br>Vout = 0 dBm                     |

| Input impedance                  | Rin              | _    | 25   | _               | k     |                                              |

| Standby current                  | lq2              | _    | _    | 200             | μA    |                                              |

| Standby control voltage (high)   | $V_{\rm STH}$    | 3.5  | —    | V <sub>cc</sub> | V     |                                              |

| Standby control voltage (low)    | $V_{\rm STL}$    | 0    | —    | 1.5             | V     |                                              |

| Muting control voltage (high)    | V <sub>MH</sub>  | 3.5  |      | V <sub>cc</sub> | V     |                                              |

| Muting control voltage (low)     | V <sub>ML</sub>  | 0    |      | 1.5             | V     |                                              |

| Muting attenuation               | A <sub>TTM</sub> | _    | 70   |                 | dB    | Vout = 0 dBm                                 |

| Pin<br>No. | Symbol   | Functions       | Input<br>Impedance       | DC<br>Voltage      | Equivalence Circuit |

|------------|----------|-----------------|--------------------------|--------------------|---------------------|

| 1          | IN1      | CH1 INPUT       | 25 k (Typ)               | 0 V                |                     |

| 11         | IN2      | CH2 INPUT       |                          |                    |                     |

| 13         | IN3      | CH3 INPUT       |                          |                    |                     |

| 23         | IN4      | CH4 INPUT       |                          |                    |                     |

| 2          | STBY     | Standby control | 90 k<br>(at Trs. cutoff) | _                  | 23.5 k              |

| 3          | OUT1 (+) | CH1 OUTPUT      | _                        | V <sub>cc</sub> /2 |                     |

| 5          | OUT1 (–) | _               |                          |                    |                     |

| 7          | OUT2 (+) | CH2 OUTPUT      |                          |                    |                     |

| 9          | OUT2 (–) |                 |                          |                    |                     |

| 15         | OUT3 (+) | CH3 OUTPUT      |                          |                    |                     |

| 17         | OUT3 (–) |                 |                          |                    |                     |

| 19         | OUT4 (+) | CH4 OUTPUT      |                          |                    |                     |

| 21         | OUT4 (–) |                 |                          |                    |                     |

| 10         | MUTE     | Muting control  | 25 k (Typ)               | _                  | 10 <b>+ k</b>       |

## Pin Explanation

## Pin Explanation (cont)

| Pin<br>No. | Symbol             | Functions             | Input<br>Impedance | DC<br>Voltage      | Equivalence Circuit |

|------------|--------------------|-----------------------|--------------------|--------------------|---------------------|

| 22         | RIPPLE             | Bias stability        | _                  | V <sub>cc</sub> /2 |                     |

| 6          | PV <sub>cc</sub> 1 | Power of output stage |                    | V <sub>cc</sub>    | _                   |

| 18         | PV <sub>cc</sub> 2 |                       |                    |                    |                     |

| 14         | $INV_{cc}$         | Power of input stage  |                    | V <sub>cc</sub>    | _                   |

| 4          | CH1 GND            | CH1 power GND         | —                  | _                  | _                   |

| 8          | CH2 GND            | CH2 power GND         | -                  |                    |                     |

| 16         | CH3 GND            | CH3 power GND         | _                  |                    |                     |

| 20         | CH4 GND            | CH4 power GND         | -                  |                    |                     |

| 12         | IN GND             | Input signal GND      |                    |                    | _                   |

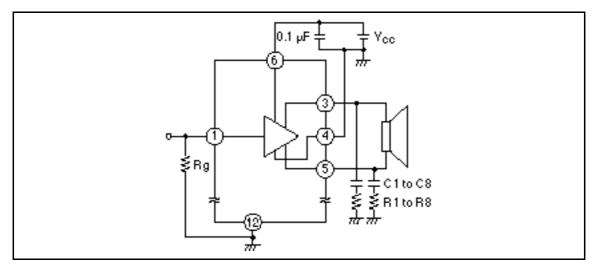

#### **Point of Application Board Design**

- 1. Notes on Application board's pattern design

- For increasing stability, the connected line of  $V_{CC}$  and OUTGND is better to be made wider and lower impedance.

- For increasing stability, it is better to place the capacitor between  $V_{CC}$  and GND (0.1  $\mu F)$  close to IC.

- For increasing stability, it is better to place C1 to C8 and R1 to R8, which are for stopping oscillation, close to IC.

- It is better to place the grounding of resistor (Rg), between input line and ground, close to INGND (Pin 12) because if OUTGND is connected to the line between Rg and INGND, THD will become worse due to current from OUTGND.

Figure 1 Notes on Application Board's Pattern Design

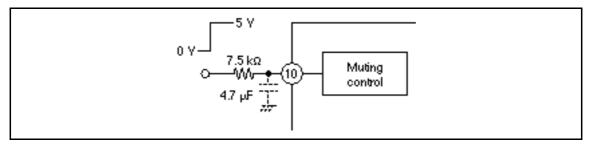

2. How to reduce the popping noise by Muting circuit

At normal operating circuit, Muting circuit operates at high speed under 1 µs.

In case popping noise becomes a problem, it is possible to reduce the popping noise by connecting capacitor, which determines the switching time constant, between pin 10 and GND. (Following figure 2)

We recommend value of capacitor greater then 1  $\mu F.$

Also transitional popping noise can be reduced sharply by muting before  $V_{CC}$  and Standby are ON/OFF.

Figure 2 How to use Muting Circuit

#### Table 1Muting ON/OFF Time

| C (µF)  | ON Time    | OFF Time   |

|---------|------------|------------|

| nothing | under 1 µs | under 1 µs |

| 0.47    | 2 ms       | 2 ms       |

| 4.7     | 19 ms      | 19 ms      |

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## HITACHI

Hitachi, Ltd. Semiconductor 4. IC DV. Nepon Bidg, 2-5-2, Ohte-mach, Chiyoda-ku, Tokyo 100, Japan Tet Tokyo (03, 3270-2111 Fax (03, 3270-5109

For Auther in forms Ion write to : Hischi America, Ud Semiconductor & IC DW. 2000 Sierre Point Perlavey Briebene, CA. 94005-4835 U S.Å Tet 415-583-8300 Fax 415-583-4207

Hitschi Burope GmbH Bedronic Components Group Cartinertal Burope Danscher Straße 3 D-85522 Fieldkirchen Minchen Tet 083-9 94 80-0 Fex 083-9 29 30 00 Hitschi Burope Ltd. Bedronie Components Div. Nothern Burope Hesologuerters Whitebrook Perk Lower Cook hem Roed Neidenheed Berkshire SL6SYA Urited Kingdom Tet 0625-535000 Fer: 0625-778322 Hitschi Asia Pte. Ltd 45 Collyer Quey \$20-00 Hitschi Tower Singspore 0404 Tet 535-2400 Fex: 535-4533

Hitschi Asia (Hong Kong) Ltd. Unit 705, North Towar, World Finance Cantre, Herbour City, Carton Road Taim Sha Tau, Kowloon Hong Kong Tet 27350218 Fax: 27306074

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.