## Features

- Utilizes the AVR<sup>®</sup> RISC Architecture

- AVR High-performance and Low-power RISC Architecture

- 120 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 20 MIPS Throughput at 20 MHz

- Data and Non-volatile Program and Data Memories

- 2K Bytes of In-System Self Programmable Flash Endurance 10,000 Write/Erase Cycles

- 128 Bytes In-System Programmable EEPROM Endurance: 100,000 Write/Erase Cycles

- 128 Bytes Internal SRAM

- Programming Lock for Flash Program and EEPROM Data Security

- Peripheral Features

- One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare and Capture Modes

- Four PWM Channels

- On-chip Analog Comparator

- Programmable Watchdog Timer with On-chip Oscillator

- USI Universal Serial Interface

- Full Duplex USART

- Special Microcontroller Features

- debugWIRE On-chip Debugging

- In-System Programmable via SPI Port

- External and Internal Interrupt Sources

- Low-power Idle, Power-down, and Standby Modes

- Enhanced Power-on Reset Circuit

- Programmable Brown-out Detection Circuit

- Internal Calibrated Oscillator

- I/O and Packages

- 18 Programmable I/O Lines

- 20-pin PDIP, 20-pin SOIC, 20-pad QFN/MLF

- Operating Voltages

- 1.8 5.5V (ATtiny2313V)

- 2.7 5.5V (ATtiny2313)

- Speed Grades

- ATtiny2313V: 0 4 MHz @ 1.8 5.5V, 0 10 MHz @ 2.7 5.5V

- ATtiny2313: 0 10 MHz @ 2.7 5.5V, 0 20 MHz @ 4.5 5.5V

- Typical Power Consumption

- Active Mode

- 1 MHz, 1.8V: 230 µA

- 32 kHz, 1.8V: 20 µA (including oscillator)

- Power-down Mode

- < 0.1 µA at 1.8V

8-bit **AVR**<sup>®</sup> Microcontroller with 2K Bytes In-System Programmable Flash

ATtiny2313/V

Preliminary Summary

Rev. 2543HS-AVR-02/05

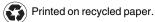

Figure 1. Pinout ATtiny2313

### **Pin Configurations**

NOTE: Bottom pad should be soldered to ground.

#### **Overview**

The ATtiny2313 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny2313 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

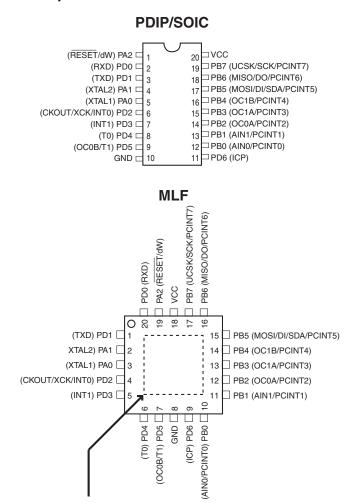

#### **Block Diagram**

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATtiny2313 provides the following features: 2K bytes of In-System Programmable Flash, 128 bytes EEPROM, 128 bytes SRAM, 18 general purpose I/O lines, 32 general purpose working registers, a single-wire Interface for On-chip Debugging, two flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, Universal Serial Interface with Start Condition Detector, a programmable Watchdog Timer with internal Oscillator, and three software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, or by a conventional non-volatile memory programmer. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATtiny2313 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATtiny2313 AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.

# **Pin Descriptions**

| VCC             | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Port A (PA2PA0) | Port A is a 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.  |

|                 | Port A also serves the functions of various special features of the ATtiny2313 as listed on page 52.                                                                                                                                                                                                                                                                                                                                      |

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                 | Port B also serves the functions of various special features of the ATtiny2313 as listed on page 52.                                                                                                                                                                                                                                                                                                                                      |

| Port D (PD6PD0) | Port D is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.  |

|                 | Port D also serves the functions of various special features of the ATtiny2313 as listed on page 55.                                                                                                                                                                                                                                                                                                                                      |

| RESET           | Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a reset, even if the clock is not running. The minimum pulse length is given in Table<br>15 on page 33. Shorter pulses are not guaranteed to generate a reset. The Reset Input<br>is an alternate function for PA2 and dW.                                                                                                               |

| XTAL1           | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. XTAL1 is an alternate function for PA0.                                                                                                                                                                                                                                                                                                    |

| XTAL2           | Output from the inverting Oscillator amplifier. XTAL2 is an alternate function for PA1.                                                                                                                                                                                                                                                                                                                                                   |

# **Register Summary**

| Address                    | Name             | Bit 7            | Bit 6            | Bit 5            | Bit 4               | Bit 3              | Bit 2          | Bit 1             | Bit 0          | Page       |

|----------------------------|------------------|------------------|------------------|------------------|---------------------|--------------------|----------------|-------------------|----------------|------------|

| 0x3F (0x5F)                | SREG             | 1                | т                | н                | S                   | v                  | N              | Z                 | С              | 7          |

| 0x3E (0x5E)                | Reserved         | -                | -                | -                | -                   | -                  | -              | -                 | _              |            |

| 0x3D (0x5D)                | SPL              | SP7              | SP6              | SP5              | SP4                 | SP3                | SP2            | SP1               | SP0            | 10         |

| 0x3C (0x5C)                | OCR0B            |                  | •                |                  | -<br>Timer/Counter0 | Compare Registe    | er B           | •                 |                | 77         |

| 0x3B (0x5B)                | GIMSK            | INT1             | INT0             | PCIE             | -                   | _                  | -              | -                 | -              | 59         |

| 0x3A (0x5A)                | EIFR             | INTF1            | INTF0            | PCIF             | -                   | -                  | -              | -                 | -              | 61         |

| 0x39 (0x59)                | TIMSK            | TOIE1            | OCIE1A           | OCIE1B           | -                   | ICIE1              | OCIE0B         | TOIE0             | OCIE0A         | 78, 109    |

| 0x38 (0x58)                | TIFR             | TOV1             | OCF1A            | OCF1B            | -                   | ICF1               | OCF0B          | TOV0              | OCF0A          | 78         |

| 0x37 (0x57)                | SPMCSR           | -                | -                | -                | CTPB                | RFLB               | PGWRT          | PGERS             | SELFPRGEN      | 155        |

| 0x36 (0x56)                | OCR0A            |                  | 1                |                  |                     | Compare Registe    |                | 1                 | -              | 77         |

| 0x35 (0x55)                | MCUCR            | PUD              | SM1              | SE               | SM0                 | ISC11              | ISC10          | ISC01             | ISC00          | 52         |

| 0x34 (0x54)                | MCUSR            | -                | -                | -                | -                   | WDRF               | BORF           | EXTRF             | PORF           | 36         |

| 0x33 (0x53)                | TCCR0B           | FOC0A            | FOC0B            | -                | -                   | WGM02              | CS02           | CS01              | CS00           | 76         |

| 0x32 (0x52)                | TCNT0            |                  |                  | 0.115            |                     | unter0 (8-bit)     |                | 0.114             |                | 77         |

| 0x31 (0x51)                | OSCCAL           | -                | CAL6             | CAL5             | CAL4                | CAL3               | CAL2           | CAL1              | CALO           | 25         |

| 0x30 (0x50)                | TCCR0A<br>TCCR1A | COM0A1<br>COM1A1 | COM0A0<br>COM1A0 | COM0B1<br>COM1B1 | COM0B0<br>COM1BO    | -                  | -              | WGM01<br>WGM11    | WGM00<br>WGM10 | 73         |

| 0x2F (0x4F)<br>0x2E (0x4E) | TCCR18           | ICNC1            | ICES1            | -                | WGM13               | -<br>WGM12         | <br>CS12       | CS11              | CS10           | 104<br>107 |

| 0x2E (0x4E)<br>0x2D (0x4D) | TCNT1H           | 101101           | 102.01           |                  |                     | unter Register Hig |                | 0311              | 0010           | 107        |

| 0x2D (0x4D)<br>0x2C (0x4C) | TCNT1L           |                  |                  |                  |                     | unter Register Lo  |                |                   |                | 108        |

| 0x2B (0x4B)                | OCR1AH           |                  |                  |                  |                     | pare Register A H  |                |                   |                | 108        |

| 0x2A (0x4A)                | OCR1AL           |                  |                  |                  |                     | pare Register A L  | <i>,</i> ,     |                   |                | 108        |

| 0x29 (0x49)                | OCR1BH           |                  |                  |                  |                     | pare Register B F  |                |                   |                | 109        |

| 0x28 (0x48)                | OCR1BL           |                  |                  |                  |                     | pare Register B L  |                |                   |                | 109        |

| 0x27 (0x47)                | Reserved         | -                | -                | -                | -                   | _                  | -              | -                 | -              |            |

| 0x26 (0x46)                | CLKPR            | CLKPCE           | -                | -                | _                   | CLKPS3             | CLKPS2         | CLKPS1            | CLKPS0         | 27         |

| 0x25 (0x45)                | ICR1H            |                  |                  | Timer/           | Counter1 - Input (  | Capture Register   | High Byte      |                   |                | 109        |

| 0x24 (0x44)                | ICR1L            |                  | _                | Timer/           | Counter1 - Input    | Capture Register   | Low Byte       | _                 |                | 109        |

| 0x23 (0x43)                | GTCCR            | -                | -                | -                | -                   | -                  | -              | -                 | PSR10          | 81         |

| 0x22 (ox42)                | TCCR1C           | FOC1A            | FOC1B            | -                | -                   | -                  | -              | -                 | -              | 108        |

| 0x21 (0x41)                | WDTCSR           | WDIF             | WDIE             | WDP3             | WDCE                | WDE                | WDP2           | WDP1              | WDP0           | 41         |

| 0x20 (0x40)                | PCMSK            | PCINT7           | PCINT6           | PCINT5           | PCINT4              | PCINT3             | PCINT2         | PCINT1            | PCINT0         | 61         |

| 0x1F (0x3F)                | Reserved         | -                | -                | -                | -                   | -                  | -              | -                 | -              |            |

| 0x1E (0x3E)                | EEAR             | -                |                  |                  |                     | ROM Address R      | egister        |                   |                | 15         |

| 0x1D (0x3D)                | EEDR             |                  |                  | 55044            |                     | Data Register      | FEMDE          | FERE              | FERE           | 16         |

| 0x1C (0x3C)                | EECR             | -                | -                | EEPM1            | EEPM0               | EERIE<br>–         | EEMPE          | EEPE              | EERE           | 16         |

| 0x1B (0x3B)<br>0x1A (0x3A) | PORTA<br>DDRA    | _                |                  |                  | -                   |                    | PORTR2<br>DDA2 | PORTA1<br>DDA1    | PORTA0<br>DDA0 | 57<br>57   |

| 0x19 (0x39)                | PINA             | _                | _                | _                | _                   | _                  | PINA2          | PINA1             | PINA0          | 57         |

| 0x18 (0x38)                | PORTB            | PORTB7           | PORTB6           | PORTB5           | PORTB4              | PORTB3             | PORTB2         | PORTB1            | PORTB0         | 57         |

| 0x17 (0x37)                | DDRB             | DDB7             | DDB6             | DDB5             | DDB4                | DDB3               | DDB2           | DDB1              | DDB0           | 57         |

| 0x16 (0x36)                | PINB             | PINB7            | PINB6            | PINB5            | PINB4               | PINB3              | PINB2          | PINB1             | PINB0          | 57         |

| 0x15 (0x35)                | GPIOR2           |                  |                  |                  |                     | ose I/O Register 2 |                |                   |                | 20         |

| 0x14 (0x34)                | GPIOR1           |                  |                  |                  |                     | ose I/O Register 1 | ·              |                   |                | 20         |

| 0x13 (0x33)                | GPIOR0           |                  |                  |                  | •                   | ose I/O Register 0 |                |                   |                | 20         |

| 0x12 (0x32)                | PORTD            | -                | PORTD6           | PORTD5           | PORTD4              | PORTD3             | PORTD2         | PORTD1            | PORTD0         | 57         |

| 0x11 (0x31)                | DDRD             | -                | DDD6             | DDD5             | DDD4                | DDD3               | DDD2           | DDD1              | DDD0           | 57         |

| 0x10 (0x30)                | PIND             | -                | PIND6            | PIND5            | PIND4               | PIND3              | PIND2          | PIND1             | PIND0          | 57         |

| 0x0F (0x2F)                | USIDR            |                  |                  |                  | USI Da              | ta Register        |                |                   |                | 144        |

| 0x0E (0x2E)                | USISR            | USISIF           | USIOIF           | USIPF            | USIDC               | USICNT3            | USICNT2        | USICNT1           | USICNT0        | 145        |

| 0x0D (0x2D)                | USICR            | USISIE           | USIOIE           | USIWM1           | USIWM0              | USICS1             | USICS0         | USICLK            | USITC          | 146        |

| 0x0C (0x2C)                | UDR              |                  | 1                | 1                |                     | Register (8-bit)   | 1              |                   |                | 129        |

| 0x0B (0x2B)                | UCSRA            | RXC              | TXC              | UDRE             | FE                  | DOR                | UPE            | U2X               | MPCM           | 129        |

| 0x0A (0x2A)                | UCSRB            | RXCIE            | TXCIE            | UDRIE            | RXEN                | TXEN               | UCSZ2          | RXB8              | TXB8           | 131        |

| 0x09 (0x29)                | UBRRL            | 107              | 4675             | 100              |                     | RH[7:0]            | 10:0           | 10:00             | 40155          | 133        |

| 0x08 (0x28)                | ACSR             | ACD              | ACBG             | ACO              | ACI                 | ACIE               | ACIC           | ACIS1             | ACIS0          | 149        |

| 0x07 (0x27)                | Reserved         | -                | -                | -                | -                   | -                  | -              | -                 | -              |            |

| 0x06 (0x26)                | Reserved         | -                | -                | -                | -                   | -                  | -              | -                 | -              |            |

| 0x05 (0x25)                | Reserved         | -                | -                | -                | -                   | -                  | -              | -                 | -              |            |

| 0x04 (0x24)                | Reserved         | -                |                  | -<br>LIDM1       | -                   |                    | -              | -                 | -              | 100        |

| 0x03 (0x23)<br>0x02 (0x22) | UCSRC<br>UBRRH   | _                | UMSEL            | UPM1<br>_        | UPM0                | USBS               | UCSZ1          | UCSZ0<br>RH[11:8] | UCPOL          | 132<br>133 |

| UNUZ (UNZZ)                |                  | _                | _                | _                | -                   | _                  |                | AIN1D             | AIN0D          | 133        |

| 0x01 (0x21)                | DIDR             |                  |                  |                  |                     |                    |                |                   |                |            |

- Note: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O Registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses.

# **Instruction Set Summary**

| Mnemonics        | Operands          | Description                            | Operation                                                                                    | Flags        | #Clocks |

|------------------|-------------------|----------------------------------------|----------------------------------------------------------------------------------------------|--------------|---------|

| ARITHMETIC AND L | OGIC INSTRUCTIONS | 3                                      |                                                                                              | -            | -       |

| ADD              | Rd, Rr            | Add two Registers                      | Rd ← Rd + Rr                                                                                 | Z,C,N,V,H    | 1       |

| ADC              | Rd, Rr            | Add with Carry two Registers           | $Rd \leftarrow Rd + Rr + C$                                                                  | Z,C,N,V,H    | 1       |

| ADIW             | Rdl,K             | Add Immediate to Word                  | $Rdh:RdI \leftarrow Rdh:RdI + K$                                                             | Z,C,N,V,S    | 2       |

| SUB              | Rd, Rr            | Subtract two Registers                 | Rd ← Rd - Rr                                                                                 | Z,C,N,V,H    | 1       |

| SUBI             | Rd, K             | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                                                       | Z,C,N,V,H    | 1       |

| SBC              | Rd, Rr            | Subtract with Carry two Registers      | Rd ← Rd - Rr - C                                                                             | Z,C,N,V,H    | 1       |

| SBCI             | Rd, K             | Subtract with Carry Constant from Reg. | $Rd \gets Rd - K - C$                                                                        | Z,C,N,V,H    | 1       |

| SBIW             | Rdl,K             | Subtract Immediate from Word           | $Rdh:Rdl \leftarrow Rdh:Rdl - K$                                                             | Z,C,N,V,S    | 2       |

| AND              | Rd, Rr            | Logical AND Registers                  | $Rd \gets Rd \bullet Rr$                                                                     | Z,N,V        | 1       |

| ANDI             | Rd, K             | Logical AND Register and Constant      | $Rd \gets Rd \bullet K$                                                                      | Z,N,V        | 1       |

| OR               | Rd, Rr            | Logical OR Registers                   | $Rd \leftarrow Rd \lor Rr$                                                                   | Z,N,V        | 1       |

| ORI              | Rd, K             | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                                                                    | Z,N,V        | 1       |

| EOR              | Rd, Rr            | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                                                                 | Z,N,V        | 1       |

| COM              | Rd                | One's Complement                       | $Rd \leftarrow 0xFF - Rd$                                                                    | Z,C,N,V      | 1       |

| NEG              | Rd                | Two's Complement                       | Rd ← 0x00 - Rd                                                                               | Z,C,N,V,H    | 1       |

| SBR              | Rd,K              | Set Bit(s) in Register                 | Rd ← Rd v K                                                                                  | Z,N,V        | 1       |

| CBR              | Rd,K              | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                        | Z,N,V        | 1       |

| INC              | Rd                | Increment                              | $Rd \leftarrow Rd + 1$                                                                       | Z,N,V        | 1       |

| DEC              | Rd                | Decrement                              | $Rd \leftarrow Rd - 1$                                                                       | Z,N,V        | 1       |

|                  |                   |                                        |                                                                                              |              |         |

| TST              | Rd                | Test for Zero or Minus                 | Rd ← Rd • Rd                                                                                 | Z,N,V        | 1       |

| CLR              | Rd                | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                                                                 | Z,N,V        | 1       |

| SER              | Rd                | Set Register                           | $Rd \leftarrow 0xFF$                                                                         | None         | 1       |

| BRANCH INSTRUCT  | TIONS             |                                        | I                                                                                            | 1            | 1       |

| RJMP             | k                 | Relative Jump                          | $PC \leftarrow PC + k + 1$                                                                   | None         | 2       |

| IJMP             |                   | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                                                            | None         | 2       |

| RCALL            | k                 | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                                                                   | None         | 3       |

| ICALL            |                   | Indirect Call to (Z)                   | $PC \leftarrow Z$                                                                            | None         | 3       |

| RET              |                   | Subroutine Return                      | $PC \leftarrow STACK$                                                                        | None         | 4       |

| RETI             |                   | Interrupt Return                       | $PC \leftarrow STACK$                                                                        | 1            | 4       |

| CPSE             | Rd,Rr             | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                     | None         | 1/2/3   |

| СР               | Rd,Rr             | Compare                                | Rd – Rr                                                                                      | Z, N,V,C,H   | 1       |

| CPC              | Rd,Rr             | Compare with Carry                     | Rd – Rr – C                                                                                  | Z, N,V,C,H   | 1       |

| CPI              | Rd,K              | Compare Register with Immediate        | Bd – K                                                                                       | Z, N,V,C,H   | 1       |

| SBRC             | Rr, b             | Skip if Bit in Register Cleared        | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3                                                     | None         | 1/2/3   |

| SBRS             | Rr, b             | Skip if Bit in Register is Set         | if $(\text{Rr}(b)=1)$ PC $\leftarrow$ PC + 2 or 3                                            | None         | 1/2/3   |

| SBIC             | P, b              |                                        |                                                                                              |              | 1/2/3   |

|                  |                   | Skip if Bit in I/O Register Cleared    | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                             | None         |         |

| SBIS             | P, b              | Skip if Bit in I/O Register is Set     | if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                             | None         | 1/2/3   |

| BRBS             | s, k              | Branch if Status Flag Set              | if $(SREG(s) = 1)$ then $PC \leftarrow PC+k + 1$                                             | None         | 1/2     |

| BRBC             | s, k              | Branch if Status Flag Cleared          | if $(SREG(s) = 0)$ then $PC \leftarrow PC + k + 1$                                           | None         | 1/2     |

| BREQ             | k                 | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRNE             | k                 | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRCS             | k                 | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRCC             | k                 | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRSH             | k                 | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRLO             | k                 | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRMI             | k                 | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRPL             | k                 | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRGE             | k                 | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                                        | None         | 1/2     |

| BRLT             | k                 | Branch if Less Than Zero, Signed       | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                                        | None         | 1/2     |

| BRHS             | k                 | Branch if Half Carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRHC             | k                 | Branch if Half Carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRTS             | k                 | Branch if T Flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRTC             | k                 | Branch if T Flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1                                                   | None         | 1/2     |

| BRVS             | k                 | Branch if Overflow Flag is Set         | if $(V = 1)$ then PC $\leftarrow$ PC + k + 1                                                 |              | 1/2     |

| BRVC             | k k               | Branch if Overflow Flag is Cleared     | if $(V = 0)$ then $PC \leftarrow PC + k + 1$<br>if $(V = 0)$ then $PC \leftarrow PC + k + 1$ | None<br>None | 1/2     |

|                  |                   |                                        |                                                                                              |              |         |

| BRIE             | k                 | Branch if Interrupt Enabled            | if $(1 = 1)$ then PC $\leftarrow$ PC + k + 1                                                 | None         | 1/2     |

| BRID             | k                 | Branch if Interrupt Disabled           | if ( $I = 0$ ) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2     |

| BIT AND BIT-TEST |                   |                                        |                                                                                              | <b>.</b>     | T       |

| SBI              | P,b               | Set Bit in I/O Register                | I/O(P,b) ← 1                                                                                 | None         | 2       |

| CBI              | P,b               | Clear Bit in I/O Register              | I/O(P,b) ← 0                                                                                 | None         | 2       |

| LSL              | Rd                | Logical Shift Left                     | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                               | Z,C,N,V      | 1       |

|                  |                   | La sizal Ohitt Disht                   |                                                                                              | Z,C,N,V      | 1 1     |

| LSR              | Rd                | Logical Shift Right                    | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                               | Z,C,N,V      | 1       |

# ATtiny2313/V

| Mnemonics       | Operands    | Description                      | Operation                                                                                                     | Flags   | #Clocks |

|-----------------|-------------|----------------------------------|---------------------------------------------------------------------------------------------------------------|---------|---------|

| ROR             | Rd          | Rotate Right Through Carry       | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$                                                 | Z,C,N,V | 1       |

| ASR             | Rd          | Arithmetic Shift Right           | $Rd(n) \leftarrow Rd(n+1), n=06$                                                                              | Z,C,N,V | 1       |

| SWAP            | Rd          | Swap Nibbles                     | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                                                   | None    | 1       |

| BSET            | s           | Flag Set                         | SREG(s) ← 1                                                                                                   | SREG(s) | 1       |

| BCLR            | s           | Flag Clear                       | $SREG(s) \leftarrow 0$                                                                                        | SREG(s) | 1       |

| BST             | Rr, b       | Bit Store from Register to T     | $T \leftarrow Rr(b)$                                                                                          | Т       | 1       |

| BLD             | Rd, b       | Bit load from T to Register      | $Rd(b) \leftarrow T$                                                                                          | None    | 1       |

| SEC             |             | Set Carry                        | C ← 1                                                                                                         | С       | 1       |

| CLC             |             | Clear Carry                      | C ← 0                                                                                                         | С       | 1       |

| SEN             |             | Set Negative Flag                | N ← 1                                                                                                         | Ν       | 1       |

| CLN             |             | Clear Negative Flag              | N ← 0                                                                                                         | Ν       | 1       |

| SEZ             |             | Set Zero Flag                    | Z ← 1                                                                                                         | Z       | 1       |

| CLZ             |             | Clear Zero Flag                  | Z ← 0                                                                                                         | Z       | 1       |

| SEI             |             | Global Interrupt Enable          | I ← 1                                                                                                         | 1       | 1       |

| CLI             |             | Global Interrupt Disable         | I ← 0                                                                                                         | 1       | 1       |

| SES             |             | Set Signed Test Flag             | S ← 1                                                                                                         | S       | 1       |

| CLS             |             | Clear Signed Test Flag           | S ← 0                                                                                                         | S       | 1       |

| SEV             |             | Set Twos Complement Overflow.    | V ← 1                                                                                                         | V       | 1       |

| CLV             |             | Clear Twos Complement Overflow   | V ← 0                                                                                                         | V       | 1       |

| SET             |             | Set T in SREG                    | T ← 1                                                                                                         | т       | 1       |

| CLT             |             | Clear T in SREG                  | T ← 0                                                                                                         | т       | 1       |

| SEH             |             | Set Half Carry Flag in SREG      | H ← 1                                                                                                         | н       | 1       |

| CLH             |             | Clear Half Carry Flag in SREG    | H ← 0                                                                                                         | н       | 1       |

| DATA TRANSFER I | NSTRUCTIONS |                                  |                                                                                                               | ł       |         |

| MOV             | Rd, Rr      | Move Between Registers           | Rd ← Rr                                                                                                       | None    | 1       |

| MOVW            | Rd, Rr      | Copy Register Word               | Rd+1:Rd ← Rr+1:Rr                                                                                             | None    | 1       |

| LDI             | Rd, K       | Load Immediate                   | $Rd \leftarrow K$                                                                                             | None    | 1       |

| LD              | Rd, X       | Load Indirect                    | $Rd \leftarrow (X)$                                                                                           | None    | 2       |

| LD              | Rd, X+      | Load Indirect and Post-Inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$                                                                       | None    | 2       |

| LD              | Rd, - X     | Load Indirect and Pre-Dec.       | $X \leftarrow X - 1, Rd \leftarrow (X)$                                                                       | None    | 2       |

| LD              | Rd, Y       | Load Indirect                    | $Rd \leftarrow (Y)$                                                                                           | None    | 2       |

| LD              | Rd, Y+      | Load Indirect and Post-Inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                                                                       | None    | 2       |

| LD              | Rd, - Y     | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                                                                       | None    | 2       |

| LDD             | Rd,Y+q      | Load Indirect and Tre-Dec.       | $Rd \leftarrow (Y + q)$                                                                                       | None    | 2       |

| LD              | Rd, Z       | Load Indirect                    | $Rd \leftarrow (Z)$                                                                                           | None    | 2       |

| LD              | Rd, Z+      | Load Indirect and Post-Inc.      | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                                                         | None    | 2       |

| LD              | Rd, -Z      | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                                                                       | None    | 2       |

| LDD             | Rd, Z+q     | Load Indirect and Tre-Dec.       | $Rd \leftarrow (Z + q)$                                                                                       | None    | 2       |

| LDS             | Rd, k       | Load Direct from SRAM            | $Rd \leftarrow (k)$                                                                                           | None    | 2       |

| ST              | X, Rr       | Store Indirect                   | $(X) \leftarrow Rr$                                                                                           | None    | 2       |

|                 |             |                                  |                                                                                                               |         | 2       |

| ST<br>ST        | X+, Rr      | Store Indirect and Post-Inc.     | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$ $X \leftarrow X - 1, (X) \leftarrow \operatorname{Rr}$ | None    | 2       |

|                 | - X, Rr     | Store Indirect and Pre-Dec.      |                                                                                                               | None    | 2       |

| ST              | Y, Rr       | Store Indirect                   | $(Y) \leftarrow Rr$                                                                                           | None    |         |

| ST              | Y+, Rr      | Store Indirect and Post-Inc.     | $(Y) \leftarrow \operatorname{Rr}, Y \leftarrow Y + 1$                                                        | None    | 2       |

| ST              | - Y, Rr     | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                                                                       | None    | 2       |

| STD             | Y+q,Rr      | Store Indirect with Displacement | $(Y + q) \leftarrow Rr$                                                                                       | None    | 2       |

| ST              | Z, Rr       | Store Indirect                   | $(Z) \leftarrow \operatorname{Rr}$                                                                            | None    | 2       |

| ST              | Z+, Rr      | Store Indirect and Post-Inc.     | $(Z) \leftarrow \operatorname{Rr}, Z \leftarrow Z + 1$                                                        | None    | 2       |

| ST              | -Z, Rr      | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                                                                       | None    | 2       |

| STD             | Z+q,Rr      | Store Indirect with Displacement | $(Z + q) \leftarrow Rr$                                                                                       | None    | 2       |

| STS             | k, Rr       | Store Direct to SRAM             | $(k) \leftarrow Rr$                                                                                           | None    | 2       |

| LPM             | +           | Load Program Memory              | $R0 \leftarrow (Z)$                                                                                           | None    | 3       |

| LPM             | Rd, Z       | Load Program Memory              | $Rd \leftarrow (Z)$                                                                                           | None    | 3       |

| LPM             | Rd, Z+      | Load Program Memory and Post-Inc | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                                                         | None    | 3       |

| SPM             |             | Store Program Memory             | (Z) ← R1:R0                                                                                                   | None    | -       |

| IN              | Rd, P       | In Port                          | $Rd \leftarrow P$                                                                                             | None    | 1       |

| OUT             | P, Rr       | Out Port                         | P ← Rr                                                                                                        | None    | 1       |

| PUSH            | Rr          | Push Register on Stack           | $STACK \leftarrow Rr$                                                                                         | None    | 2       |

| POP             | Rd          | Pop Register from Stack          | $Rd \gets STACK$                                                                                              | None    | 2       |

| MCU CONTROL INS | STRUCTIONS  |                                  |                                                                                                               |         |         |

| NOP             |             | No Operation                     |                                                                                                               | None    | 1       |

| SLEEP           |             | Sleep                            | (see specific descr. for Sleep function)                                                                      | None    | 1       |

| WDR             |             | Watchdog Reset                   | (see specific descr. for WDR/timer)                                                                           | None    | 1       |

|                 |             | Break                            | For On-chip Debug Only                                                                                        | None    | N/A     |

## **Ordering Information**

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code                                                                                                                                                     | Package <sup>(1)</sup>                     | Operation Range               |

|----------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------|

| 10                         | 1.8 - 5.5V   | ATtiny2313V-10PI<br>ATtiny2313V-10PU <sup>(2)</sup><br>ATtiny2313V-10SI<br>ATtiny2313V-10SU <sup>(2)</sup><br>ATtiny2313V-10MI<br>ATtiny2313V-10MU <sup>(2)</sup> | 20P3<br>20P3<br>20S<br>20S<br>20M1<br>20M1 | Industrial<br>(-40°C to 85°C) |

| 20                         | 2.7 - 5.5V   | ATtiny2313-20PI<br>ATtiny2313-20PU <sup>(2)</sup><br>ATtiny2313-20SI<br>ATtiny2313-20SU <sup>(2)</sup><br>ATtiny2313-20MI<br>ATtiny2313-20MU <sup>(2)</sup>       | 20P3<br>20P3<br>20S<br>20S<br>20M1<br>20M1 | Industrial<br>(-40°C to 85°C) |

Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For Speed vs.  $V_{CC}$  see Figure 82 on page 180 and Figure 83 on page 180.

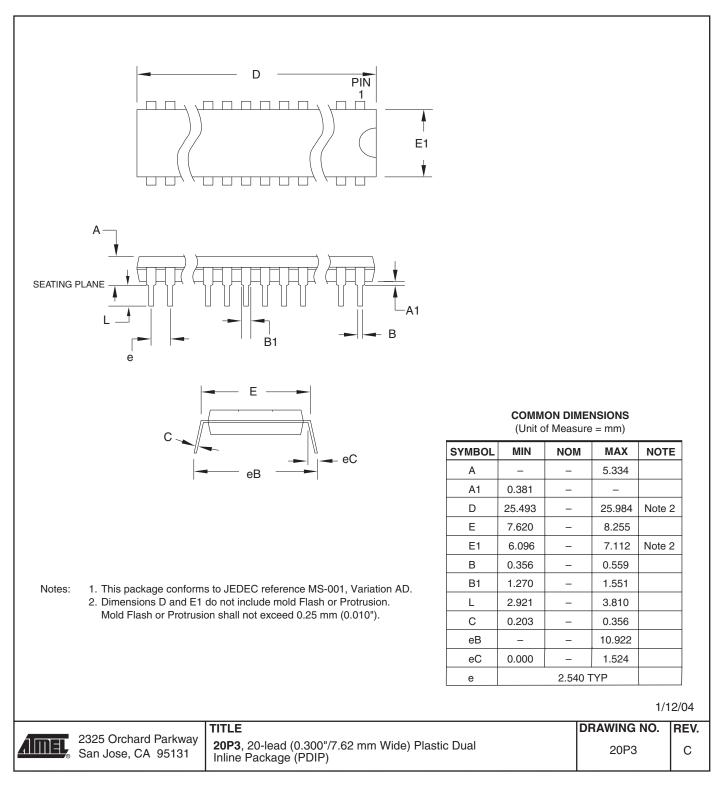

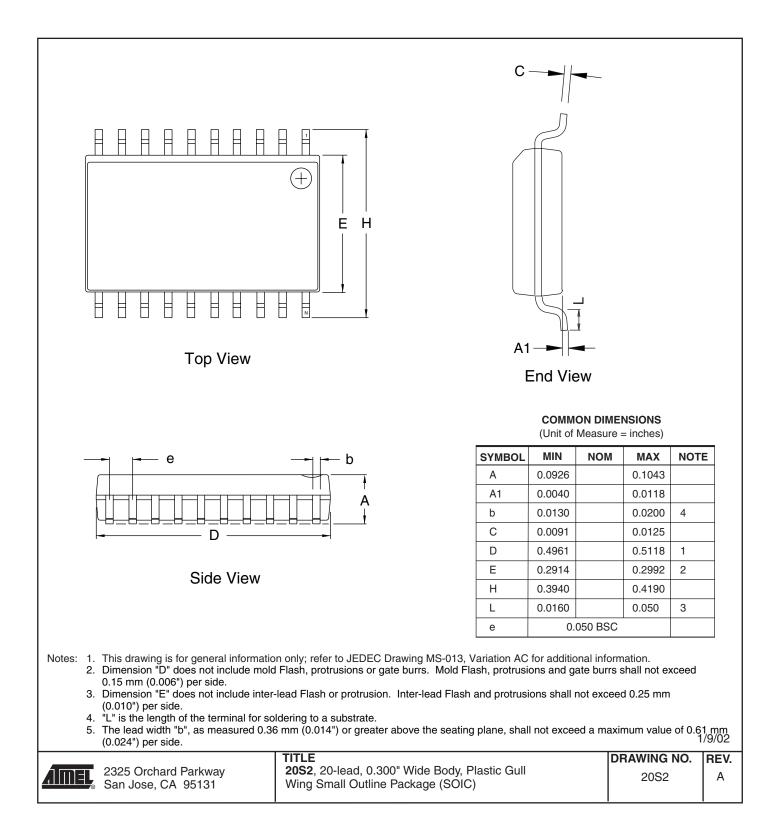

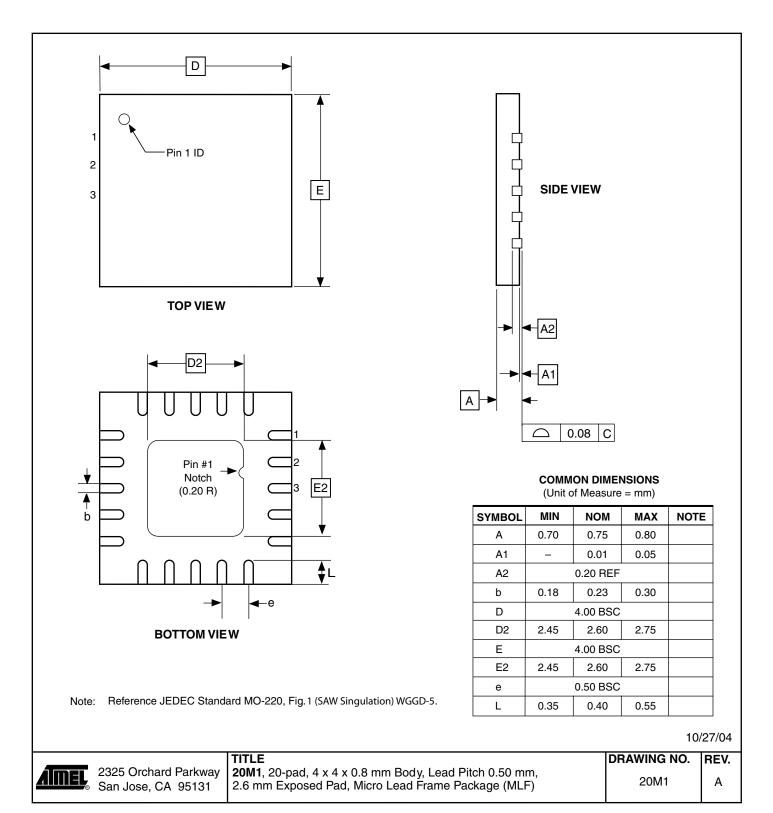

| Package Type |                                                                               |  |  |

|--------------|-------------------------------------------------------------------------------|--|--|

| 20P3         | 20-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                      |  |  |

| 20S          | 20-lead, 0.300" Wide, Plastic Gull Wing Small Outline Package (SOIC)          |  |  |

| 20M1         | 20-pad, 4 x 4 x 0.8 mm Body, Quad Flat No-Lead/Micro Lead Frame Package (MLF) |  |  |

# **Packaging Information**

#### 20P3

# ATtiny2313/V

#### 20M1

## Errata

The revision in this section refers to the revision of the ATtiny2313 device.

#### ATtiny2313 Rev B

- Wrong values read after Erase Only operation

- Parallel Programming does not work

- Watchdog Timer Interrupt disabled

- EEPROM can not be written below 1.9 volts

#### 1. Wrong values read after Erase Only operation

At supply voltages below 2.7 V, an EEPROM location that is erased by the Erase Only operation may read as programmed (0x00).

#### **Problem Fix/Workaround**

If it is necessary to read an EEPROM location after Erase Only, use an Atomic Write operation with 0xFF as data in order to erase a location. In any case, the Write Only operation can be used as intended. Thus no special considerations are needed as long as the erased location is not read before it is programmed.

#### 2. Parallel Programming does not work

Parallel Programming is not functioning correctly. Because of this, reprogramming of the device is impossible if one of the following modes are selected:

- In-System Programming disabled (SPIEN unprogrammed)

- Reset Disabled (RSTDISBL programmed)

#### **Problem Fix/Workaround**

Serial Programming is still working correctly. By avoiding the two modes above, the device can be reprogrammed serially.

#### 3. Watchdog Timer Interrupt disabled

If the watchdog timer interrupt flag is not cleared before a new timeout occurs, the watchdog will be disabled, and the interrupt flag will automatically be cleared. This is only applicable in interrupt only mode. If the Watchdog is configured to reset the device in the watchdog time-out following an interrupt, the device works correctly.

#### Problem fix / Workaround

Make sure there is enough time to always service the first timeout event before a new watchdog timeout occurs. This is done by selecting a long enough time-out period.

#### 4. EEPROM can not be written below 1.9 volts

Writing the EEPROM at  $V_{CC}$  below 1.9 volts might fail.

#### Problem fix / Workaround

Do not write the EEPROM when  $V_{CC}$  is below 1.9 volts.

ATtiny2313 Rev A Revision A has not been sampled.

# ATtiny2313/V

| Datasheet Revision<br>History                           | Please note that the referring page numbers in this section are referred to this docu-<br>ment. The referring revision in this section are referring to the document revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Changes from Rev.<br>2514G-10/04 to Rev.<br>2514H-02/05 | <ol> <li>Updated Table 6 on page 24, Table 15 on page 33, Table 68 on page 160<br/>and Table 80 on page 178.</li> <li>Changed CKSEL default value in "Default Clock Source" on page 22 to<br/>8 MHz.</li> <li>Updated "Programming the Flash" on page 165, "Programming the<br/>EEPROM" on page 167 and "Enter Programming Mode" on page 163.</li> <li>Updated "DC Characteristics" on page 177.</li> <li>MLF option updated to "Quad Flat No-Lead/Micro Lead Frame<br/>(QFN/MLF)"</li> </ol>                                                                                                                                                        |  |  |  |

| Changes from Rev.<br>2514F-08/04 to Rev.<br>2514G-10/04 | <ol> <li>Updated "Features" on page 1.</li> <li>Updated "Pinout ATtiny2313" on page 2.</li> <li>Updated "Ordering Information" on page 10.</li> <li>Updated "Packaging Information" on page 11.</li> <li>Updated "Errata" on page 14.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Changes from Rev.<br>2514E-04/04 to Rev.<br>2514F-08/04 | <ol> <li>Updated "Features" on page 1.</li> <li>Updated "Alternate Functions of Port B" on page 52.</li> <li>Updated "Calibration Byte" on page 160.</li> <li>Moved Table 69 on page 160 and Table 70 on page 161 to "Page Size"<br/>on page 160.</li> <li>Updated "Enter Programming Mode" on page 163.</li> <li>Updated "Serial Programming Algorithm" on page 173.</li> <li>Updated Table 78 on page 174.</li> <li>Updated "DC Characteristics" on page 177.</li> <li>Updated "ATtiny2313 Typical Characteristics" on page 181.</li> <li>Changed occurences of PCINT15 to PCINT7, EEMWE to EEMPE and<br/>EEWE to EEPE in the document.</li> </ol> |  |  |  |

| Changes from Rev.<br>2514D-03/04 to Rev.<br>2514E-04/04 | <ol> <li>Speed Grades changed         <ul> <li>12MHz to 10MHz</li> <li>24MHz to 20MHz</li> </ul> </li> <li>Updated Figure 1 on page 2.</li> <li>Updated "Ordering Information" on page 10.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

- 3. Updated "Ordering Information" on page 10.

- 4. Updated "Maximum Speed vs. VCC" on page 180.

- 5. Updated "ATtiny2313 Typical Characteristics" on page 181.

# Changes from Rev. 2514C-12/03 to Rev. 2514D-03/04

- 1. Updated Table 2 on page 22.

- 2. Replaced "Watchdog Timer" on page 38.

- 3. Added "Maximum Speed vs. VCC" on page 180.

- 4. "Serial Programming Algorithm" on page 173 updated.

- 5. Changed mA to  $\mu$ A in preliminary Figure 136 on page 207.

- 6. "Ordering Information" on page 10 updated. MLF package option removed

- 7. Package drawing "20P3" on page 11 updated.

- 8. Updated C-code examples.

- 9. Renamed instances of SPMEN to SELFPRGEN, Self Programming Enable.

- 1. Updated "Calibrated Internal RC Oscillator" on page 24.

Changes from Rev. 2514A-09/03 to Rev.

Changes from Rev. 2514B-09/03 to Rev.

2514B-09/03

2514C-12/03

- 1. Fixed typo from UART to USART and updated Speed Grades and Power Consumption Estimates in "Features" on page 1.

- 2. Updated "Pin Configurations" on page 2.

- 3. Updated Table 15 on page 33 and Table 80 on page 178.

- 4. Updated item 5 in "Serial Programming Algorithm" on page 173.

- 5. Updated "Electrical Characteristics" on page 177.

- 6. Updated Figure 82 on page 180 and added Figure 83 on page 180.

- 7. Changed SFIOR to GTCCR in "Register Summary" on page 6.

- 8. Updated "Ordering Information" on page 10.

- 9. Added new errata in "Errata" on page 14.

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

*Memory* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

## Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, AVR<sup>®</sup>, and AVR Studio<sup>®</sup> are registered trademarks, and Everywhere You Are<sup>SM</sup> are the trademarks of Atmel Corporation or its subsidiaries. Microsoft<sup>®</sup>, Windows<sup>®</sup>, Windows NT<sup>®</sup>, and Windows XP<sup>®</sup> are the registered trademarks of Microsoft Corporation. Other terms and product names may be trademarks of others.