# **N-Channel Enhancement Power Mosfet Specification**

### **Features**

- Advanced trench cell design

- High speed switch

### **Applications**

- Portable appliances

- Notebook/PC appliances

- Power Management

- DC/DC Converter

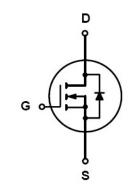

1: Gate 2: Source 3: Drain

### **Quick reference**

$BV \ge 60 V ID=2.2A$

$$\label{eq:rds} \begin{split} \text{RDS(ON)} & \leq ~105~\text{m}\Omega \; \textcircled{0} \; \text{VGS} = 10 \; \text{V} \\ \text{RDS(ON)} & \leq ~130~\text{m}\Omega \; \textcircled{0} \; \text{VGS} = 5 \; \text{V} \end{split}$$

## Limiting Values

| Symbol    | Parameter            | Rating | Unit |  |

|-----------|----------------------|--------|------|--|

| $V_{DSS}$ | Drain-Source Voltage | 60     | V    |  |

| $V_{GSS}$ | Gate-Source Voltage  | ± 20   |      |  |

REV.08 1 of 2

# Electrical Characteristics ( Ta = 25°C Unless Otherwise Noted )

| Symbol                             | Parameter                      | Conditions                                       |                        | Min | Тур | Max   | Unit |  |  |  |

|------------------------------------|--------------------------------|--------------------------------------------------|------------------------|-----|-----|-------|------|--|--|--|

| Static Characteristics             |                                |                                                  |                        |     |     |       |      |  |  |  |

| BV <sub>DSS</sub>                  | Drain-Source Breakdown Voltage | $V_{GS} = 0 \text{ V}, I_{DS} = 250 \mu\text{A}$ |                        | 60  | -   | -     | V    |  |  |  |

| V <sub>GS(th)</sub>                | Gate Threshold Voltage         | $V_{DS} = V_{GS}$ , $I_{DS} = 250 \mu A$         |                        | 1.0 | 1.6 | 2.5   | >    |  |  |  |

| I <sub>DSS</sub>                   | Drain Leakage Current          | V <sub>DS</sub> = 48 V, V <sub>GS</sub> = 0V     |                        | ï   | -   | 1     | μΑ   |  |  |  |

|                                    |                                |                                                  | T <sub>J</sub> = 85 °C | í   | -   | 30    | μΑ   |  |  |  |

| I <sub>GSS</sub>                   | Gate Leakage Current           | V <sub>GS</sub> = ±20 V, V <sub>DS</sub> = 0 V   |                        | ť   | -   | ± 100 | nΑ   |  |  |  |

| R <sub>DS(ON)</sub> <sup>a</sup>   | On-State Resistance            | $V_{GS}$ = 10 V, $I_{DS}$ = 0.5A                 |                        | -   | -   | 105   | mΩ   |  |  |  |

|                                    |                                | V <sub>GS</sub> = 5 V, I <sub>DS</sub> = 0.5 A   |                        | -   | -   | 130   |      |  |  |  |

| Diode Characteristics <sup>b</sup> |                                |                                                  |                        |     |     |       |      |  |  |  |

| V <sub>SD</sub>                    | Diode Forward Voltage          | I <sub>SD</sub> = 0.5 A, V <sub>GS</sub> = 0V    |                        | -   | 0.7 | 1.3   | ٧    |  |  |  |

#### Notes:

This wafer must be stored at N2 box ( RH<20 % ).

Wafer must be completely assembled within two months.

a : CP measured on wafer by probe card. ( RDS(ON) depended on packaged type and amount of bonding wires )

b : Pulse test ; pulse width  $\, \leqslant \, 300 \, \mu \, \text{s}$  , duty cycle  $\, \leqslant \, 2\%$