www.ti.com

SBVS009B - JANUARY 1998 - REVISED MAY 2009

# **PWM SOLENOID/VALVE DRIVER**

### FEATURES

- HIGH OUTPUT DRIVE: 2.7A

- WIDE SUPPLY RANGE: +8V to +60V

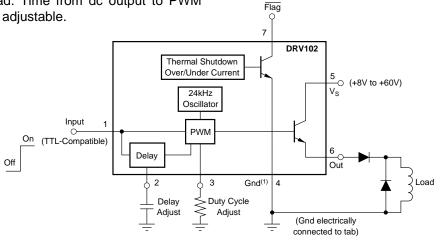

- COMPLETE FUNCTION PWM Output Internal 24kHz Oscillator Digital Control Input Adjustable Delay and Duty Cycle Over/Under Current Indicator

- FULLY PROTECTED Thermal Shutdown with Indicator Internal Current Limit

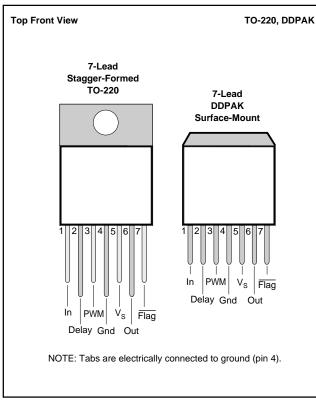

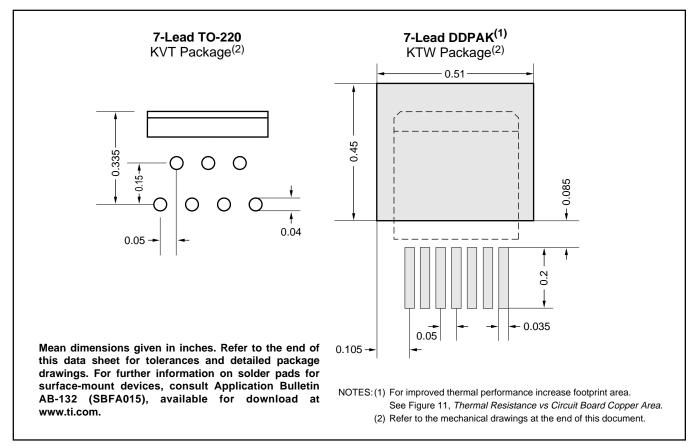

- POWER PACKAGES: 7-Lead TO-220 and 7-Lead Surface-Mount DDPAK

### DESCRIPTION

The DRV102 is a high-side power switch employing a pulse-width modulated (PWM) output. Its rugged design is optimized for driving electromechanical devices such as valves, solenoids, relays, actuators, and positioners. The DRV102 is also ideal for driving thermal devices such as heaters and lamps. PWM operation conserves power and reduces heat rise in the device, resulting in higher reliability. In addition, adjustable PWM allows fine control of the power delivered to the load. Time from dc output to PWM output is externally adjustable.

# APPLICATIONS

- ELECTROMECHANICAL DRIVERS: Solenoids Positioners Actuators High Power Relays/Contactors Valves Clutches/Brakes

- SOLENOID OVERHEAT PROTECTORS

- FLUID AND GAS FLOW CONTROLLERS

- PART HANDLERS

- ELECTRICAL HEATERS/COOLERS

- MOTOR SPEED CONTROLLERS

- INDUSTRIAL CONTROL

- FACTORY AUTOMATION

- MEDICAL ANALYSIS

- PHOTOGRAPHIC PROCESSING

The DRV102 can be set to provide a strong initial closure, automatically switching to a soft hold mode for power savings. Duty cycle can be controlled by a resistor, analog voltage, or digital-to-analog converter for versatility. A flag output indicates thermal shutdown and over/under current limit. A wide supply range allows use with a variety of actuators.

The DRV102 is available in a 7-lead staggered TO-220 package and a 7-lead surface-mount DDPAK plastic power package. It operates from -55°C to +125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# **SPECIFICATIONS**

At  $T_C = +25^{\circ}C$ ,  $V_S = +24V$ , load = series diode MUR415 and  $100\Omega$ , and  $4.99k\Omega$  Flag pull-up to +5V, unless otherwise noted.

| PARAMETER                              | CONDITIONS                                         | MIN     | ТҮР                           | MAX                                   | UNITS    |  |

|----------------------------------------|----------------------------------------------------|---------|-------------------------------|---------------------------------------|----------|--|

| OUTPUT                                 |                                                    |         |                               |                                       |          |  |

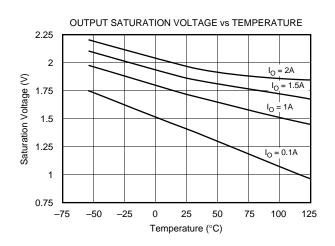

| Output Saturation Voltage, Source      | $I_{O} = 1A$                                       |         | +1.7                          | +2.2                                  | V        |  |

|                                        | $I_{0} = 0.1A$                                     |         | +1.3                          | +1.7                                  | V        |  |

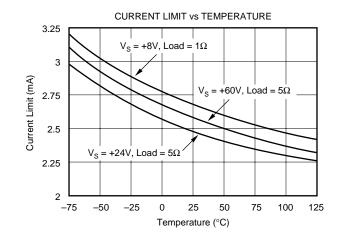

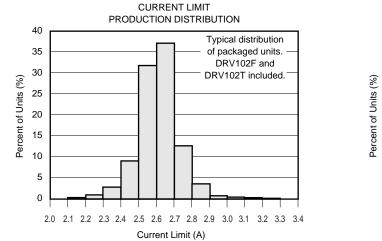

| Current Limit                          | Ū                                                  | 2       | 2.7                           | 3.4                                   | А        |  |

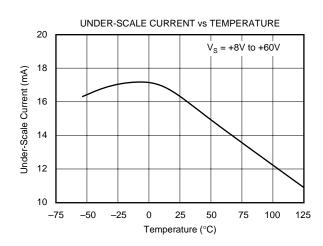

| Under-Scale Current                    |                                                    |         | 16                            |                                       | mA       |  |

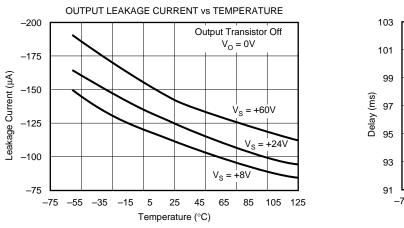

| Leakage Current                        | Output Transistor Off, $V_S = +60V$ , $V_O = 0V$   |         | ±0.01                         | ±2                                    | mA       |  |

| DIGITAL CONTROL INPUT <sup>(1)</sup>   |                                                    |         |                               |                                       |          |  |

| V <sub>CTR</sub> Low (output disabled) |                                                    | 0       |                               | +1.2                                  | V        |  |

| V <sub>CTR</sub> High (output enabled) |                                                    | +2.2    |                               | Vs                                    | V        |  |

| I <sub>CTR</sub> Low (output disabled) | V <sub>CTR</sub> = 0V                              |         | -80(2)                        | 3                                     | μA       |  |

| I <sub>CTR</sub> High (output enabled) | $V_{CTR} = +5V$                                    |         | 20 <sup>(2)</sup>             |                                       | μA       |  |

| Propagation Delay: On-to-Off           |                                                    |         | 0.9                           |                                       | μs       |  |

| Off-to-On                              |                                                    |         | 1.8                           |                                       | μs       |  |

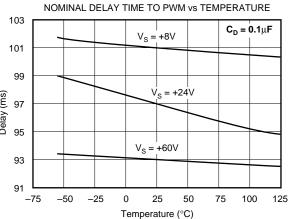

| DELAY TO PWM <sup>(3)</sup>            | dc to PWM Mode                                     |         | _                             |                                       | P        |  |

| Delay Equation <sup>(4)</sup>          |                                                    | Delav t | l<br>o PWM ≈ C <sub>D</sub> ∙ | 10 <sup>6</sup> (C <sub>p</sub> in F) | s        |  |

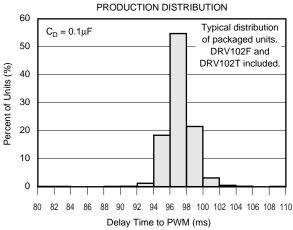

| Delay Time                             | $C_D = 0.1 \mu F$                                  | 80      | 97                            | 110                                   | ms       |  |

| Minimum Delay Time <sup>(5)</sup>      | $C_D = 0$                                          |         | 15                            |                                       | μs       |  |

| DUTY CYCLE ADJUST                      | -                                                  |         |                               |                                       |          |  |

| Duty Cycle Range                       |                                                    |         | 10 to 90                      |                                       | %        |  |

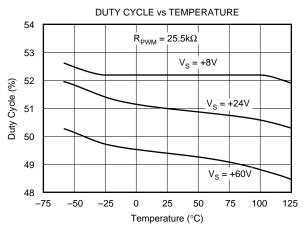

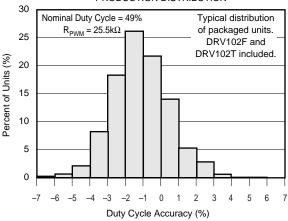

| Duty Cycle Accuracy                    | 49% Duty Cycle, $R_{PWM} = 25.5 k\Omega$           |         | ±1                            | ±7                                    | %        |  |

| vs Supply Voltage                      | 49% Duty Cycle, $V_S = 8V$ to 60V                  |         | ±1                            | ±5                                    | %        |  |

| Nonlinearity <sup>(6)</sup>            | 20% to 80% Duty Cycle                              |         | ±2                            |                                       | % FSR    |  |

| DYNAMIC RESPONSE                       |                                                    |         |                               |                                       |          |  |

| Output Voltage Rise Time               | $V_{0} = 10\%$ to 90% of $V_{S}$                   |         | 0.25                          | 2.5                                   | μs       |  |

| Output Voltage Fall Time               | $V_{0} = 90\%$ to 10% of $V_{S}$                   |         | 0.25                          | 2.5                                   | μs       |  |

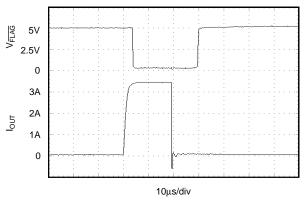

| Oscillator Frequency                   | 10 10 10 10 10                                     | 19      | 24                            | 29                                    | kHz      |  |

| FLAG                                   |                                                    |         |                               |                                       |          |  |

| Normal Operation                       | 20k $\Omega$ Pull-Up to +5V, I <sub>O</sub> < 1.5A | +4      | +4.9                          |                                       | V        |  |

| Fault <sup>(7)</sup>                   | Sinking 1mA                                        |         | +0.2                          | +0.4                                  | v        |  |

| Sink Current                           | $V_{\overline{FLAG}} = 0.4V$                       |         | 2                             | 10.1                                  | mA       |  |

| Under-Current Flag: Set                | VFLAG = 0.1V                                       |         | 5.2                           |                                       | μs       |  |

| Reset                                  |                                                    |         | 11                            |                                       | μs       |  |

| Over-Current Flag: Set                 |                                                    |         | 5.2                           |                                       | μs<br>μs |  |

| Reset                                  |                                                    |         | 11.5                          |                                       | μs<br>μs |  |

| THERMAL SHUTDOWN                       |                                                    |         |                               |                                       |          |  |

| Junction Temperature                   |                                                    |         |                               |                                       |          |  |

| Shutdown                               |                                                    |         | +165                          |                                       | °C       |  |

| Reset from Shutdown                    |                                                    |         | +150                          |                                       | °Č       |  |

| POWER SUPPLY                           |                                                    | 1       |                               |                                       | -        |  |

| Specified Operating Voltage            |                                                    |         | +24                           |                                       | V        |  |

| Operating Voltage Range                |                                                    | +8      |                               | +60                                   | V        |  |

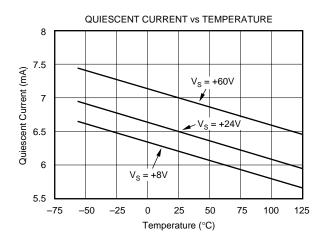

| Quiescent Current                      | $I_{O} = 0$                                        | +0      | 6.5                           | 9                                     | mA       |  |

|                                        |                                                    |         | 0.0                           | Ť                                     |          |  |

|                                        |                                                    | . 55    |                               | +125                                  | °C       |  |

| Specified Range                        |                                                    | -55     |                               | +125                                  |          |  |

| Storage Range                          |                                                    | -55     |                               | +125                                  | °C       |  |

| Thermal Resistance, $\theta_{JC}$      |                                                    |         |                               |                                       | 00.004   |  |

| 7-Lead DDPAK, 7-Lead TO-220            |                                                    |         | 3                             |                                       | °C/W     |  |

| Thermal Resistance, $\theta_{JA}$      | No Llost Cists                                     |         | 65                            |                                       | 0000     |  |

| 7-Lead DDPAK, 7-Lead TO-220            | No Heat Sink                                       |         | 65                            |                                       | °C/W     |  |

NOTES: (1) Logic high enables output (normal operation). (2) Negative conventional current flows out of the terminals. (3) Constant dc output to PWM (pulse-width modulated) time. (4) Maximum delay is determined by an external capacitor. Pulling the Delay Adjust pin low corresponds to an infinite (continuous) delay. (5) Connecting the Delay Adjust pin to +5V reduces delay time to 3µs. (6) V<sub>IN</sub> at pin 3 to percent of duty cycle at pin 6. (7) A fault results from over-temperature, over-current, or under-current conditions.

#### **CONNECTION DIAGRAMS**

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| –0.2V to V <sub>S</sub> (24V max) |

|-----------------------------------|

| 0.2V to V <sub>S</sub> (24V max)  |

| 55°C to +125°C                    |

| –55°C to +125°C                   |

| +150°C                            |

| +300°C                            |

|                                   |

NOTES: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. (2) Vapor-phase or IR reflow techniques are recommended for soldering the DRV102F surface-mount package. Wave soldering is not recommended due to excessive thermal shock and "shadowing" of nearby devices.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see the Package Ordering Addendum at the end of this data sheet.

#### **PIN DESCRIPTIONS**

| PIN # | NAME                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1 | Input                      | The input is compatible with standard TTL levels. The device output becomes enabled when the input voltage is driven above the typical switching threshold, 1.7V. Below this level, the output is disabled. With no connection to the pin, the input level rises to 3.4V. Input current is $20\mu$ A when driven high and $80\mu$ A with the input low. The input may be driven to the power supply (V <sub>S</sub> ) without damage.                                                                                                                                                                                                                             |

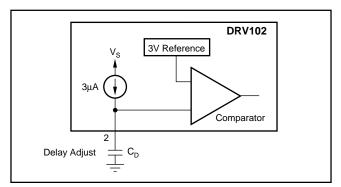

| Pin 2 | Delay Adjust               | This pin sets the duration of the initial 100% duty cycle before the output goes into PWM mode. Leaving this pin floating results in a delay of approximately 15 $\mu$ s, which is internally limited by parasitic capacitance. Minimum delay may be reduced to less than 3 $\mu$ s by tying the pin to 5V. This pin connects internally to a 3 $\mu$ A current source from V <sub>S</sub> and to a 3V threshold comparator. When the pin voltage is below 3V, the output device is 100% on. The PWM oscillator is not synchronized to the Input (pin 1), so the first pulse may be extended by any portion of the programmed duty cycle.                         |

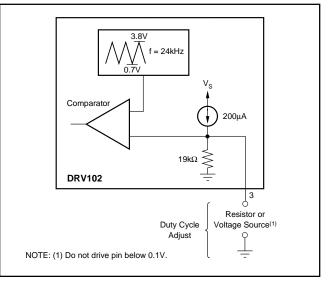

| Pin 3 | Duty Cycle Adjust<br>(PWM) | Internally, this pin connects to the input of a comparator and a $19k\Omega$ resistor to ground. It is driven by a $200\mu$ A current source from V <sub>S</sub> . The voltage at this node linearly sets the duty cycle. Duty cycle can be programmed with a resistor, analog voltage, or output of a D/A converter. The active voltage range is from 0.55V to 3.7V to facilitate the use of single-supply control electronics. At 0.56V (or R <sub>PWM</sub> = 4.4k $\Omega$ ), duty cycle is near 90%. Swing to ground should be limited to no lower than 0.1V. PWM frequency is a constant 24kHz.                                                             |

| Pin 4 | Ground                     | This pin is electrically connected to the package tab. It must be connected to system ground for the DRV102 to function. It carries the 6.5mA quiescent current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin 5 | Vs                         | This is the power supply pin. Operating range is +8V to +60V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin 6 | Out                        | The output is the emitter of a power npn with the collector connected to $V_s$ . Low power dissipation in the DRV102 is obtained<br>by low saturation voltage and fast switching transitions. Rise time is less than 250ns, fall time depends on load impedance.<br>A flyback diode is (D <sub>1</sub> ) needed with inductive loads to conduct the load current during the off cycle. The external diode should<br>be selected for low forward voltage. The internal clamp diode provides protection but should not be used to conduct load<br>currents. An additional diode (D <sub>2</sub> ), located in series with Out pin, is required for inductive loads. |

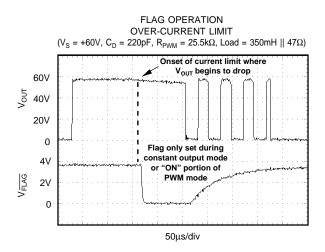

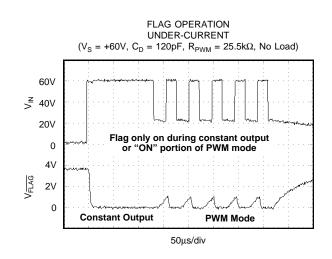

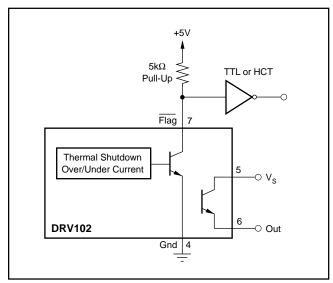

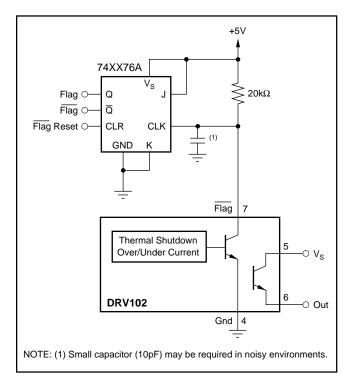

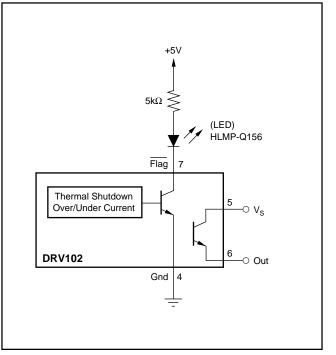

| Pin 7 | Flag                       | Normally high (active low), the Flag signals either an over-temperature, over-current, or under-current fault. The over/under-<br>current flags are true only when the output is on (constant dc output or the "on" portion of PWM mode). A thermal fault (thermal<br>shutdown) occurs when the die surface reaches approximately 165°C and latches until the die cools to 150°C. Its output<br>requires a pull-up resistor. It can typically sink two milliamps, sufficient to drive a low-current LED.                                                                                                                                                          |

#### LOGIC BLOCK DIAGRAM

## **TYPICAL PERFORMANCE CURVES**

At T<sub>C</sub> = +25°C and V<sub>S</sub> = +24V, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

At T<sub>C</sub> = +25°C and V<sub>S</sub> = +24V, unless otherwise noted.

50µs/div

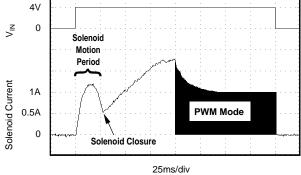

$(V_{S} = +60V, C_{D} = 0.1 \mu F, R_{PWM} = 30.1 k\Omega, Load = 350 mH)$

TYPICAL SOLENOID CURRENT WAVEFORM

# **TYPICAL PERFORMANCE CURVES (CONT)**

At T<sub>C</sub> = +25°C and V<sub>S</sub> = +24V, unless otherwise noted.

DELAY TIME TO PWM

DUTY CYCLE ACCURACY PRODUCTION DISTRIBUTION

# **BASIC OPERATION**

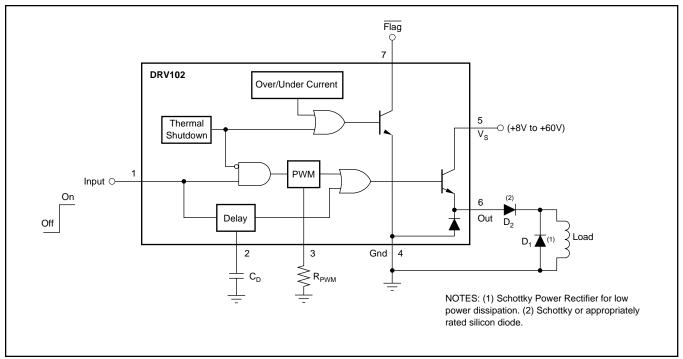

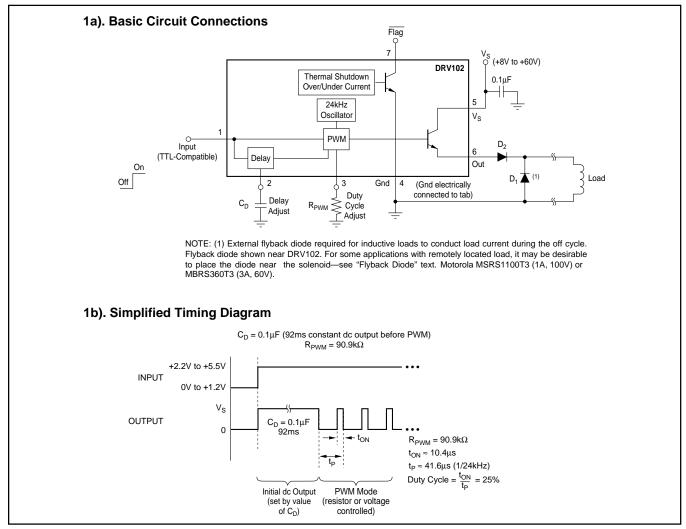

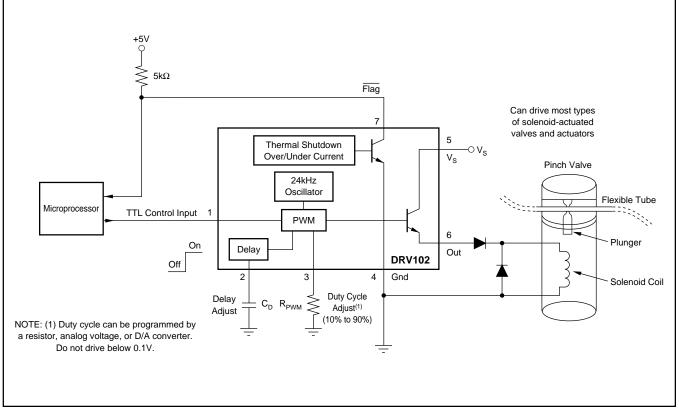

The DRV102 is a high-side, bipolar power switch employing a pulse-width modulated (PWM) output for driving electromechanical and thermal devices. Its design is optimized for two types of applications: a two-state driver (open/close) for loads such as solenoids and actuators, and a linear driver for valves, positioners, heaters, and lamps. Its wide supply range, adjustable delay to PWM mode, and adjustable duty cycle make it suitable for a wide range of applications. Figure 1 shows the basic circuit connections to operate the DRV102. A  $0.1\mu$ F bypass capacitor is shown connected to the power supply pin.

The Input (pin 1) is compatible with standard TTL levels. Input voltages between +2.2V and +5.5V turn the device output on, while pulling the pin low (0V to +1.2V), shuts the DRV102 output off. Input current is typically  $80\mu$ A.

Delay Adjust (pin 2) and Duty Cycle Adjust (pin 3) allow external adjustment of the PWM output signal. The Delay Adjust pin can be left floating for minimum delay to PWM mode (typically  $15\mu$ s) or a capacitor can be used to set the delay time. Duty cycle of the PWM output can be controlled by a resistor, analog voltage, or D/A converter. Figure 1b provides an example timing diagram with the Delay Adjust pin connected to  $0.1\mu$ F and duty cycle set for 25%. See the "Delay Adjust" and "Duty Cycle Adjust" text for equations and further explanation.

Ground (pin 4) is electrically connected to the package tab. This pin must be connected to system ground for the DRV102 to function. This serves as the DRV102 reference ground.

The load (solenoid, valve, etc.) is connected between the output (pin 6) and ground. For an inductive load, an external flyback diode ( $D_1$  in Figure 1a) across the output is required. The diode serves to maintain the hold force during PWM operation. Depending on the application, the flyback diode should be placed near the DRV102 or close to the solenoid (see "Flyback Diode" text). The device's internal clamp diode, connected between the output and ground, should not be used to carry load current. When driving inductive loads, an additional diode in series with the out pin,  $D_2$ , is required (see "Series Diode" text).

The  $\overline{\text{Flag}}$  (pin 7) provides fault status for under-current, over-current, and thermal shutdown conditions. This pin is active low with pin voltage typically +0.2V during a fault condition. A small value capacitor may be needed between  $\overline{\text{Flag}}$  and ground for noisy applications.

FIGURE 1. Basic Circuit Connections and Timing Diagram.

### **APPLICATIONS INFORMATION**

#### POWER SUPPLY

The DRV102 operates from a single +8V to +60V supply with excellent performance. Most behavior remains unchanged throughout the full operating voltage range. Parameters which vary significantly with operating voltage are shown in the Typical Performance Curves.

#### CONNECTIONS TO LOAD

The PWM switching voltage and currents can cause electromagnetic radiation. Proper physical layout of the load current will help minimize radiation. Load current flows from the DRV102 output terminal to the load and returns through the ground return path. This current path forms a loop. To minimize radiation, make the area of the enclosed loop as small as possible. Twisted pair leading to the load is excellent. If the ground return current must flow through a chassis ground, route the output current line directly over the chassis surface in the most direct path to the load.

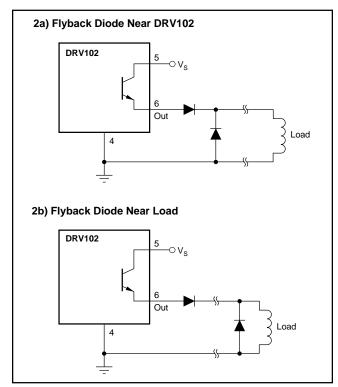

#### FLYBACK DIODE LOCATION

Physical location of the flyback diode may affect electromagnetic radiation. With most solenoid loads, inductance is large enough that load current is virtually constant during PWM operation. When the switching transistor is off, load current flows though the flyback diode. If the flyback diode is located near the DRV102 (Figure 2a), the current flowing in long lines to the load is virtually constant. If the flyback diode is, instead, located directly across the load (Figure 2b), pulses of current must flow from the DRV102 to the distant load. While theory seems to favor placing the diode at the DRV102 output (constant current in the long lines), indi-

vidual situations may defy logic; if one location seems to create noise problems, try the other.

#### SERIES DIODE FOR INDUCTIVE LOADS

An additional bias diode, located in series with the output, is required when driving inductive loads. Any silicon diode, such as the 1N4002, appropriately rated for current will work. The diode biases the emitter of the internal power device such that it can be fully shut off during the "off" portion of the PWM cycle. Note that the voltage at the load drops below ground due to the flyback diode. If it is not used, apparent leakage current can rise to hundreds of milliamps, resulting in unpredictable operation and thermal shutdown.

#### ADJUSTABLE INITIAL 100% DUTY CYCLE

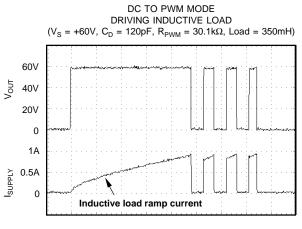

A unique feature of the DRV102 is its ability to provide an initial constant dc output (100% duty cycle) and then switch to PWM mode to save power. This function is particularly useful when driving solenoids which have a much higher pull-in current requirement than hold current requirement.

The duration of this constant dc output (before PWM output begins) can be externally and independently controlled with a capacitor connected from Delay Adjust (pin 2) to ground according to the following equation:

```

Delay Time \approx C_D \cdot 10^6

(time in seconds, C_D in Farads)

```

Leaving the Delay Adjust pin open results in a constant output time of approximately  $15\mu s$ . The duration of this initial output can be reduced to less than  $3\mu s$  by connecting the pin to 5V. Table I provides examples of desired "delay" times (constant output before PWM mode) and the appropriate capacitor values or pin connection.

| CONSTANT OUTPUT DURATION<br>(Delay Time to PWM Mode) | C <sub>D</sub>      |

|------------------------------------------------------|---------------------|

| 3μs                                                  | Pin Connected to 5V |

| 15μs                                                 | Pin Open            |

| 97μs                                                 | 100pF               |

| 0.97ms                                               | 1nF                 |

| 97ms                                                 | 0.1µF               |

TABLE I. Delay Adjust Pin Connections.

The internal Delay Adjust circuitry is composed of a  $3\mu A$  current source and a 3V comparator as shown in Figure 3. Thus, when the pin voltage is less than 3V, the output device is 100% on (dc output mode).

FIGURE 3. Simplified Circuit Model of the Delay Adjust Pin.

Texas

Instruments

www.ti.com

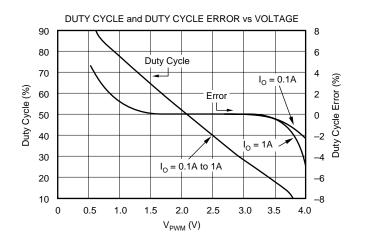

#### ADJUSTABLE DUTY CYCLE

The DRV102's externally adjustable duty cycle provides an accurate means of controlling power delivered to the load. Duty cycle can be set from 10% to 90% with an external resistor, analog voltage, or the output of a D/A converter. Reduced duty cycle results in reduced power dissipation. This keeps the DRV102 and load cooler, resulting in increased reliability for both devices. PWM frequency is a constant 24kHz.

#### **Resistor-Controlled Duty Cycle**

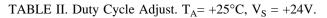

Duty cycle is independently programmed with a resistor  $(R_{PWM})$  connected between the Duty Cycle Adjust pin and ground. Increased resistor values correspond to decreased duty cycles. Table II provides resistor values for typical duty cycles. Resistor values for additional duty cycles can be obtained from Figure 4. For reference purposes, the equation for calculating  $R_{PWM}$  is included in Figure 4.

| DUTY CYCLE | RESISTOR <sup>(1)</sup><br>R <sub>PWM</sub> (kΩ) | VOLTAGE <sup>(2)</sup><br>V <sub>PWM</sub> (V) |

|------------|--------------------------------------------------|------------------------------------------------|

| 10         | 536                                              | 3.67                                           |

| 20         | 137                                              | 3.31                                           |

| 30         | 66.5                                             | 2.91                                           |

| 40         | 39.2                                             | 2.49                                           |

| 50         | 24.9                                             | 2.07                                           |

| 60         | 16.2                                             | 1.66                                           |

| 70         | 10.5                                             | 1.26                                           |

| 80         | 6.65                                             | 0.88                                           |

| 90         | 4.42                                             | 0.56                                           |

NOTES: (1) Resistor values listed are nearest 1% standard values. (2) Do not drive pin below 0.1V. For additional values, see "Duty Cycle vs Voltage" typical performance curve.

FIGURE 4. R<sub>PWM</sub> versus Duty Cycle.

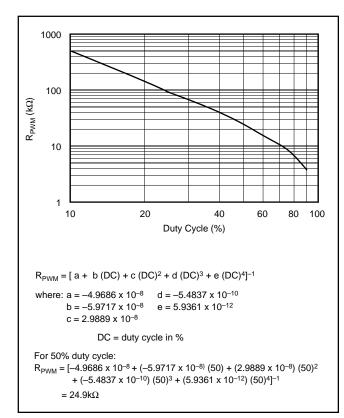

#### Voltage-Controlled Duty Cycle

Duty cycle can also be programmed with an analog voltage,  $V_{PWM}$ . With  $V_{PWM} \approx 0.5V$ , duty cycle is 100%. Increasing this voltage results in decreased duty cycles. For 0% duty cycle,  $V_{PWM}$  is approximately 4V. Table II provides  $V_{PWM}$  values for typical duty cycles. See the "Duty Cycle vs Voltage" typical performance curve for additional duty cycle values.

The Duty Cycle Adjust pin should not be driven below 0.1V. If the voltage source used can go between 0.1V and ground, a  $1k\Omega$  series resistor between the voltage source and the Duty Cycle Adjust pin (Figure 5) is required to limit swing. If the pin is driven below 0.1V, the output will be unpredictable.

FIGURE 5. Using a Voltage Source to Program Duty Cycle.

The DRV102's internal 24kHz oscillator sets the PWM period. This frequency is not externally adjustable. Duty Cycle Adjust (pin 3) is internally driven by a 200 $\mu$ A current source and connects to the input of a comparator and a 19k $\Omega$  resistor as shown in Figure 6. The DRV102's PWM control design is inherently monotonic. That is, a decreased voltage (or resistor value) always produces an increased duty cycle.

FIGURE 6. Simplified Circuit Model of the Duty Cycle Adjust Pin.

**IEXAS**

www.ti.com

INSTRUMENTS

#### STATUS FLAG

Flag (pin 7) provides fault indication for under-current, over-current, and thermal shutdown conditions. During a fault condition, Flag output is driven low (pin voltage typically drops to 0.2V). A pull-up resistor, as shown in Figure 7, is required to interface with standard logic. A small value capacitor may be needed between Flag and ground in noisy applications.

Figure 7 gives an example of a non-latching fault monitoring circuit, while Figure 8 provides a latching version. The Flag pin can sink several milliamps, sufficient to drive external logic circuitry or an LED (Figure 9) to indicate when a fault has occurred. In addition, the Flag pin can be used to turn off other DRV102's in a system for chain fault protection.

FIGURE 7. Non-Latching Fault Monitoring Circuit.

FIGURE 9. LED to Indicate Fault Condition.

#### **Over/Under Current Fault**

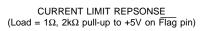

An over-current fault occurs when the output current exceeds the current limit. All units are guaranteed to drive 2A without current limiting. Typically, units will limit at 2.7A. The status flag is not latched. Since current during PWM mode is switched on and off, the flag output will be modulated with PWM timing (see flag waveforms in the Typical Performance Curves).

An under-current fault occurs when the output current is below the under-scale current threshold (typically 16mA). For example, this function indicates when the load is disconnected. Again, the flag output is not latched, so an undercurrent condition during PWM mode will produce a flag output that is modulated by the PWM waveform. An initial, brief under-current flag normally appears driving inductive loads and may be avoided by adding a parallel resistor sufficient to move the initial current above the under-current threshold. Avoid adding capacitance to pin 6 (Out) as it may cause momentary current limiting.

#### **Over-Temperature Fault**

A thermal fault occurs when the die reaches approximately 165°C, producing a similar effect as pulling the input low. Internal shutdown circuitry disables the output and resets the Delay Adjust pin. The Flag is latched in the low state (fault condition) until the die has cooled to approximately 150°C. A thermal fault can occur in any mode of operation. Recovery from thermal fault will start in delay mode (constant dc output).

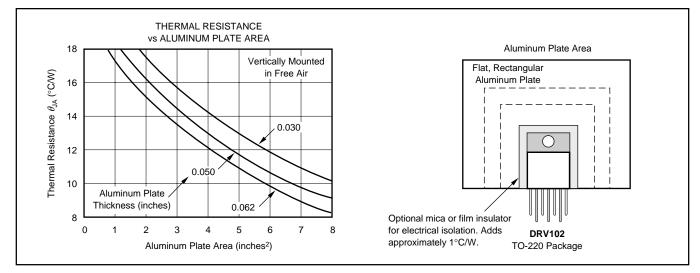

#### PACKAGE MOUNTING

Figure 10 provides recommended PCB layouts for both the TO-220 and DDPAK power packages. The tab of both packages is electrically connected to ground (pin 4). It may be desirable to isolate the tab of TO-220 package from its mounting surface with a mica (or other film) insulator (see Figure 11). For lowest overall thermal resistance, it is best to isolate the entire heat sink/DRV102 structure from the mounting surface rather than to use an insulator between the semiconductor and heat sink.

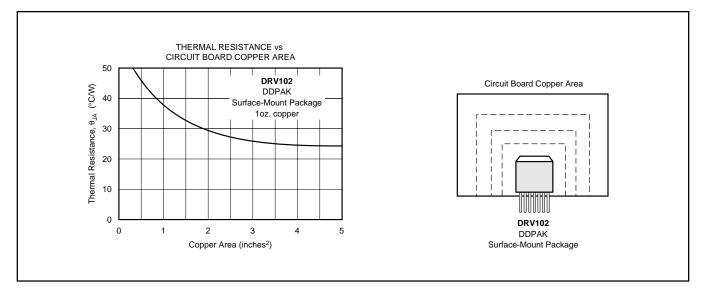

For best thermal performance, the tab of the DDPAK surface-mount version should be soldered directly to a circuit board copper area. Increasing the copper area improves heat dissipation. Figure 12 shows typical thermal resistance from junction-to-ambient as a function of the copper area.

#### POWER DISSIPATION

Power dissipation depends on power supply, signal, and load conditions. Power dissipation is equal to the product of

FIGURE 10. TO-220 and DDPAK Solder Footprints.

FIGURE 11. TO-220 Thermal Resistance versus Aluminum Plate Area.

FIGURE 12. DDPAK Thermal Resistance versus Circuit Board Copper Area.

output current times the voltage across the conducting output transistor times the duty cycle. Power dissipation can be minimized by using the lowest possible duty cycle necessary to assure the required hold force.

#### THERMAL PROTECTION

Power dissipated in the DRV102 will cause the junction temperature to rise. The DRV102 has thermal shutdown circuitry that protects the device from damage. The thermal protection circuitry disables the output when the junction temperature reaches approximately +165°C, allowing the device to cool. When the junction temperature cools to approximately +150°C, the output circuitry is again enabled. Depending on load and signal conditions, the thermal protection circuit may cycle on and off. This limits the dissipation of the driver but may have an undesirable effect on the load.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heat sink. For reliable operation, junction temperature should be limited to  $+125^{\circ}$ C, maximum. To estimate the margin of safety in a complete design (including heat sink), increase the ambient temperature until the thermal protection is triggered. Use worst-case load and signal conditions. For good reliability, thermal protection should trigger more than  $40^{\circ}$ C above the maximum expected ambient condition of your application. This produces a junction temperature of  $125^{\circ}$ C at the maximum expected ambient condition.

The internal protection circuitry of the DRV102 was designed to protect against overload conditions. It was not intended to replace proper heat sinking. Continuously running the DRV102 into thermal shutdown will degrade reliability.

#### **HEAT SINKING**

Most applications will not require a heat sink to assure that the maximum operating junction temperature (125°C) is not exceeded. However, junction temperature should be kept as low as possible for increased reliability. Junction temperature can be determined according to the equation:

$$T_{\rm J} = T_{\rm A} + P_{\rm D}\theta_{\rm JA} \tag{1}$$

where,

$$\theta_{JA} = \theta_{JC} + \theta_{CH} + \theta_{HA}$$

(2)

- $T_J$  = Junction Temperature (°C)

- $T_A$  = Ambient Temperature (°C)

- $P_D$  = Power Dissipated (W)

- $\theta_{\rm JC}$  = Junction-to-Case Thermal Resistance (°C/W)

- $\theta_{CH}$  = Case-to-Heat Sink Thermal Resistance (°C/W)

- $\theta_{HA}$  = Heat Sink-to-Ambient Thermal Resistance (°C/W)

- $\theta_{JA}$  = Junction-to-Air Thermal Resistance (°C/W)

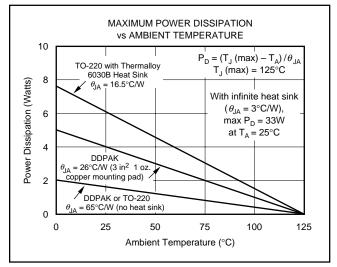

Figure 13 shows maximum power dissipation versus ambient temperature with and without the use of a heat sink. Using a heat sink significantly increases the maximum power dissipation at a given ambient temperature as shown.

FIGURE 13. Maximum Power Dissipation versus Ambient Temperature.

The difficulty in selecting the heat sink required lies in determining the power dissipated by the DRV102. For dc output into a purely resistive load, power dissipation is simply the load current times the voltage developed across the conducting output transistor times the duty cycle. Other loads are not as simple. Once power dissipation for an application is known, the proper heat sink can be selected.

#### **Heat Sink Selection Example**

A TO-220 package's maximum dissipation is 2 Watts. The maximum expected ambient temperature is  $80^{\circ}$ C. Find the proper heat sink to keep the junction temperature below  $125^{\circ}$ C.

Combining Equations 1 and 2 gives:

$$T_{\rm J} = T_{\rm A} + P_{\rm D}(\theta_{\rm JC} + \theta_{\rm CH} + \theta_{\rm HA})$$

(3)

T<sub>J</sub>, T<sub>A</sub>, and P<sub>D</sub> are given.  $\theta_{JC}$  is provided in the Specifications table, 3°C/W.  $\theta_{CH}$  can be obtained from the heat sink manufacturer. Its value depends on heat sink size, area, and material used. Semiconductor package type, mounting screw torque, insulating material used (if any), and thermal joint compound used (if any) also affect  $\theta_{CH}$ . A typical  $\theta_{CH}$  for a TO-220 mounted package is 1°C/W. Now we can solve for  $\theta_{HA}$ :

$$\theta_{\rm HA} = \frac{{\rm T}_{\rm J} - {\rm T}_{\rm A}}{{\rm P}_{\rm D}} - \left(\theta_{\rm JC} + \theta_{\rm CH}\right)$$

(4)

$$\theta_{\rm HA} = \frac{125^{\circ}{\rm C} - 80^{\circ}{\rm C}}{2{\rm W}} - \left(3^{\circ}{\rm C}/{\rm W} + 1^{\circ}{\rm C}/{\rm W}\right) = 18.5^{\circ}{\rm C}/{\rm W}$$

To maintain junction temperature below  $125^{\circ}$ C, the heat sink selected must have a  $\theta_{HA}$  less than  $18.5^{\circ}$ C/W. In other words, the heat sink temperature rise above ambient must be less than  $37^{\circ}$ C ( $18.5^{\circ}$ C/W • 2W). For example, at 2 Watts Thermalloy model number 6030B has a heat sink temperature rise of about  $33^{\circ}$ C above ambient, which is below the  $37^{\circ}$ C required in this example. Figure 13 shows power dissipation versus ambient temperature for a TO-220 package with a 6030B heat sink.

Another variable to consider is natural convection versus forced convection air flow. Forced-air cooling by a small fan can lower  $\theta_{CA}$  ( $\theta_{CH} + \theta_{HA}$ ) dramatically. Heat sink manufacturers provide thermal data for both of these cases. For additional information on determining heat sink requirements, consult Application Bulletin AB-038.

As mentioned earlier, once a heat sink has been selected, the complete design should be tested under worst-case load and signal conditions to ensure proper thermal protection.

## **APPLICATION CIRCUITS**

FIGURE 14. Fluid Flow Control System.

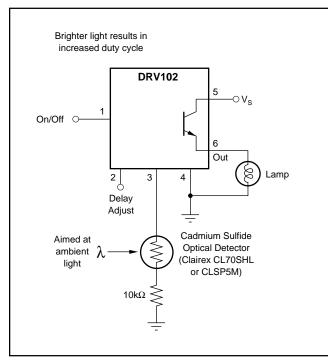

FIGURE 15. Instrument Light Dimmer Circuit.

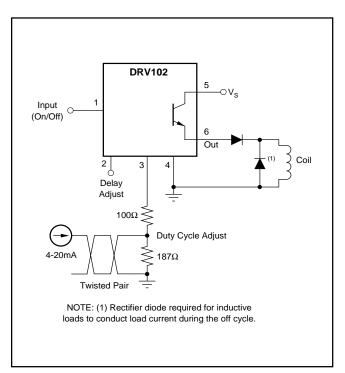

FIGURE 16. 4-20mA Input to PWM Output.

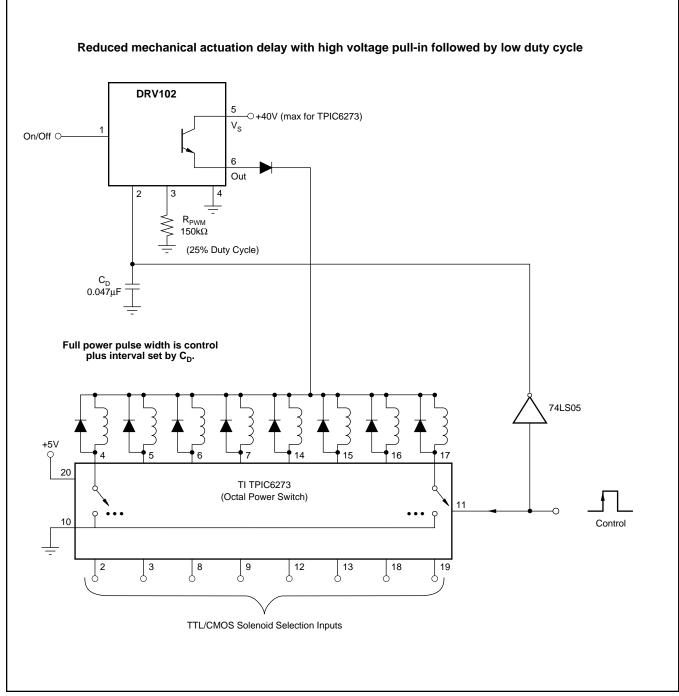

FIGURE 17. Improved Switching Time When Driving Multiple Loads.

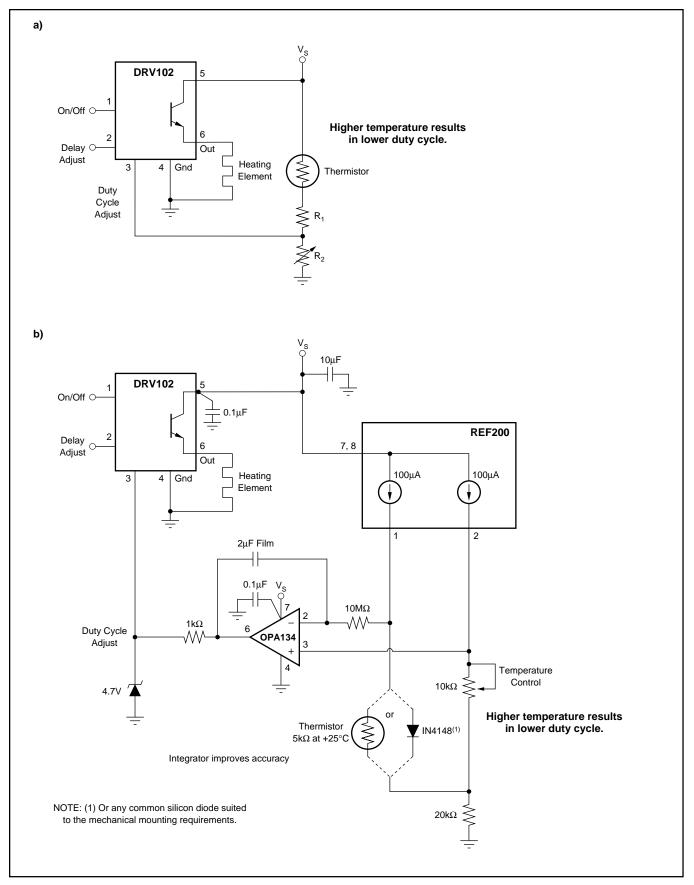

FIGURE 18. (a) Constant Temperature Controller. (b) Improved Accuracy Constant Temperature Controller.

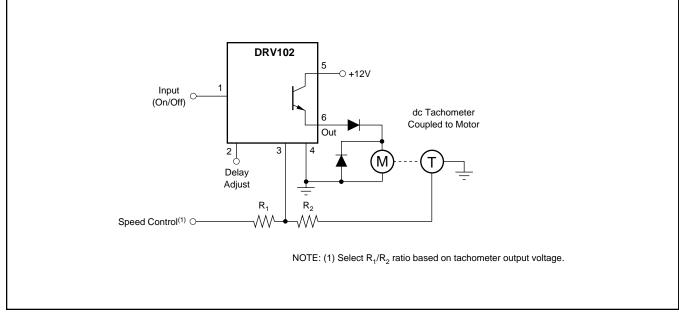

FIGURE 19. Constant Speed Motor Control.

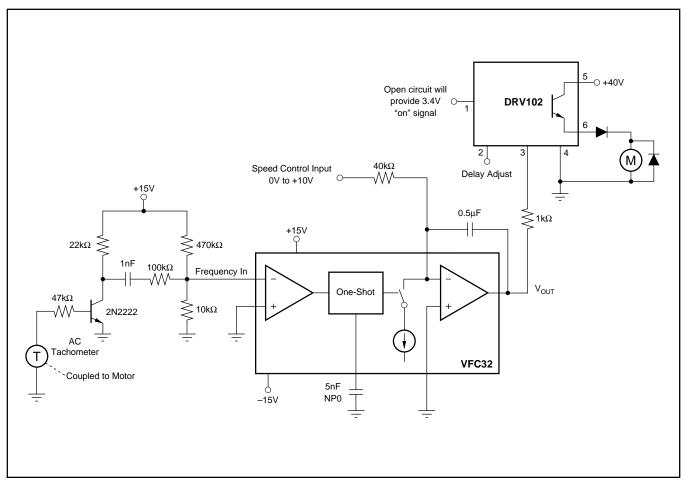

FIGURE 20. DC Motor Speed Control Using AC Tachometer.

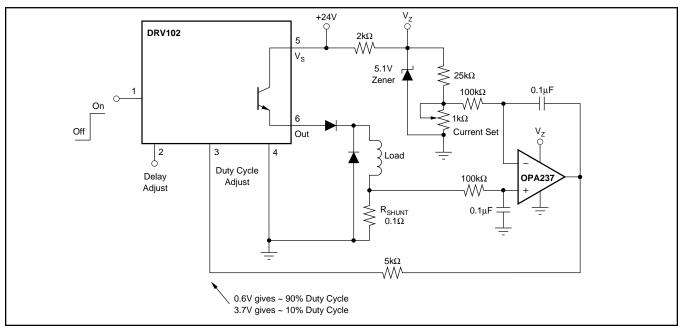

FIGURE 21. Constant Current Output Drive.

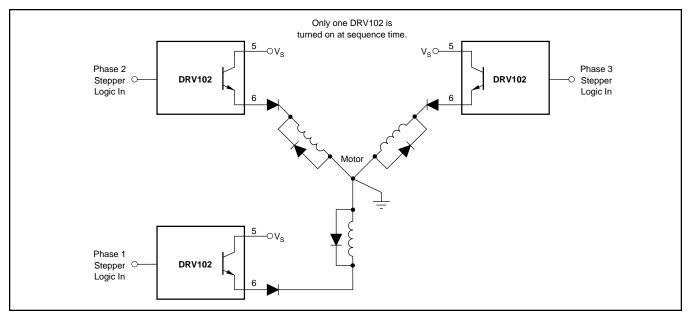

FIGURE 22. Three-Phase Stepper Motor Driver Provides High-Stepping Torque.

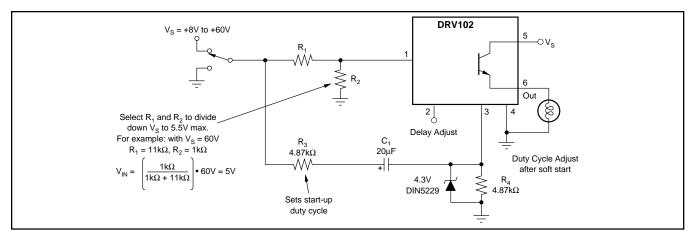

FIGURE 23. Soft-Start Circuit for Incandescent Lamps and Other Sensitive Loads.

### **Revision History**

| DATE | REVISION | PAGE | SECTION          | DESCRIPTION                                      |

|------|----------|------|------------------|--------------------------------------------------|

| 5/09 | Р        | 1    | Front Page       | Updated front page appearance.                   |

| 5/09 | Б        | 12   | Package Mounting | Changed Figure 10 to show TI package designator. |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish<br>(6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|------------------|--------------------|------|----------------|----------------------------|-------------------------|---------------------|--------------|-------------------------|---------|

| DRV102F/500      | ACTIVE        | DDPAK/<br>TO-263 | KTW                | 7    | 500            | Green (RoHS<br>& no Sb/Br) | CU SN                   | Level-2-260C-1 YEAR | -55 to 125   | DRV102F                 | Samples |

| DRV102FKTWT      | ACTIVE        | DDPAK/<br>TO-263 | KTW                | 7    | 250            | Green (RoHS<br>& no Sb/Br) | CU SN                   | Level-3-245C-168 HR | -55 to 125   | DRV102F                 | Samples |

| DRV102FKTWTG3    | ACTIVE        | DDPAK/<br>TO-263 | KTW                | 7    | 250            | Green (RoHS<br>& no Sb/Br) | CU SN                   | Level-3-245C-168 HR | -55 to 125   | DRV102F                 | Samples |

| DRV102T          | ACTIVE        | TO-220           | KVT                | 7    | 50             | Green (RoHS<br>& no Sb/Br) | CU SN                   | N / A for Pkg Type  | -55 to 125   | DRV102T                 | Samples |

| DRV102TG3        | ACTIVE        | TO-220           | KVT                | 7    | 50             | Green (RoHS<br>& no Sb/Br) | CU SN                   | N / A for Pkg Type  | -55 to 125   | DRV102T                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

28-Oct-2017

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

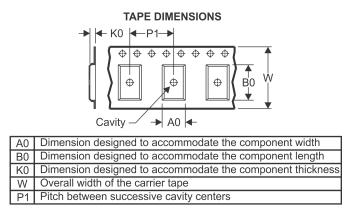

#### TAPE AND REEL INFORMATION

\*All dimensions are nominal

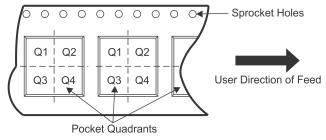

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device      | •                | Package<br>Drawing |   | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|------------------|--------------------|---|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV102F/500 | DDPAK/<br>TO-263 | KTW                | 7 | 500 | 330.0                    | 24.4                     | 10.95      | 16.5       | 5.15       | 16.0       | 24.0      | Q2               |

| DRV102FKTWT | DDPAK/<br>TO-263 | KTW                | 7 | 250 | 330.0                    | 24.4                     | 10.6       | 15.6       | 4.9        | 16.0       | 24.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

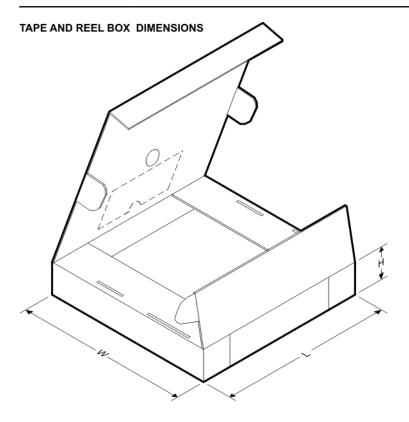

### PACKAGE MATERIALS INFORMATION

15-Sep-2017

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| DRV102F/500 | DDPAK/TO-263 | KTW             | 7    | 500 | 346.0       | 346.0      | 41.0        |

| DRV102FKTWT | DDPAK/TO-263 | KTW             | 7    | 250 | 367.0       | 367.0      | 45.0        |

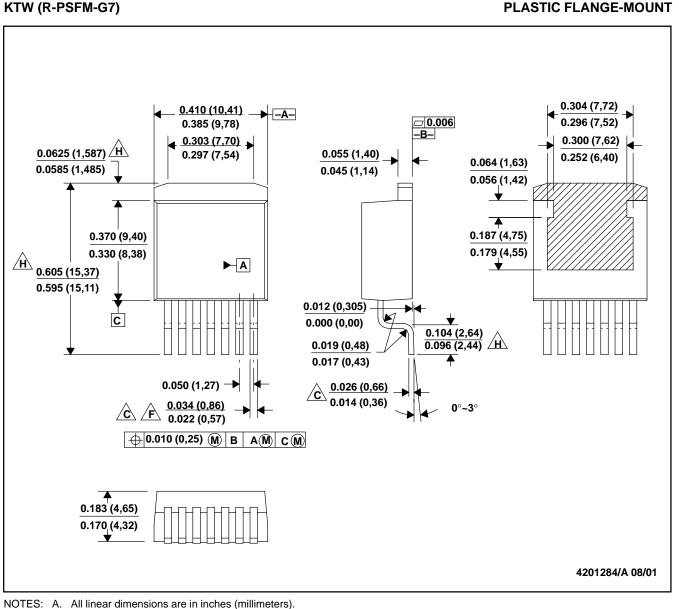

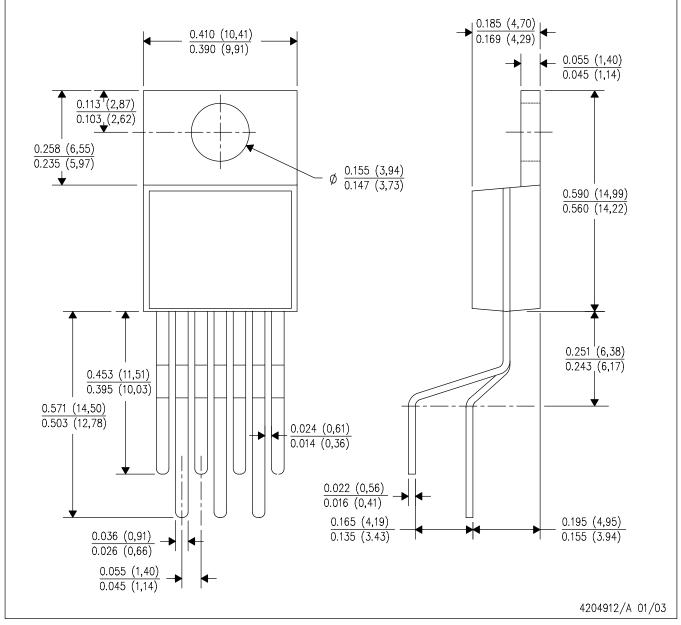

### **MECHANICAL DATA**

MPSF015 - AUGUST 2001

S: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

- C. Lead width and height dimensions apply to the plated lead.

- D. Leads are not allowed above the Datum B.

- E. Stand–off height is measured from lead tip with reference to Datum B.

- F. Lead width dimension does not include dambar protrusion. Allowable dambar protrusion shall not cause the lead width to exceed the maximum dimension by more than 0.003".

- G. Cross-hatch indicates exposed metal surface.

- A Falls within JEDEC MO–169 with the exception of the dimensions indicated.

KVT (R-PZFM-T7)

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated