# 62EM1-Programmable 62mm Electrical Series

# **Optimized for Silicon Carbide (SiC) MOSFET Modules**

#### **Overview**

The AgileSwitch 62EM1-62mm Electrical driver provides monitoring and fault reporting information to enable better control and analysis of SiC MOSFET-based power systems. The 62EM1 provides up to 20 Amps of peak current at an operating frequency up to 200 kHz. The driver includes isolated HI and LO Side DC/DC converters and provides 7 fault conditions that are reported as a combination of the 3 fault lines via the 20 pin control header. All AgileSwitch drivers use automotive temperature grade components and allow for modifying settings of gate resistors.

## **Software Programmable Features**

- Augmented Turn-Off<sup>TM</sup> (ATOff) (Patented)

- Power supply under-voltage lockout (UVLO)

- Power supply over-voltage lockout (OVLO)

- Desaturation detection settings

- Dead time

- Fault lockout settings

- Automatic Reset settings

# **Applications**

- High Speed Trains/Traction

- Motor Drives

- HEV/EV

- Induction Welding, Cutting and Heating

- Solar/PV inverters

- Wind Turbines

- UPS

- Frequency Conversion

## **Key Switch Driver Features**

- UL Complaint 1200V & 1700V SiC

- Single-ended (5V, 15V) or Differential (RS-422 Compatible) logic

- Temperature Monitoring, PWM

- Isolated High Voltage Monitoring, PWM

- 2 X 10W output power

- RoHs compliant

- Configurable Gate Output Voltages

- Up to 7 Unique Fault Conditions

# **System Overview**

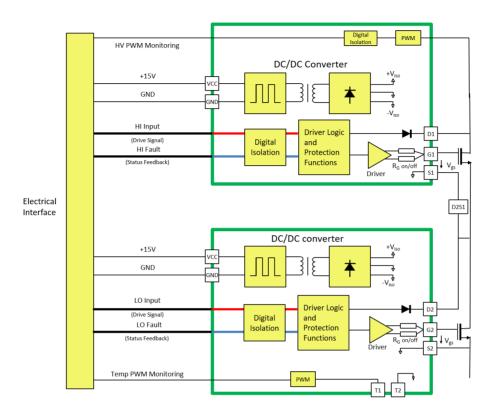

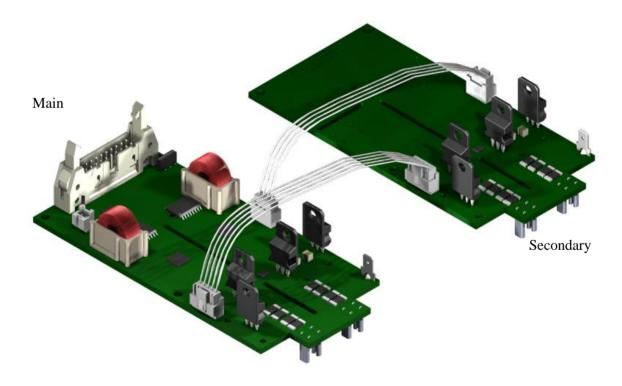

The basic topology of the driver is shown in Figure 1.

Figure 1: Basic schematic of the 62EM1-62mm Electrical Gate Driver

# **Absolute Maximum Ratings**

Interaction of maximum ratings is dependent on operating conditions

| Parameter             | Description                                  | Min  | Max       | Unit  |

|-----------------------|----------------------------------------------|------|-----------|-------|

| Supply Voltage        | VCC to GND                                   | 0    | 18        | V     |

| Peak Gate Current     | Note 1                                       | -20  | 20        | A     |

| Input Logic Levels    | To GND                                       | -0.5 | 16        | V     |

| Output Power per Gate |                                              |      | 10.0      | W     |

| Switching Frequency   | Note 2                                       |      | 200       | kHz   |

| Isolation Voltage     | Primary to Secondary VDC, 1 min              |      | 4500      | V     |

| Working Voltage       | Primary to Secondary, Secondary to Secondary |      | 1200/1700 | V     |

| Creepage Distance     | Primary to Secondary Side                    | 12   |           | mm    |

| dV/dt*                | Rate of change input to output               | 100  |           | kV/μs |

| Operating Temperature | Ambient Operating Temperature                | -40  | +85       | °C    |

| Storage Temperature   |                                              | -40  | +90       | °C    |

### **Electrical Characteristics**

Conditions:  $V_{SUP} = +15.0 \text{ V}, V_{IN\_LOGIC}$

= 15V or 5V, MOSFET = CAS300M12BM2

| Power Supply                          | Description                                              | Min  | Тур       | Max  | Unit |

|---------------------------------------|----------------------------------------------------------|------|-----------|------|------|

| Supply Voltage                        | VCC to GND                                               |      | 15        | 16   | V    |

| Supply Current                        | Without Load                                             |      | 110       |      | mA   |

| Supply Current                        | With Load, Note 3                                        |      |           | 1250 | mA   |

| UVLO Level-HI and LO*                 | Primary Side low voltage detect fault level              | 13.5 | 14        |      | V    |

| UVLO Level-HI and LO*                 | Secondary Side low voltage detect fault level,<br>Note 3 | 20   |           |      | V    |

| OVLO Level-HI and LO*                 | Primary Side high voltage detect fault level             |      | 16        | 16.5 | V    |

| V <sub>SOFT</sub> *                   | 2-Level Turn Off, Note 3                                 |      | 1.5       |      | V    |

| V <sub>soft</sub> D1*                 | DSAT 1st Level Turn Off Voltage, Note 3                  |      | 9         |      | V    |

| V <sub>soft</sub> D2*                 | DSAT 2 <sup>nd</sup> Level Turn Off Voltage, Note 3      |      | 5         |      | V    |

| Signal I/O                            | Description                                              | Min  | Тур       | Max  | Unit |

| Input Impedance                       | 5V - HI and LO side input                                |      | 500       |      | Ω    |

|                                       | 15V - HI and LO side input                               |      | 3000      |      | Ω    |

|                                       | 5V Differential – HI and LO side input                   |      | 1000      |      | Ω    |

| V <sub>IN</sub> Low                   | 5V - Turn-off threshold                                  |      |           | 1.25 | V    |

|                                       | 15V - Turn-off threshold                                 |      |           | 4    | V    |

| V <sub>IN</sub> High                  | 5V – Turn-on Threshold                                   | 3.5  |           |      | V    |

|                                       | 15V - Turn-on threshold                                  | 10   |           |      | V    |

| V <sub>IN</sub> (differential option) | Difference between VIN+ to VIN-                          | 2    |           |      | V    |

| Gate Output Voltage Low               | Note 3                                                   | -6   |           | -4   | V    |

| Gate Output Voltage High              | Note 3                                                   | +17  |           | +21  | V    |

| Fault Output Voltage                  | Fault lines are open collect with 5mA load               | 0.3  |           |      | V    |

| Fault Output Current                  | Note 4                                                   |      |           | 10   | mA   |

| Switching Frequency                   | Note 2                                                   |      |           | 200  | kHz  |

| DC Link & Temp Monitoring             | High Voltage (HV) & Temp Monitoring<br>Output            | 0    |           | 5    | V    |

| DC Link & Temp Monitoring             | PWM Frequency                                            |      | 31.5      |      | kHz  |

| DC Link & Temp Monitoring             | Output Impedance                                         |      | 510<br>1% |      | Ω    |

| DC Link Voltage                       |                                                          | 880  |           | 920  | V    |

| Temperature Trip                      |                                                          |      | 125       |      | °C   |

| <b>MOSFET Short Protection</b>        | Description                                              | Min  | Тур       | Max  | Unit |

| Desat Monitor Voltage*                | Between Drain and Sink of MOSFET, Note 3                 |      | 8.25      |      | V    |

| $T_{DSAT}^*$                          | Activation after MOSFET Turn on                          |      | 1.5       |      | μs   |

| Response Time after Fault             |                                                          |      |           | 200  | ns   |

Note 1: Input signal should not be activated until 20 ms after power is applied to allow on board DC-DC converter to stabilize.

Note 2: Actual maximum switching speed is a function of gate capacitance.

Note 3: SiC MOSFET dependant, conditions listed above assume CAS300M12BM2

Note 4: Fault lines are open collector and require a pull-up resistor,  $2K\Omega$  recommended

<sup>\*</sup> Software configurable parameter

# 62EM1 – Programmable 62mm Electrical Series PRELIMINARY

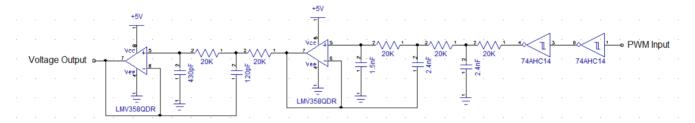

Temperature and High Voltage PWM Monitoring: The AgileSwitch 62EM1 Driver provides two 31.5 kHz, 5.0V PWM output signals that monitor the thermistor temperature (non-isolated) and the DC Link Voltage(isolated) (High Side drain to Low Side source) of the SiC MOSFET power module. The PWM signals have an output impedance of  $510\Omega$ . When combined with an external low pass filter, these signals represent a real time, isolated voltage for both High Voltage and Thermistor Temperature. A Sallen-Key active low pass filter can be used with these outputs as shown below with a 2 kHz cut-off frequency. The cut-off frequency can be optimized for your application. For simplicity, a simple RC low pass filter with 100 Hz cut-off frequency can also be used.

Figure 2: Example of external 2 kHz low pass filter

#### **Interconnects**

#### **Controller/Power to Driver Connectors**

| Connector      | Type   | Ref | Manufacturer Part Number |

|----------------|--------|-----|--------------------------|

| Driver Board   | 20 Pin | J1  | FCI 71918-220LF          |

| Cable Assembly | 20 Pin |     | FCI 71600-120LF          |

Recommended Cable for High Noise Environments: Flat Ribbon Cable, Twisted Pair, Shielded (3M 1785/20 Series)

#### Main to Secondary Driver Connectors (Optional – Please specify if required, otherwise not populated)

| Connector      | Type  | Ref | Manufacturer Part Number |

|----------------|-------|-----|--------------------------|

| Driver Board   | 5 Pin | J6  | JST B05B-PASK-1          |

| Cable Assembly | 5 Pin |     | JST PAP-05V-S            |

| Driver Board   | 4 Pin | J7  | JST B04B-PASK-1          |

| Cable Assembly | 4 Pin |     | JST PAP-04V-S            |

#### **Thermistor Connector**

| Connector      | Type  | Ref | Manufacturer Part Number |

|----------------|-------|-----|--------------------------|

| Driver Board   | 2 Pin | J5  | JST B02B-PASK-1          |

| Cable Assembly | 2 Pin |     | JST PAP-02V-S            |

Standard part is a vertical 2 pin header. Right-angle 2 pin header available upon request (P/N: JST S02B-PASK-2)

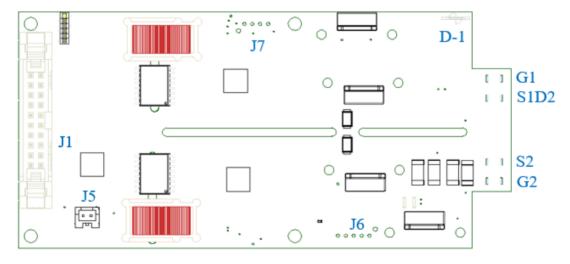

#### **MOSFET Terminals**

| Ref ID           | Type            | Manufacturer Part Number |

|------------------|-----------------|--------------------------|

| G1, G2, S2, S1D2 | 2.8mm Quick Fit | Keystone 3534            |

| D1*              | 4.8mm Quick Fit | Keystone 1285-ST         |

<sup>\*</sup>Recommended Mate for D1 – Keystone 8291 (Female Fully Insulated Quick Fit Terminal)

<sup>\*</sup>D1 Quick Fit terminal on gate driver must be connected to the D1 terminal on the SiC MOSFET module.

Figure 3: Interconnect Locations on PCB

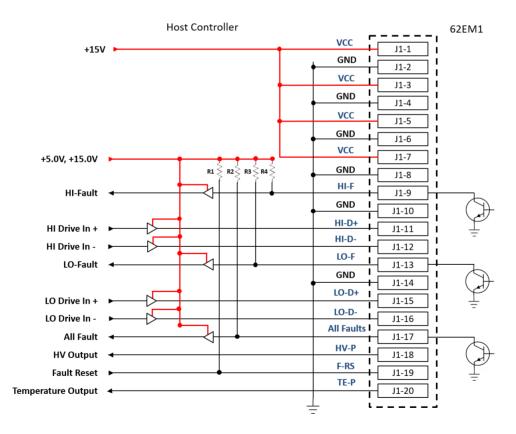

#### inout - Controller/Power to Driver Connection

#### 20 PIN - J1

| Pin No | Signal                                      | Pin No | Signal                                  |

|--------|---------------------------------------------|--------|-----------------------------------------|

| 1      | VCC – +15V Supply Voltage                   | 2      | GND                                     |

| 3      | VCC – +15V Supply Voltage                   | 4      | GND                                     |

| 5      | VCC – +15V Supply Voltage                   | 6      | GND                                     |

| 7      | VCC – +15V Supply Voltage                   | 8      | GND                                     |

| 9      | HI-F – HI-Fault                             | 10     | GND                                     |

| 11     | HI-D (+) HI Drive In (+)                    | 12     | HI-D (-) HI Drive In (-) or GND         |

| 13     | LO-F - LO Fault                             | 14     | GND                                     |

| 15     | LO-D (+) LO Drive In (+)                    | 16     | LO-D (-) LO Drive In (-) or GND         |

| 17     | AL-F – All Faults (Low when HI-F or LO-F)   | 18     | HV-P – Isolated High Voltage Monitoring |

| 19     | F-RS – Fault Reset (Auto Reset<br>Optional) | 20     | TE-P – Temperature Monitoring           |

#### **Recommended Interface Circuitry**

Figure 3: 20 pin pinout diagram for 62EM1-62mm Electrical Gate Driver

#### Pinout - Main to Secondary Driver Connectors

#### 4 PIN – J7

| Pin No | Signal                   |

|--------|--------------------------|

| 1      | Positive Supply Voltage* |

| 2      | HI Drive In              |

| 3      | Negative Supply Voltage* |

| 4      | GND                      |

#### 5 PIN – J6

| Pin No | Signal                   |

|--------|--------------------------|

| 1      | Positive Supply Voltage* |

| 2      | LO Drive In              |

| 3      | Negative Supply Voltage* |

| 4      | GND                      |

| 5      | NC – No Connect          |

<sup>\*</sup>Positive and Negative Supply Voltages provided by Main Gate Driver to the Secondary Gate Driver

Figure 5: Typical Main-Secondary Setup

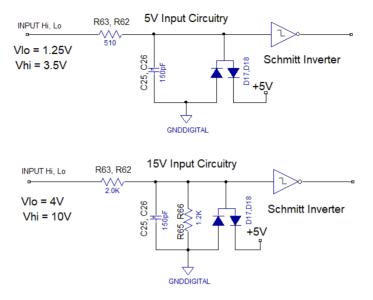

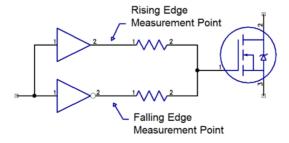

#### **Buffer Schematic for Single Ended Inputs on 62EM1**

Figure 6: Input buffers on 62EM1; schematics for 5V and 15V logic

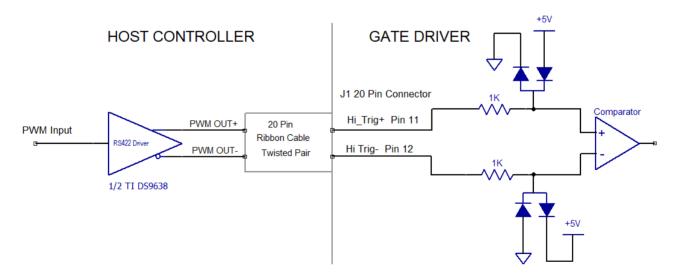

#### **Buffer Schematic for Differential Inputs on 62EM1**

Figure 7: Input buffer schematic - differential input

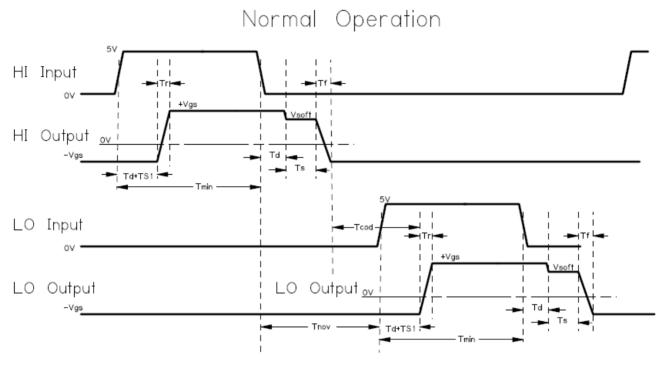

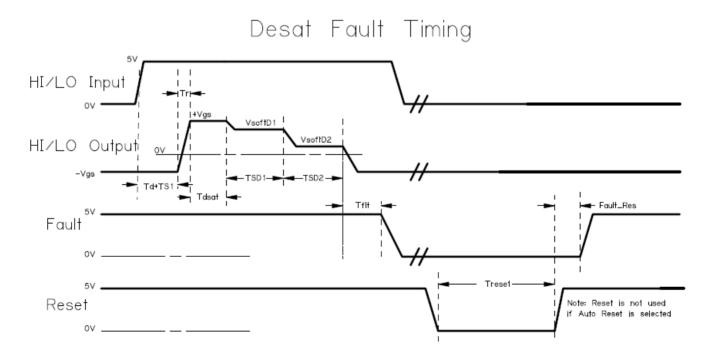

# **Timing Diagrams**

Figure 8: Signal input and output timing diagram.

Figure 9: Signal desaturation and fault timing diagram.

#### **Timing Diagram Values**

Conditions:  $V_{SUP}$  = +15.0 V,  $V_{IN\_LOGIC}$  = 15V or 5V, MOSFET = CAS300M12B2, Temp = 0 °C to 85 °C

| Description                   | Symbol           | Min  | Тур  | Max  | Unit | Notes                                                                       |

|-------------------------------|------------------|------|------|------|------|-----------------------------------------------------------------------------|

| Minimum Pulse<br>Width        | $T_{MIN}$        | 1000 |      |      | ns   |                                                                             |

| Delay Time                    | $T_D$            |      |      | 250  | ns   |                                                                             |

| De-Glitch Time                |                  |      | 200  |      | ns   | Input signal de-glitch time                                                 |

| Rise Time                     | $T_R$            |      | 80   |      | ns   | Measured from 10% to 90% points on edge Measurement Point 1 – Fig. 10       |

| Fall Time                     | $T_{\mathrm{F}}$ |      | 90   |      | ns   | Measured from 10% to 90% points on edge Measurement Point 2 – Fig. 10       |

| 2-Level Turn-Off<br>Time      | $T_{S1}$         |      | 360  |      | ns   | Software configurable                                                       |

| 2-Level Turn-Off<br>Voltage   | Vsoft            |      | 1.5  |      | V    | Software configurable                                                       |

| Desaturation Time             | $T_{DSAT}$       | 1400 | 1500 | 1600 | ns   | Software configurable                                                       |

| 1 <sup>st</sup> DSAT V        | Vsoft D1         |      | 9    |      | V    | Multi-Level Turn-Off – First DSAT<br>Step                                   |

| First DSAT Time*              | TSD1             |      | 400  |      | ns   | First DSAT 2-level turn-off time                                            |

| 2 <sup>nd</sup> DSAT V        | Vsoft D2         |      | 5    |      | V    | Multi-Level Turn-Off – Second DSAT<br>Step                                  |

| Second DSAT Time*             | TSD2             |      | 200  |      | ns   | Second DSAT 2-level turn-off time                                           |

| Fault Time Delay              | $T_{FLT}$        |      | 5000 |      | ns   |                                                                             |

| Fault Reset                   | Fault_Res        |      | 1000 |      | ns   |                                                                             |

| Fault Response Time           | $T_{RESP}$       |      | 200  |      | ns   |                                                                             |

| Dead Time - Input             | $T_{NOV}$        |      | 1000 |      | ns   | Recommended Minimum Time between Inputs                                     |

| Dead Time – Driver            | Tcod             | 1000 |      |      | ns   | Minimum Time between drive signals allowed by driver, software configurable |

| Reset Timing                  | Treset           | 1000 |      |      | ns   | Minimum Reset Time                                                          |

| Automatic Reset (Optional)    |                  |      | 5    |      | ms   | Standard setting of 5 ms                                                    |

| Main-Secondary<br>Timing Skew |                  |      |      | 10   | ns   | Timing difference between Main and Secondary drivers                        |

<sup>\*</sup>Note 3

Figure 10: Measurement points for rise and fall time.

#### **Temperature Monitor**

The following table describes the correlation between the Thermistor Temperature and Temperature Monitor PWM Output with 2kHz 4 pole filter. This is based on an NTC thermistor that measures  $5k\Omega$  @  $25^{\circ}$ C. Recommended Thermistor P/N: USUR1000-502G.

| Output Voltage [V] | Temperature [°C] |

|--------------------|------------------|

| 0.8                | -3               |

| 1.6                | 25               |

| 2.2                | 41               |

| 2.8                | 57               |

| 3.1                | 67               |

| 3.3                | 74               |

| 3.4                | 80               |

| 3.7                | 94               |

| 4.0                | 108              |

| 4.1                | 122              |

| 4.3                | 138              |

| 4.4                | 154              |

#### DC Link Voltage Monitor – 1200V

The DC Link (HI Side drain to LO Side source) Monitor Output Voltage is 1% accurate from 25V to 975V. The PWM output is the ratio of the DC Link Voltage / 1000V. For example, a 500V DC Link Voltage, the PWM output will be 50%. The linear equation for the Voltage Monitor PWM Output with a 2 kHz 4 pole filter is:

$$V_{DC}[V] = 200 \, X \, Vmonitor$$

#### DC Link Voltage Monitor - 1700V

The DC Link (HI Side drain to LO Side source) Monitor Output Voltage is 1% accurate from 50V to 1650V. The PWM output is the ratio of the DC Link Voltage / 1700V. For example, an 825V DC Link Voltage, the PWM output will be 50%. The linear equation for the Voltage Monitor PWM Output with a 2 kHz 4 pole filter is:

$$V_{DC}[V] = 340 X V monitor$$

## **Generic Sample Factory Settings**

AgileSwitch drivers are designed to provide safe, secure and efficient operation of the SiC MOSFET power module, as well as to provide unparalleled information on the condition of the overall system.

Generic samples are set at the factory to perform certain actions (e.g. turn off the HI side or LO side of the SiC MOSFET) and to report that a fault occurred based on performance parameters that occur outside of default ranges.

The tables below show the generic configuration.

#### **Performance & Interconnect Settings**

| Parameter                        | <b>Generic Factory Setting</b> | Value | Unit |  |  |

|----------------------------------|--------------------------------|-------|------|--|--|

| Rgon (Turn-on Gate Resistance)   | Populated                      | 1.1   | Ω    |  |  |

| Rgoff (Turn-off Gate Resistance) | Populated                      | 1.1   | Ω    |  |  |

| Desaturation Time                | Enabled                        | 1.5   | μs   |  |  |

| Dead Time                        | Enabled                        | 1     | μs   |  |  |

| Fault Reset                      | Auto                           | 5     | ms   |  |  |

| DC Link Voltage Fault            | Enabled                        | 900   | V    |  |  |

| Temperature Fault                | Enabled                        | 125   | °C   |  |  |

| UVLO Primary                     | Enabled                        | 13.2  | V    |  |  |

| OVLO Primary                     | Enabled                        | 16.5  | V    |  |  |

| J1 (20 pin Control/Power Header) | Populated                      |       |      |  |  |

| J5 (2 pin Thermistor Header)     | Populated                      |       |      |  |  |

| J6 (5 pin Main/Secondary Header) | Not Populated                  |       |      |  |  |

| J7 (4 pin Main/Secondary Header) | Not Popu                       | lated |      |  |  |

#### **Fault and Monitoring Conditions**

| Fault<br>Condition/Action        | Generic Sample<br>Default Trigger<br>Values  | Action on IGBT if<br>Active (Default<br>Setting) | HI<br>Fault | LO<br>Fault | All<br>Faults |

|----------------------------------|----------------------------------------------|--------------------------------------------------|-------------|-------------|---------------|

| NO FAULTS                        |                                              |                                                  | HIGH        | HIGH        | HIGH          |

| DSAT/UVLO – HI                   | See Electrical<br>Characteristics            | Turn Off HI & LO<br>Side                         | LOW         | HIGH        | LOW           |

| DSAT/UVLO – LO                   | See Electrical<br>Characteristics            | Turn Off HI &LO<br>Side                          | HIGH        | LOW         | LOW           |

| OVLO                             | See Electrical<br>Characteristics            | Turn Off HI & LO<br>Side                         | HIGH        | HIGH        | LOW           |

| Temperature Fault                | 125 °C Thermistor<br>Monitor                 | No Action                                        | HIGH        | HIGH        | LOW           |

| DC Link Voltage<br>Fault         | DC Link Voltage<br>above or below<br>setting | Turn Off HI & LO<br>Side                         | HIGH        | HIGH        | LOW           |

| Power On<br>Configuration Fault* | Failure to Configure<br>Gate drivers         | Turn Off HI & LO<br>Side                         | LOW         | LOW         | LOW           |

<sup>\*</sup>After power up, if all Fault lines are LOW, then either there is a real fault (UVLO/DSAT) on both the HI and LO sides or there has been a software configuration failure.

## **Important Precautions**

Caution: Handling devices with high voltages involves risk to life. It is imperative to comply with all respective precautions and safety regulations.

When installing the ribbon cable, please make sure that power is turned off. Multi-signal values are sent along this ribbon cable, thus hot swapping may cause damage to the IC components on the board.

AgileSwitch assumes that the gate drive board has been mounted on the SiC MOSFET prior to start-up testing. It is recommended that the user checks that the SiC MOSFET power modules are operating inside the Specified Operating Area (SOA) as specified by the module manufacturer including short circuit testing under very low load conditions.

## **Recommended Start-Up Testing**

- 1. Connect the driver through the 20 pin control header to your drive electronics and supply the driver with +15V.

- 2. Send the fault reset pin, pin 19, a low signal. Return pin 19 to a high condition. (If the driver is configured for Auto Reset, you may ignore this step.)

- 3. Check the gate voltage:

- a) For the off-state, the nominal gate voltage should be -6V to -4V. (Note 3)

- b) For the on state, it is +17 to +21V. (Note 3)

- c) Check that the supply current of the driver is within spec with inactive trigger signals and then at the desired switching frequency.

- 4. The system is now ready for application testing under load conditions.

- 5. Check thermal conditions to verify that the system is operating within specified temperature range.

- 6. Do NOT apply High Voltage to the SiC Module without first applying power to the GDB.

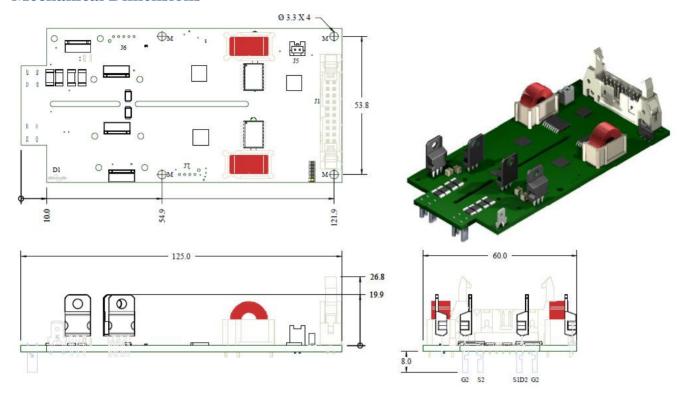

# **Mechanical Dimensions**

Figure 11: Dimensions of the 62EM1-62mm Electrical Gate Driver (+/- 0.1mm)

Dimensions are in mm.

Download the full drawing and model for additional details. Not all components are shown.

62EM1 Drawing

62EM1 .STEP Model

# **Part Numbers & Configuration Details**

|                                  | Part Number           |              |

|----------------------------------|-----------------------|--------------|

| Hardware Settings                | Symbol                | 62EM1-00001  |

| Rgon (Turn-on Gate Resistance)   | R <sub>GON</sub>      | 1.1 Ω        |

| Rgoff (Turn-off Gate Resistance) | R <sub>GOFF</sub>     | 1.1 Ω        |

| Input Triggers                   | V <sub>IN_LOGIC</sub> | 15V          |

| Trigger Type                     | -                     | Single ended |

For hardware modifications, please contact Microchip.

| Software Settings                  | Symbol               | 62EM1-00001 |

|------------------------------------|----------------------|-------------|

| Dead Time                          | T <sub>NOV</sub>     | 430ns       |

| Gate Driver Reset                  | -                    | Automatic   |

| Reset Time Delay                   | T <sub>RESET</sub>   | 5ms         |

| DC Link Voltage Fault              | -                    | 950V        |

| Temperature Fault                  | -                    | 130C        |

| Fault Output Active Level          | -                    | Low         |

| Normal Two-Level Turn-Off          | -                    | Enabled     |

| Normal Two-Level Turn-Off Voltage  | $V_{SOFT}$           | 0V          |

| Normal Two-Level Turn-Off Time     | $T_{S1}$             | 200ns       |

| DSAT Multi-Level Turn-Off          | -                    | Enabled     |

| DSAT Blanking Time                 | $T_{DSAT}$           | 1.5µs       |

| DSAT First Turn-Off Voltage Level  | V <sub>SOFT</sub> D1 | 9V          |

| DSAT First Turn-Off Time           | TSD1                 | 400ns       |

| DSAT Second Turn-Off Voltage Level | V <sub>SOFT</sub> D2 | 5V          |

| DSAT Second Turn-Off Time          | TSD2                 | 200ns       |

| Primary UVLO/OVLO Fault Detection  | -                    | Enabled     |

| Secondary UVLO Fault Detection     | -                    | Enabled     |

For software modifications, please go to: <a href="https://www.AgileSwitch.com/program.html">www.AgileSwitch.com/program.html</a>

# **Revisions**

| Version | Date       | Description                                                      |  |

|---------|------------|------------------------------------------------------------------|--|

| 01      | 10/14/2016 | Preliminary Release                                              |  |

| 02      | 10/24/2016 | Added Patent Number                                              |  |

| 03      | 1/16/2017  | Updated characteristics, mechanical drawing                      |  |

| 04      | 5/22/2017  | Updated mechanical drawing                                       |  |

| 05      | 6/16/2017  | Added part number info. for thermistor connector, de-glitch time |  |

| 06      | 10/9/2017  | Beta Release to reflect lifetime & power testing                 |  |

| 07      | 11/16/2017 | Modified Fault & Monitoring conditions table                     |  |

| 08      | 3/18/2020  | Added configuration details                                      |  |

| 09      | 1/26/2021  | Updated Figure 3                                                 |  |

| 10      | 6/2/2021   | Updated isolation voltage in absolute max ratings                |  |

## **Legal Disclaimer**

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, OUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE.

Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

All Microchip products are sold pursuant to Microchip's terms and conditions of sale.

The Microchip name and logo, the Microchip logo, and AgileSwitch are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

© 2020 Microchip Technology Incorporated. All Rights Reserved <a href="www.microchip.com">www.microchip.com</a>. Any other names are the property of their respective owners.

Information in this document supersedes and replaces all information previously supplied.

Specifications are subject to change without notice.

#### **Patent Notices**

| Offering                             | Issued U.S. Patent Numbers |

|--------------------------------------|----------------------------|

| AgileStack <sup>TM</sup> Power stack | 8,984,197                  |

| control systems                      |                            |

| Gate drive control system for        | 9,490,798                  |

| SiC and IGBT power devices           |                            |

| Additional Patents Pending           |                            |

#### **Address**

Microchip Technology Inc 2355 West Chandler Blvd. Chandler, Arizona, USA 85224-6199 (480) 792-7200