# Change Summary

# CHANGES

| No. | o. Applicable Section Description |                                              | Page(s) |

|-----|-----------------------------------|----------------------------------------------|---------|

| 1.  | Ordering Information              | a) Add OZ972GN, OZ972IGN, OZ976TN & OZ976ITN | 1       |

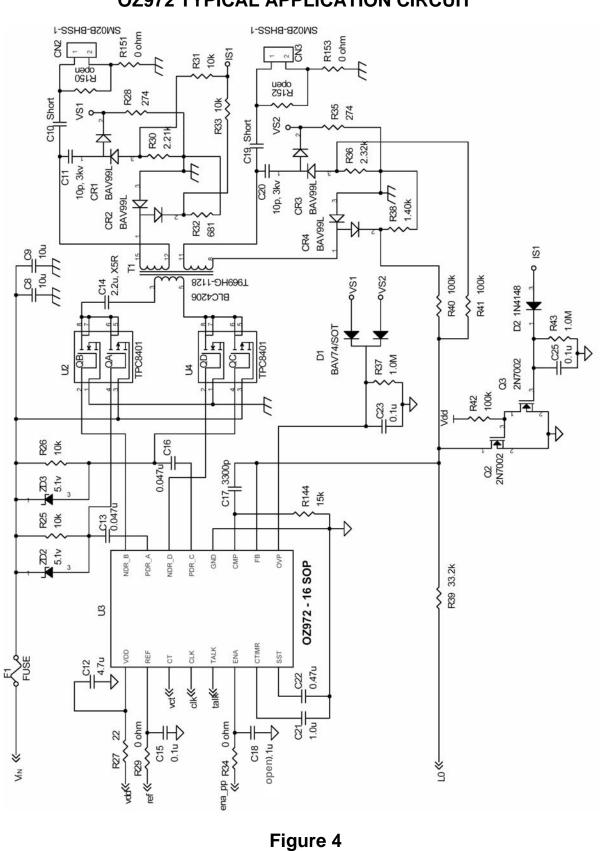

| 2.  | OZ972 Typical Application Circuit | Change C18 value from "0.1u" to "open"       | 16      |

| 3.  | Throughout data sheet             | Miscellaneous corrections                    |         |

# **REVISION HISTORY**

| Revision No. | Description of change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Release<br>Date |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0.97         | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10/21/02        |

| 0.98         | 1. Revise part number in header and footer to read "O2972/ <u>O2</u> 976" and ensure text diagrams and figures are in this sequence throughout data sheet; 2. Add alpha to part numbers in "Ordering Information"; 3. Add patent number in footer of first page; 4. Update the O2972 and O2976 functional block diagrams, application circuit figures and functional specifications; 5. Revise "Functional Specifications" for O2972 and O2976 as follows: <u>O2972</u> - a] first test condition listed, <u>b</u> add note (2), <u>c</u> ) add note (2) to Input Offset Voltage and change Max. limit, <u>d</u> ) add note (2) to Input Voltage Range, Open Loop Voltage Gain and Unity Gain Bandwidth under Error Amplifier, <u>e</u> ) delete Power Supply Rejection parameter, <u>f</u> ) add Source and Sink Current parameters [with note (2)] under Error Amplifier, <u>g</u> ) add note (2) to NDR-PDR Output Resistance (current sink) and change Typ. & Max, limits, <u>j</u> ) change Max. Min. Overlap title to "Maximum Overlap", <u>j</u> ) Maximum Overlap between Diagonal Switches Min. & Typ. limits, <u>M</u> ) delete Gate Drive (A,B,C,D) Off Condition parameter, <u>j</u> ) Break-Before-Make PDR_A/NDR_B and PDR_C/NDR_D Min. & Max, limits, <u>m</u> ) OVP test condition, Min. and Typ. limits; <u>O2976 - n</u> ) Add notes (4) & (5), <u>o</u> add note (4) to Reference Voltage-Nominal and change Min., Typ. & Max, limits, <u>m</u> ) add source and Sink Current parameters under Reference Voltage-Source voltage-Load Regulation and change Max. limit; <u>m</u> ) add source and Sink Current parameters under Reference Voltage, <u>s</u> ] delete C Toscillator Ramp Peak and Valley and note (5) to LCT Oscillator Ramp Peak and Valley and change Min., Typ. & Max, limits, <u>m</u> ) CT Oscillator CLK Frequency Min., Typ. & Max, limits, <u>m</u> ) add note (5) to LCT Oscillator Ramp Peak and Valley and change Min. & Max, limits, <u>m</u> ) change Threshold VIN <u>5</u> " and change Min. & Max, limits, <u>n</u> ) change Threshold VIN <u>5</u> " and change Min. & Max. limits, and <u>2</u> ] add TALK parameter under Threshold; 6. Correct subtite under item "15." to read "VINS"; 7. Update the formulas for the operatio | 04/23/03        |

| 0.99         | 1. Features & Gen'l Descriptioncorrect application lamp numbers; 2. Correct package type in part name in Ordering Information; 3. Update Functional Block Diagram; 4. Update OZ976 Typical Application Circuit; 5. OZ976 Pin Descriptiondelete note ref. for pin # s 38, 44 & 45; 6. Complete 'Package Power Dissipation' value in Absolute Max, Ratings; 7. OZ972 Functional Specs <u>a)</u> replace 'Input voltage range' parameter & limits, with 'Reference voltage at non-inverting input pin (internal)' parameter & limits, <u>b</u> correct 'Max. Overlap between diagonal switches' test condition, <u>c)</u> correct Break-Before-Make 'PDR_ANDR, B' test conditions, Typ & Max limits, and 'PDR_C'NDR_D test conditions, Typ & Max limits, <u>and g</u> ) Correct 'Supply Current' test conditions, Typ & Max limits, <u>and g</u> ) SST current 'Min, Typ & Max limits, <u>8</u> , OZ976 Functional Specs <u>a)</u> add note (5) to CT Oscillator 'Temp, stability', and <u>b</u> ) correct 'Supply Current' test conditions, <u>7</u> , 6 <sup>th</sup> line, correct voltage referenced; <u>10</u> . Functional Description, 8, 1 <sup>st</sup> line, correct voltage referenced; <u>11</u> . Functional Description, 8, 1 <sup>st</sup> line, correct voltage referenced; <u>11</u> . Functional Description, 8, correct voltage referenced; <u>12</u> . Functional Description, 8, correct Internal LCT frequency formula; <u>13</u> . Package Information, delete symbol 'C' in table; not included in the drawing; and <u>14</u> . Misc. corrections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 05/13/03        |

| 1.0          | 1. Add O2972IG & O2976IT packages and table that include temp range of each package in Ordering Information and General Description, 2.<br>Delete "I/O" columns in Pin Description tables, 3. Absolute Max. Ratings a) Modify table title, b) move note "(1)" from "VDDA, VDDA, VDDD, VDD" to the table title, c) innange "Logic Inputs" to read "Signal Inputs", d) revise Resonator Frequency', and d) add separate Operating Temp. table that breaks out commercial and industrial temp ranges, 4. O2972 Electrical Characteristics Revise a) table title, b) add temp range before the table, c) first test condition at beginning of table, d) delete 'Input offset voltage' parameter, e) add test conditions and Min, Typ & Max limits for 'Reference voltage at non-inverting input pin and revise current Min, Typ & Max limits, f) delete 'Open looy voltage gain and Unity gain bandwidth' parameters, g) change 'Source Current' title to read 'Output voltage', add symbol and test condition, and revise Min, Typ, Max limits & units, f) delete 'Snin Current' parameter, f) test conditions for 'NDR-PDR Output' parameters, adding Min, Typ, Max limits & units for new test conditions, j) 'Break-Before-Make' parameters Min, Typ & Max limits, b) add test condition plus Min, Typ, Max limits & units o' Threshold OVP' and update current test conditions, Min, Typ & Max limits, b) add test condition plus Min, Typ, Max limits & units o' Threshold OVP' and update current test conditions, adding Min, Typ, Max limits & units for new test conditions, and revising current Min, Typ & Max limits, e) 'CJ2976 Electrical Characteristics Revise a) table title, b) add test perfore that table, c) first test condition at beginning of table, d) add test condition plus Min, Typ, & Max limits, e) 'Line regulation' note numbers and Max limit, Typ, Max limits & units for new test conditions, and revising current Min, Typ & Max limits, e) 'Line regulation' note numbers and Max limit, f) delete 'Load regulation', 'Source Current' and 'Sink Current', g) add tote(3) to 'Low Frequency P                                                                                                                                                    |                 |

# Intelligent CCFL Inverter Controller

# FEATURES

- Low cost synchronized inverter solution

- Fixed synchronized operating frequency for up to 48 CCFLs

- Programmable operating and PWM frequencies

- Zero-voltage-switching full bridge topology

- 90% efficiency vs. typical 70% efficiency of conventional designs

- Supports up to 12 equal-delay PWM signals

- PWM signals synchronized with either external or internal signal

- Intelligent time-sharing dimming control

- Constant-frequency design eliminates interference between CCFLs and LCD panel.

- Built-in intelligence for ignition and normal operation of CCFLs

- Internal open lamp and over voltage

protection

- Fewer components and smaller board size

- Low stand-by power

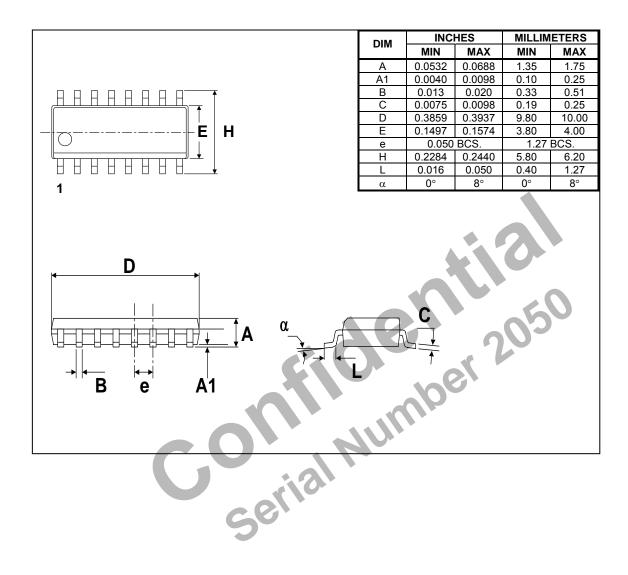

| Part<br>Number | Temp Range    | Package                  |

|----------------|---------------|--------------------------|

| 0Z972G         | 0°C to 70°C   | 16-pin SOP               |

| 0Z972IG        | -40°C to 85°C | 16-pin SOP               |

| 0Z972GN        | 0°C to 70°C   | 16-pin SOP,<br>Leadfree  |

| 0Z972IGN       | -40°C to 85°C | 16-pin SOP,<br>Leadfree  |

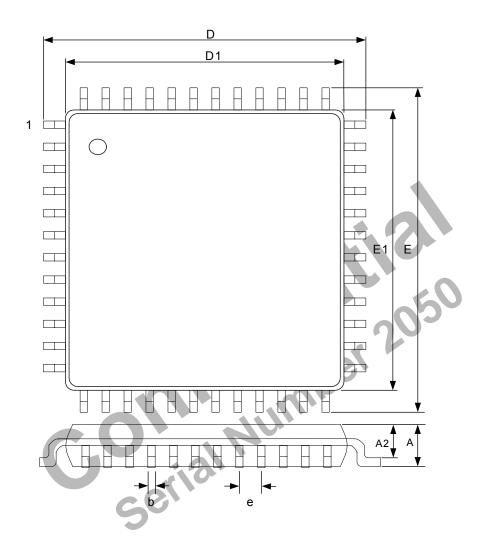

| OZ976T         | 0°C to 70°C   | 48-pin LQFP              |

| OZ976IT        | -40°C to 85°C | 48-pin LQFP              |

| OZ976TN        | 0°C to 70°C   | 48-pin LQFP,<br>Leadfree |

| 0Z976ITN       | -40°C to 85°C | 48-pin LQFP,<br>Leadfree |

# **ORDERING INFORMATION**

# **GENERAL DESCRIPTION**

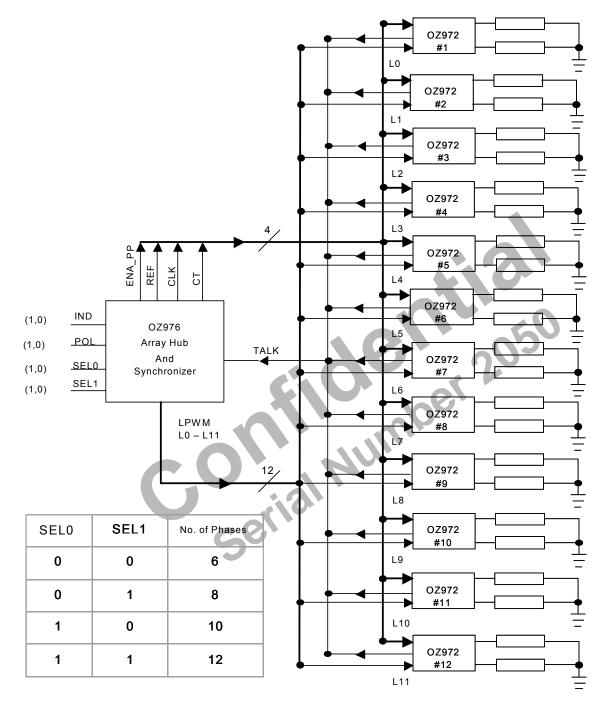

The Phase Array (OZ972/OZ976) is a unique, high-efficiency, CCFL backlight controller chipset that is targeted for LCD applications requiring 6 to 48 lamps. The Phase Array chipset consists of two devices, the OZ976 Array Hub and OZ972 Power Controller. Depending on the number of lamps, each application requires one OZ976 device and either 6, 8, 10 or 12 OZ972 Power Drivers. The number of OZ972 devices used in an application is user-selectable. Figure 1, page 8, illustrates the Phase Array topology. The OZ972, Power Controller, drives a zerovoltage-switching full-bridge circuit, providing output voltage and current waveforms to the CCFLs. Operating in a zero-voltage switching configuration; the inverter circuit minimizes EMI emission. In addition, the inverter circuit achieves very high power conversion efficiency resulting in lower heat and higher system reliability.

A smart protection circuit is incorporated in the Power Controller to achieve a high safety requirement. This circuit provides lamp ignition, normal operation, open lamp and broken lamp protection, and communicates the status to the OZ976. Intelligent open-lamp and over-voltage protection provides design flexibility with various transformer characteristics.

The OZ976, Array Hub, generates and distributes the operating frequency to all OZ972 Power Controllers, to ensure that all lamps operate at one frequency. This eliminates interference among lamps that result from different lamp operation frequencies. Interference causes EMI problems and may create visual effects (waterfall) on the LCD panel. The operating frequency of the OZ976 is programmable via an external resistor and capacitor.

The OZ976 utilizes the pulse-width-modulation (PWM) dimming method to achieve a wide dimming range. The PWM dimming frequency can be synchronized with an external TTL-level signal or an internal signal, programmed via an internal (LCT) oscillator circuit. If an external TTL level signal does not exist, the OZ976 will automatically follow the pre-programmed LCT frequency to generate the PWM signals. Otherwise, the external TTL level frequency will be used to generate the PWM signals.

The OZ976 provides a set of PWM signals with a different phase delay to each OZ972. This method reduces power supply ripple. Without the PWM phase shift, a system utilizing a large number of lamps, for example 12, would cause a large power supply current surge (spike) if the lamps turned on and off simultaneously. This abrupt power demand increases the power supply design burden and degrades EMI performance. By splitting a large power demand into smaller segments, the OZ976 minimizes the peak power bus ripple and in-rush current. The OZ976 monitors the power supply voltage to prevent an under-voltage lockout condition. OZ976 will disable all the inverters if it detects an under-voltage condition.

The OZ972 is available in a 16-pin SOP package and the OZ976 in a 48-pin LQFP package. Both devices are specified over the commercial temperature range from  $0^{\circ}$ C to  $70^{\circ}$ C, and the industrial temperature from  $-40^{\circ}$ C to  $85^{\circ}$ C.

continue 2050 Serial Number 2050

# **OZ972 PIN DESCRIPTION**

| Name  | Pin No. | Description                                             |

|-------|---------|---------------------------------------------------------|

| VDD   | 1       | IC Power                                                |

| REF   | 2       | Reference Voltage Input                                 |

| СТ    | 3       | Saw tooth wave with double inverter operating frequency |

| CLK   | 4       | Square wave with inverter operating frequency           |

| TALK  | 5       | Strike/Normal/Shut Down indicator                       |

| ENA   | 6       | Enable input; TTL signal – Active High                  |

| CTIMR | 7       | CCFL ignition period timer                              |

| SST   | 8       | Soft-start timer                                        |

| OVP   | 9       | Output voltage sense, Vth=2.0V                          |

| FB    | 10      | CCFL current feedback signal                            |

| CMP   | 11      | Compensation output of the error amplifier              |

| GND   | 12      | Ground                                                  |

| PDR_C | 13      | PMOSFET drive output                                    |

| NDR_D | 14      | NMOSFET drive output                                    |

| PDR_A | 15      | PMOSFET drive output                                    |

| NDR_B | 16      | NMOSFET drive output                                    |

# **OZ976 PIN DESCRIPTION**

| Name   | Pin No.                                            | Description                                                          |

|--------|----------------------------------------------------|----------------------------------------------------------------------|

| ENA PP | 3                                                  | Enable OZ972                                                         |

| VDDA2  | 4                                                  | Analog Power                                                         |

| VDDA   | 5                                                  | Analog Power                                                         |

| VDDD   | 6                                                  | Digital Power                                                        |

| OSCA   | 7                                                  | Connected to 4MHz Resonator                                          |

| OSCY   | 8                                                  | Connected to 4MHz Resonator                                          |

| VSYNC  | 9                                                  | External synchronization input, TTL signal                           |

| TALK   | 10                                                 | OZ972 feedback Ignition/Normal/Abnormal                              |

| L11    | 14                                                 | Low frequency PWM signal with x11 phase delay                        |

| L10    | 15                                                 | Low frequency PWM signal with x10 phase delay                        |

| L9     | 16                                                 | Low frequency PWM signal with x9 phase delay                         |

| L8     | 17                                                 | Low frequency PWM signal with x8 phase delay                         |

| L7     | 18                                                 | Low frequency PWM signal with x7 phase delay                         |

| L6     | 19                                                 | Low frequency PWM signal with x6 phase delay                         |

| L5     | 20                                                 | Low frequency PWM signal with x5 phase delay                         |

| L4     | 21                                                 | Low frequency PWM signal with x4 phase delay                         |

| L3     | 22                                                 | Low frequency PWM signal with x3 phase delay                         |

| L2     | 23                                                 | Low frequency PWM signal with x2 phase delay                         |

| L1     | 27                                                 | Low frequency PWM signal with x1 phase delay                         |

| L0     | 28                                                 | Low frequency PWM signal with no phase delay                         |

| GNDD   | 29                                                 | Digital Ground                                                       |

| GNDA   | 30                                                 | Analog Ground                                                        |

| GNDA2  | 31                                                 | Analog Ground                                                        |

| REF    | 32                                                 | Reference voltage output; 2.5V typical @ 100uA                       |

| CLK    | 33                                                 | Inverter operating clock                                             |

| СТ     | 34                                                 | Timing capacitor set inverter operating frequency                    |

| POL    | 38                                                 | POL(Polarity), Select dimming voltage polarity                       |

| IND    | 39                                                 | IND(Individual), Select OZ972 system protection mode                 |

| ENA    | 40                                                 | Enable input; TTL signal                                             |

| RT     | 41                                                 | Timing resistor set operating frequency                              |

| RT1    | 42                                                 | Timing resistor for programming ignition frequency and PWM frequency |

| LCT    | 43                                                 | Timing capacitor set internal PWM frequency                          |

| SEL1   | 44                                                 | Lamp number selector, work with SEL0                                 |

| SEL0   | 45                                                 | Lamp number selector, work with SEL1                                 |

| VDIM   | 46                                                 | A DC voltage for dimming control                                     |

| VINS   | 47                                                 | Input voltage sense, Vth=1.5V                                        |

| NC     | 1, 2, 11, 12, 13,<br>24, 25, 26, 35,<br>36, 37, 48 | No Connection                                                        |

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| VDDA, VDDA2, VDDD, VDD | 7.0V                |

|------------------------|---------------------|

| GNDA, GNDA2, GNDD, GND | +/-0.3V             |

| Signal Inputs          | -0.3V to VDDA +0.3V |

| Resonator Frequency    | 8MHz                |

|                           | OZS  | 972 | OZ976          |

|---------------------------|------|-----|----------------|

| Package Power Dissipation | 86 ° | C/W | 63 °C/W        |

|                           |      |     |                |

| Maximum Junction Temp.    |      |     | 125°C          |

| Storage Temp.             |      |     | -55°C to 150°C |

## **RECOMMENDED OPERATING RANGE**

| VDDA, VDDA2, VDDD, VDD                       | 4.7V ~ 5.3V                   |

|----------------------------------------------|-------------------------------|

| Inverter Operating Frequency <sup>(2)</sup>  | 30KHz to 150KHz               |

| $R_T$ for Inverter Operating                 | 40k $\Omega$ to 150k $\Omega$ |

| Resonator Frequency Selection <sup>(3)</sup> | 3MHz to 4MHz                  |

| Operating Temp. | OZ972/OZ976 | OZ972I/OZ976I |

|-----------------|-------------|---------------|

|                 | 0°C to 70°C | -40°C to 85°C |

#### Notes:

(1) The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The "Functional Specifications" table defines the conditions for actual ...pulses, f<sub>ABCD</sub>, a. device operation. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

(2) The frequency of PDR\_A, NDR\_B, PDR\_C, and NDR\_D output pulses, f\_ABCD, are half of CT frequency value.

(3) See Table 2, page 16 for more detail.

# **OZ972 ELECTRICAL CHARACTERISTICS**

OZ972:  $0^{\circ}C < Tamb < 70^{\circ}C$ , unless otherwise specified OZ972I: -40°C < Tamb < 85°C, unless otherwise specified

|                                |                  | Test Conditions                                       |      | Limits   |      |        |

|--------------------------------|------------------|-------------------------------------------------------|------|----------|------|--------|

| Parameter                      | Symbol           | VDD = 5.0V; REF = 2.5V;<br>unless otherwise specified | Min  | Тур      | Max  | Unit   |

| Error Amplifier                |                  |                                                       |      |          |      |        |

| Reference voltage at non-      |                  | Tamb=25°C                                             | 1.26 | 1.28     | 1.31 | V      |

| inverting input pin (internal) |                  | Temp coefficient                                      | -    | 50       | -    | ppm/°C |

| Output voltage (2)             | V11              | V10=0V; Rload=15k                                     | 3.0  | -        | -    | V      |

| NDR-PDR Output                 |                  |                                                       |      |          |      |        |

| Output resistance (2)          | Р                | Tamb=25°C; Rload=30Ω                                  | -    | 27       | 33   | Ω      |

| Output resistance              | R <sub>p</sub>   | Temp coefficient                                      | -    | 3000     | -    | ppm/°C |

| Output resistance (2)          |                  | Tamb=25°C; Rload=30Ω                                  | -    | 27       | 33   | Ω      |

| Output resistance              | Rn               | Temp coefficient                                      | -    | 3000     |      | ppm/°C |

| Maximum Overlap                |                  |                                                       |      |          |      |        |

| Max. Overlap between diagonal  |                  | CLK = 63kHz                                           | 78   |          |      | 0/     |

| switches                       |                  | Ca=Cb=Cc=Cd=1nF <sup>(1)</sup>                        | 78   | -        |      | %      |

| Break-Before-Make              |                  |                                                       |      |          |      |        |

| PDR A/NDR B                    |                  | CLK = 63kHz                                           | 70   | 115      | 160  | ns     |

| FDR_AINDR_B                    |                  | Ca=Cb=Cc=Cd=1nF <sup>(1)</sup>                        |      |          |      | 115    |

| PDR_C/NDR_D                    |                  | CLK = 63kHz                                           | 55   | 105      | 150  | ns     |

|                                |                  | Ca=Cb=Cc=Cd=1nF <sup>(1)</sup>                        |      |          |      |        |

| Threshold                      | -1               |                                                       |      | <b>i</b> | i    | 1      |

| OVP                            |                  | Tamb=25°C                                             | 2.16 | 2.22     | 2.28 | V      |

|                                |                  | Temp coefficient                                      | -    | 500      | -    | ppm/°C |

| Talk <sup>(2)</sup>            |                  | Logic High                                            | 2.0  | -        | -    | V      |

| Taik                           |                  | Logic Low                                             | -    | -        | 1.0  | V      |

| Supply                         |                  |                                                       | -    |          |      |        |

| Supply current                 | IOFF             | ENA = low                                             | -    | 150      | 200  | μΑ     |

| Cupply ourrant                 | C                | ENA = High;                                           |      | 4.0      | 5.0  | mA     |

| Supply current                 | ION              | CLK = 63kHz                                           | -    | 4.0      | 5.0  |        |

| SST current                    | I <sub>SST</sub> |                                                       | 2.5  | 5.0      | 7.6  | μA     |

|                                |                  | Tamb=25°C                                             | 1.9  | 2.6      | 3.3  | μA     |

| CTIMR current                  | ICTIMR           | Temp coefficient                                      | -    | 4500     | -    | ppm/°C |

#### Notes:

(1) Ca: capacitor from PDR\_A (Pin 15) to VDDA

Cb: capacitor from NDR\_B (Pin 16) to ground Cc: capacitor from PDR\_C (Pin 13) to VDDA

Cd: capacitor from NDR\_D (Pin 14) to ground (2) Denotes that parameter is guaranteed by design and not production tested.

# **OZ976 ELECTRICAL CHARACTERISTICS**

OZ976:  $0^{\circ}C < Tamb < 70^{\circ}C$ , unless otherwise specified OZ976I:  $-40^{\circ}C < Tamb < 85^{\circ}C$ , unless otherwise specified

| Parameter                      | Symbol | Test Conditions                                     |      | Limits |      |          |

|--------------------------------|--------|-----------------------------------------------------|------|--------|------|----------|

|                                |        | VDDA/VDDA2/VDDD = 5V;<br>unless otherwise specified | Min  | Тур    | Max  | Unit     |

| Reference Voltage              |        |                                                     |      |        |      |          |

| Neminal valtare <sup>(4)</sup> | DEE    | Tamb = 25°C; I <sub>load</sub> = 0.25mA             | 2.39 | 2.55   | 2.71 | V        |

| Nominal voltage (4)            | REF    | Temp coefficient                                    | -    | 200    | -    | ppm/°(   |

| Line regulation (2, 4)         |        | VDDA = 4.7V - 5.3V                                  | -    | 4      | -    | mV/V     |

| CT Oscillator                  |        |                                                     |      |        |      |          |

|                                |        | Tamb = 25°C;                                        |      |        |      |          |

| CLK Frequency                  |        | CT = 220pF, RT = 48.7k $\Omega^{(1)}$               | 58   | 63     | 68   | KHz      |

|                                |        | Temp coefficient                                    | -    | 200    | -    | ppm/°    |

| LCT Oscillator                 |        |                                                     |      |        |      | ppii     |

|                                |        | Tamb = 25°C;                                        |      |        |      |          |

| Initial accuracy               |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               | 190  | 210    | 230  | Hz       |

| initial accuracy               |        |                                                     |      | 500    |      | nnm/0    |

|                                | (3)    | Temp coefficient                                    |      | -500   | -    | ppm/°    |

| Low Frequency PWM (L0-L        | 1)     | VDIM = 1V; POL = 0V;                                |      |        |      |          |

|                                |        |                                                     |      |        |      | <u> </u> |

|                                |        | VSYNC frequency = 70Hz;                             | 0    | -      | 0    | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        | r    |          |

|                                |        | VDIM = 1.5V; POL = 0V;                              |      |        |      |          |

|                                |        | VSYNC frequency = 70Hz;                             |      | 18 -   | -    | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

|                                |        | VDIM = 3.2V; POL = 0V;                              | -    |        |      | %        |

|                                |        | VSYNC frequency = 70Hz;                             |      | 70     | -    |          |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

|                                |        | VDIM = 1V;POL = 0V;                                 |      | _      | 0    | %        |

|                                | C      | VSYNC = GNDA;                                       | 0    |        |      |          |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               | Ŭ    |        | Ŭ    | 70       |

|                                |        | VDIM = 1.5V;POL = 0V;                               |      |        |      |          |

| Duty Quela Decara              |        | VDIM = 1.5V,POL = 0V,<br>VSYNC = GNDA;              |      | 50     |      | 0/       |

| Duty Cycle Range               | L0-L11 |                                                     | -    | 50     | -    | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

|                                |        | VDIM = 2.2V;POL = 0V;                               |      |        |      | %        |

|                                |        | VSYNC = GNDA;                                       | 100  | -      | 100  |          |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

|                                |        | VDIM $\geq$ 3.2V; POL = 5V;                         |      |        |      |          |

|                                |        | VSYNC = GNDA;                                       | 0    | -      | 0    | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

|                                |        | VDIM = 2.5V; POL = 5V;                              |      |        |      |          |

|                                |        | VSYNC = GNDA;                                       | -    | 50     | -    | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      | -      |      | 70       |

|                                |        | $VDIM \leq 1.8V; POL = 5V;$                         |      |        | 1    |          |

|                                |        | VSYNC = GNDA;                                       | 100  |        | 100  | 0/       |

|                                |        |                                                     | 100  | -      | 100  | %        |

|                                |        | LCT = 10nF, RT = 48.7k $\Omega^{(2)}$               |      |        |      |          |

# **OZ976 ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Parameter                                                                                                                                                                             | Symbol                                        | Test Conditions                                     |      | Limits |      |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------|------|--------|------|--------------|

|                                                                                                                                                                                       |                                               | VDDA/VDDA2/VDDD = 5V;<br>unless otherwise specified | Min  | Тур    | Max  | Unit         |

| Threshold                                                                                                                                                                             |                                               |                                                     |      |        |      |              |

| ENABLE                                                                                                                                                                                | ENA                                           |                                                     | 2.0  | -      | -    | V            |

| DISABLE                                                                                                                                                                               | ENA                                           |                                                     | -    | -      | 1.0  | V            |

| VINS (ON)                                                                                                                                                                             |                                               |                                                     | 1.65 | -      | -    | V            |

| VINS (OFF)                                                                                                                                                                            |                                               |                                                     | -    | -      | 1.25 | V            |

| TALK <sup>(5)</sup>                                                                                                                                                                   |                                               | Logic High                                          | 3.5  | -      | -    | V            |

| IALK <sup>(*)</sup>                                                                                                                                                                   |                                               | Logic Low                                           | -    | -      | 1.6  | v            |

| Supply                                                                                                                                                                                |                                               |                                                     |      |        |      |              |

| Supply current                                                                                                                                                                        |                                               | ENA = low                                           | -    | 165    | 280  | μA           |

|                                                                                                                                                                                       |                                               | ENA = high                                          |      |        |      |              |

| O                                                                                                                                                                                     |                                               | 12-phase selection                                  |      |        | Ų.   |              |

| Supply current                                                                                                                                                                        |                                               | VDIM = 2V; L0-L11 = 50k $\Omega^{(3)}$              | -    | 4.4    | 5.5  | mA           |

|                                                                                                                                                                                       |                                               | CLK = 63kHz; LCT = 210Hz                            |      |        |      | $\mathbf{C}$ |

| Notes:<br>(1) CT: capacitor from CT (pin 3)<br>RT: resistor from RT (pin 41)<br>(2) LCT: capacitor from LCT (Pin<br>RT: resistor from RT (pin 41)<br>(3) L0-L11: 50kQ resistor is con | ) to ground<br>n 43) to ground<br>) to ground | L11 (Pins 14-23 and 27-28) to grour                 | 000  | x 2    | 0,2  |              |

OZ976: 0°C < Tamb < 70°C, unless otherwise specified OZ976I:  $-40^{\circ}C < Tamb < 85^{\circ}C$ , unless otherwise specified

#### Notes:

- (1) CT: capacitor from CT (pin 34) to ground

- RT: resistor from RT (pin 41) to ground (2) LCT: capacitor from LCT (Pin 43) to ground RT: resistor from RT (pin 41) to ground

- (3) L0-L11: 50k $\Omega$  resistor is connected from L0-L11 (Pins 14-23 and 27-28) to ground A 4MHz resonator is connected to OSCA and OSCY

- (4) Reference voltage measured when CT, CLK, LCT & resonator are not active.

- (5) Denotes that parameter is guaranteed by design and not production tested. Serial

## PHASE ARRAY TOPOLOGY

### FUNCTIONAL BLOCK DIAGRAM DESCRIPTION

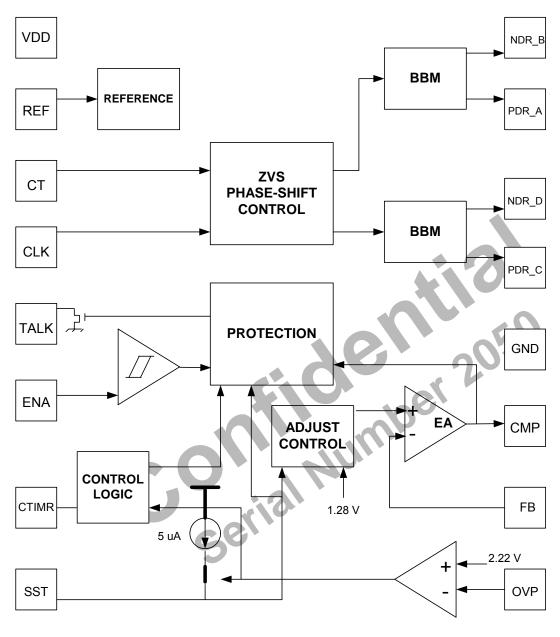

### OZ972 POWER CONTROLLER

The functional block diagram of the OZ972, Power Controller, is shown in Figure 2, page 10. The reference block receives a reference voltage from the REF pin and generates precise voltages for internal use. The drive circuit consists of four outputs, PDR\_A, NDR\_B, PDR\_C and NDR\_D. The drive circuit is designed to achieve a zerovoltage switching full-bridge application.

An error amplifier is provided to regulate the CCFL current. The Soft-Start Time (SST) circuit offers a gradual power increase to the CCFL during the ignition period. The Soft-Start Time (SST) is programmable by using an external capacitor coupled with the SST current source.

The over-voltage protection block limits the striking voltage for the CCFLs. The striking time is programmable by using an external capacitor with the CTIMR current source.

The Protection block intelligently differentiates between lamp ignition, normal operation, openlamp condition and broken lamp condition. The OZ972 communicates its' status to the OZ976 via the open drain TALK pin. The OZ972 is enabled when the ENA circuitry receives an enable signal from the OZ976 (ENA\_PP). The ADJ (Adjust) Control block provides an increased reference voltage during SST and a preset reference voltage once the lamp current is regulated.

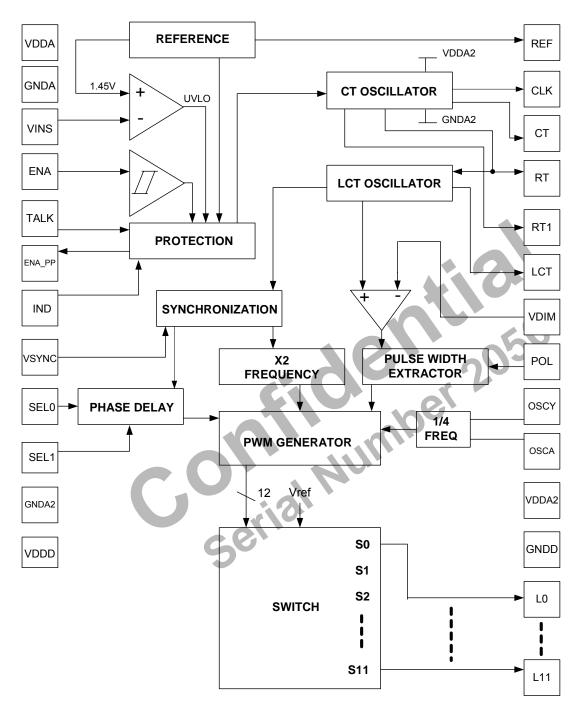

# OZ976 ARRAY HUB

The functional block diagram of the OZ976, Array Hub, is shown in Figure 3, page 11. A Precision Reference block provides reference voltages for both internal and external use.

The CT Oscillator circuit generates a userprogrammable operating frequency to the OZ972's by utilizing an external capacitor and timing resistor. To select the striking frequency, add an external resistor to RT1. The striking frequency is programmable.

The LCT Oscillator block utilizes a quarter of the current through the timing resistor (RT) to charge and discharge the external capacitor. This creates the LCT triangular waveform.

The Protection block monitors supply voltage, system enable and OZ972 status. Through VINS,

the OZ976 monitors the supply voltage and provides under-voltage lock out protection. When VINS and ENA pins are satisfied, the OZ972's are enabled through the ENA\_PP pin. When the supply voltage drops below specification, the OZ976 disables the inverters. The OZ976 operation is enabled through a TTL signal interface via the ENA circuitry.

The IND (Individual) pin is used to select the system protection mode. When IND is set high, all OZ972's act independent of each other. When IND is set low, all OZ972's act as a group. The TALK pin is used to monitor and communicate the status of the OZ972 power controllers to the OZ976.

A PWM signal is generated when VDIM exceeds a threshold voltage. A LCT oscillator generates a triangle waveform (1V to 3V) and accepts a VDIM DC voltage to generate the pulse width of the PWM dimming signals.

The Synchronize circuit selects the PWM frequency source from either the internal LCT or an external TTL signal to the VSYNC pin. If an external signal to VSYNC exists, that signal becomes the PWM frequency source. Otherwise, LCT is the PWM frequency source.

An x2 Frequency circuit doubles the PWM source frequency to eliminate low frequency flicker detected by the human eye. The Phase Delay circuit divides the PWM source period into multiple phases according to the number of lamps used in the application. The user selects the number of phases by selecting the logic levels of pins SEL0 and SEL1.

The Pulse Width Extractor extracts the PWM width from the output of LCT comparator. By selecting the POL (Polarity) logic level, the designer programs the relationship between VDIM and the panel brightness. Setting POL high, an increase in VDIM, will increase panel brightness. Conversely, setting POL low, a decrease in VDIM, will increase panel brightness. The PWM Generator circuit combines the Phase Delay, x2 Frequency and Pulse Width information to generate a set of new PWM waveforms with different phase delays.

An external resonator, connected to pins OSCY and OSCA, is needed to generate precise frequency and pulse width information to generate the PWM signals L0 to L11.

# **OZ972 POWER CONTROLLER FUNCTIONAL BLOCK DIAGRAM**

Figure 2

**OZ976 ARRAY HUB FUNCTIONAL BLOCK DIAGRAM**

Figure 3

### FUNCTIONAL DESCRIPTION

#### 1. Concept

The Phase Array is designed for a multiple-lamp CCFL panel. The OZ976 provides the reference voltage, enable signal, programmable synchronized operating frequency and PWM signals to each OZ972. In addition, when in common mode, the OZ976 monitors the status of the OZ972 via TALK. Each OZ972 operates its own lamps to reach the ultimate performance. This structure minimizes process tolerance and over-head cost while each lamp operates on its designed condition to provide the best performance.

#### 2. OZ972 Steady-State Operation

Referring to the schematic shown in Figure 4, page 17, the OZ972 drives a full-bridge power train where the transformer couples the energy from the power supply source to the CCFL. The switches in the bridge denoted as QA, QB, QC and QD are configured such that QA/QB and QC/QD are turned-on complementarily. The turn-on duration of QA/QD and QB/QC simultaneously determines the amount of energy delivered to the transformer and subsequently to the CCFL. The current in the CCFL is sensed and then regulated by adjusting the turn-on time (overlap) for both diagonal switches. This is accomplished through an error amplifier in the current feedback loop.

A voltage loop is used to regulate the output voltage to achieve the striking voltage, which is programmable by using a capacitor divider. Over voltage protection (OVP) limits transformer voltage under an open lamp condition. A softstart circuit ensures a gradual power increase to the lamp. The soft-start capacitor determines the rise rate of the voltage on the SST pin. The voltage level determines the on-time duration (overlap) of diagonal switches QA/QD and QB/QC.

The output drives for power MOSFET gates include, PDR\_A, NDR\_B, PDR\_C and NDR\_D, which output a complementary square pulse. The operation of the four switches is implemented with zero-voltage-switching to provide a high-efficiency power conversion.

#### 3. OZ972/OZ976 Interface Signals

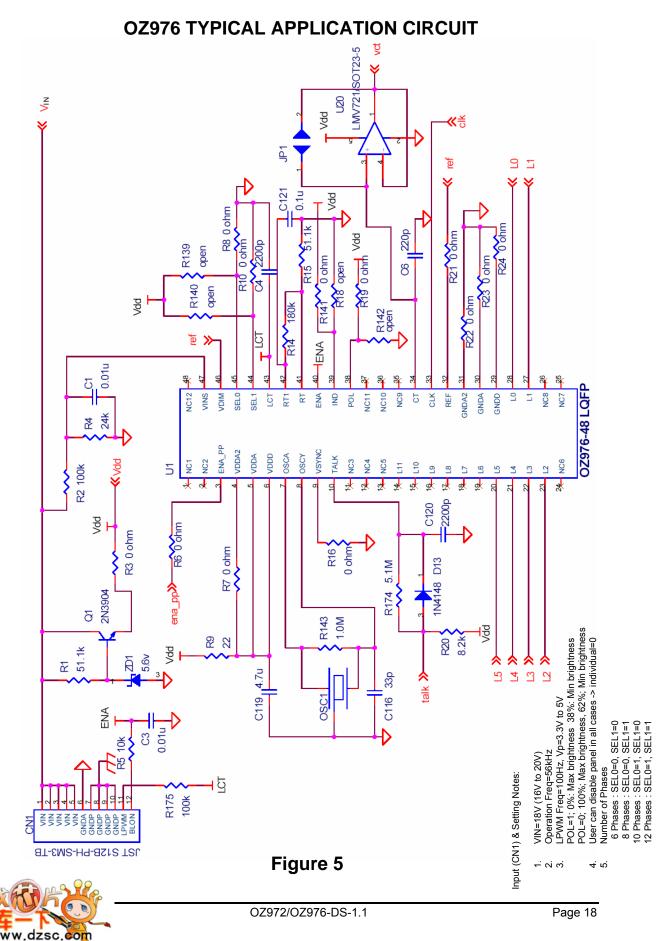

Referring to the schematics in Figures 4 and 5, pages 17 and 18, the OZ976 provides a reference voltage, enable signal, CLK and CT signals, to each OZ972. The OZ976 provides a precise reference voltage to the REF pin of each OZ972. All OZ972's are enabled by the OZ976 via the ENA PP pin. The CLK and CT signals are ch OZ972 to drive QA, QB, QC

and QD. All OZ972's are synchronized to one frequency. By sharing the reference voltage, CT and CLK, the difference in each lamp's performance is minimized. The OZ976 Controller senses the system power supply voltage. In addition, when in common mode, the OZ976 monitors OZ972 operation status via the TALK pin to determine whether to maintain normal operation or disable the inverters.

Once the system is powered-on, the OZ972 enters the Start-Up stage. Refer to Section 4 for more detailed information.

### 4. OZ972 Operation - Individual

The OZ972 operates in a constant-frequency mode. This eliminates any undesired interference between the inverter and LCD panel where interference is usually associated with variable-frequency designs.

#### Start- Up

Based on a 4MHz resonator, the OZ976 sends out a reference voltage and approximately 1ms later enables all the OZ972's. CLK and CT signals are sent out at this moment. After receiving a reference voltage and enable, CLK and CT signals, the OZ972 initiates operation. The result is a series of complementary output square pulses from PDR\_A, NDR\_B, PDR\_C and NDR\_D. The OZ972 holds the TALK pin low through an open-drain structure to inform the OZ976 to start the ignition period.

#### Soft Start Time to Normal Operation

An external resistor RT1 provides the flexibility to set a higher operating frequency for CCFL striking. In addition, the striking time is programmable through an external capacitor CTIMR. The Soft Start function gradually increases the energy delivered to the load from the diagonal switches during start-up. During Soft Start, the TALK pin is pulled low requesting the OZ976 to send a higher operating frequency to ignite the lamp. This process continues until the CCFL current is detected and reaches a regulated value. The output of the error amplifier, CMP, follows the feedback signal and controls the overlap of output drives QA/QD and QB/QC to maintain lamp current regulation. The operation of the four switches is implemented with zero-voltage switching to provide a highefficiency power conversion. Once the lamp current is sensed and regulated, the OZ972 releases TALK. When the TALK signal is released, the external resistor pulls TALK high and communicates to the OZ976 to switch the lamp to a normal operating frequency. The last OZ972 and the external pull-up resistor decide the TALK level.

#### Soft Start Time to Open Lamp

The striking voltage, or open-lamp voltage, is regulated through a voltage feedback loop. This voltage feedback loop is monitored by the OVP and controls the overlap of the output drivers to achieve a regulated striking voltage. Once the striking time has expired (CTIMR) and no lamp current is sensed, the OZ972 shuts down and releases TALK. The external resistor pulls TALK high informing the OZ976 to switch to a normal operating frequency. Approximately 20us later, the open lamp OZ972 pulls TALK low indicating to the OZ976 that an abnormal condition exists.

#### Normal Operation to Lamp Broken

A protection feature is needed to disable a damaged lamp during normal operation. Once the OZ972 senses the missing current signal through the error amplifier, the protection circuit shuts down the output drives. The OZ972 with the broken lamp then pulls TALK low informing the OZ976 of an abnormal situation.

#### Dimming

Dimming control of the inverter is implemented by adjusting the amount of energy processed and delivered to the CCFL. A PWM dimming control scheme is internally generated which provides a recommended PWM duty cycle of 0% to 85%. The OZ976 provides the phase delay PWM signals. The PWM frequency source can be provided externally from the system or internally by programming the LCT circuit.

#### 5. OZ972 Operation - Group

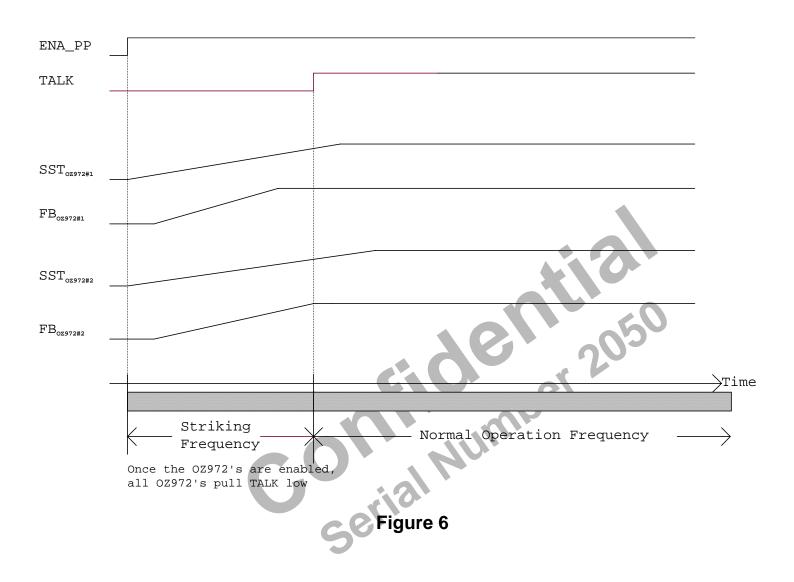

#### Soft-Start Time to Normal Operation

The OZ972s drive the power train to the CCFLs after receiving an enable signal. In the soft-start period, TALK is pulled low and a striking frequency is provided by the OZ976. Each OZ972 takes a different time to regulate the CCFL current due to lamp and component tolerances. When the lamp current is regulated on all OZ972's, the TALK signal is released. An external resistor pulls TALK high informing the OZ976 to provide a normal operating frequency to all lamps. Refer to Figure 6, page 19.

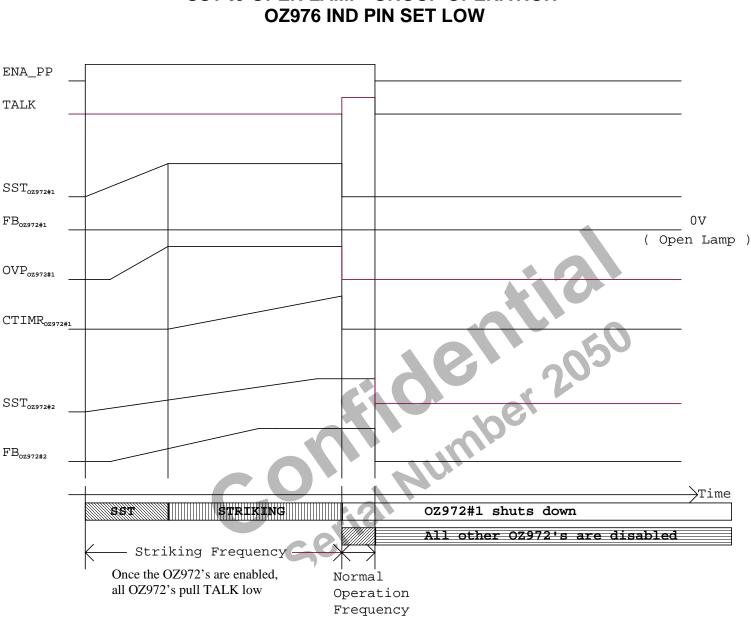

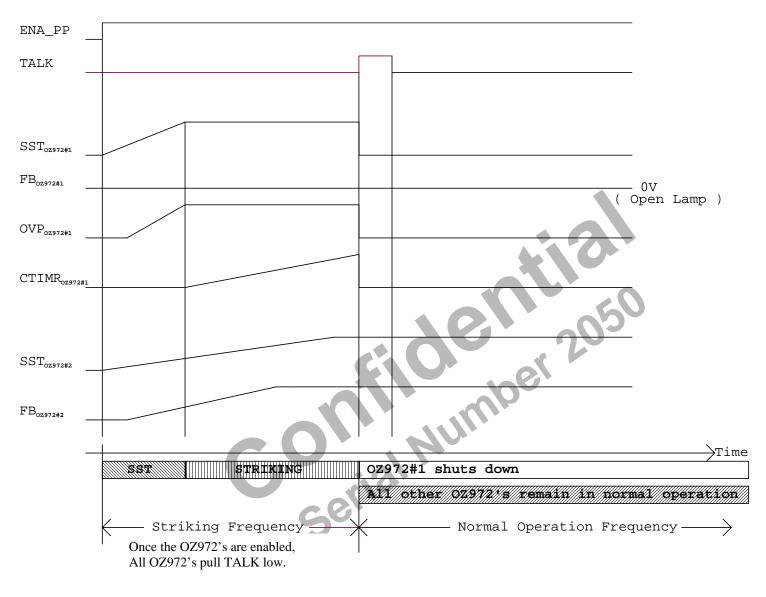

#### Soft-Start Time and Open Lamp

During the Soft Start Time, an OZ972 in open lamp condition attempts to ignite the CCFL. Once the striking time has expired and no lamp\_current is sensed, the OZ972 shuts down. By this time, the remaining OZ972's successfully regulate their lamp current and TALK is released. The external resistor pulls TALK high. The TALK rising edge informs the OZ976 to switch all lamps to a normal operating frequency. Approximately 20us later, the OZ972 with the open lamp pulls TALK low. The OZ976 will check the setting of the IND pin to decide whether to disable all the inverters. Refer to Figures 7 and 8 on pages 20 and 21, respectively.

#### Lamp Broken

When an OZ972 senses no CCFL current in normal operation, its protection block shuts down the circuit. The shut down behavior does not affect the operation of the other OZ972's and lamps. The OZ972, in shut down condition, pulls TALK low and informs the OZ976 of an abnormal condition. The OZ976 will check the setting of the IND pin and decide whether to disable all the inverters.

#### Dimming

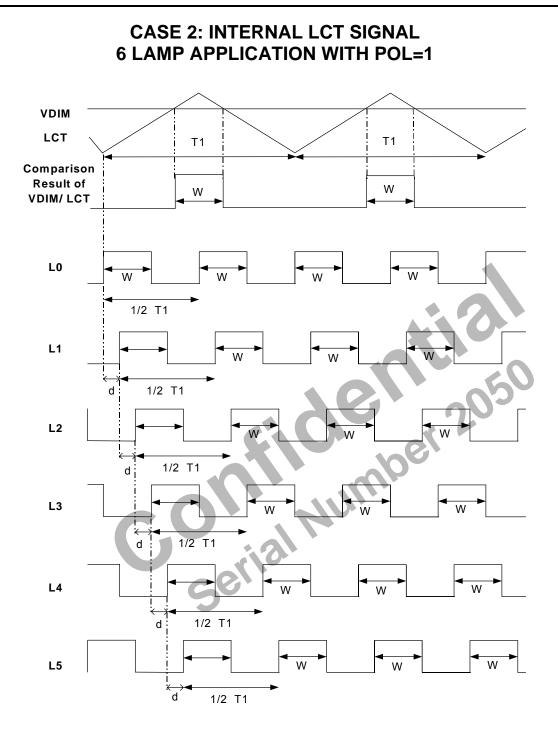

Refer to Cases 1 and 2 on pages 22 and 23, respectively. After TALK goes high and VDIM is within the LCT signal range of 1V to 3V, the OZ976 PWM Generator sends out a set of PWM signals to all the OZ972s. The VDIM voltage level and LCT signal decide the Pulse Width of the PWM dimming signals. The PWM frequency is decided by the internal LCT signal or external VSYNC signal. Each PWM signal has the same Pulse Width and frequency. Each signal has an equal amount of phase delay between them.

The delay time is determined by the following equations:

Case 1: External VSYNC Signal

T2

2 x Number of Phases

Case 2: Internal LCT Signal

T1

Delay Time =

Delay Time =

2 x Number of Phases

Each OZ972 adjusts the power delivered to its corresponding lamp following the PWM signal. This phase shift dimming control method minimizes the ripple current on the power line.

#### 6. Protection

During the ignition period, open-lamp protection is provided through both CTIMR and OVP. This ensures that a rated voltage is achieved and a required timing period is satisfied. Removal of the CCFL during normal operation will trigger the error amplifier output and shut down the OZ972.

### 7. CTIMR-CCFL Ignition Time

The ignition time varies for CCFLs, depending on their length, diameter, module package, manufacturer and temperature. OZ972 provides a flexible design where a capacitor is connected to the CTIMR pin to set the maximum striking time. When the OVP pin reaches a 2.22V threshold, the CTIMR capacitor starts to charge. When the CTIMR has expired (CTIMR capacitor voltage reaches approximately 3V) and no current is sensed, the OZ972 shuts down. An approximation of the timing calculation is:

T[second] = C[uF]

This capacitor remains reset at no charge if the lamp is connected and in normal operation.

#### 8. OVP

The OVP threshold is set at 2.22V nominal. When the output voltage reaches the threshold, it commands the QA/QD and QB/QC switches to maintain a regulated striking voltage. This ensures that the output has sufficient striking voltage while operating the transformer safely.

#### 9. OZ972 ENA

A logic high TTL signal from the OZ976 to the ENA pin of the OZ972 enables the power controllers. A logic low signal to the ENA pin will disable the operation of the inverter. Toggling this signal resumes the operation of the OZ972.

#### 10. Soft-Start Time -- SST

The soft-start function is provided with a capacitor connected to SST pin. The SST provides a rate of rise for the pulse width where diagonal switches are turned on. This function reduces in-rush current and prevents unnecessary stress to both the CCFL and the transformer.

### 11. Error Amplifier

CCFL current is regulated through the error amplifier. It also provides the intelligence of differentiating open-lamp striking versus removing the lamp during normal operation. The non-inverting reference is at 1.28V nominal.

### 12. Operating Frequency

The programmable operating frequency is decided by OZ976. CT and CLK signals are

necessary for OZ972 operation. The OZ972 combines the CLK, CT and SST or CMP signals to drive the four output drives.

#### 13. Output Drives

The four power MOSFET gate output drives are designed so that switches QA/QB and QC/QD never turn on simultaneously. The configuration prevents any shoot-through issue associated with bridge-type power conversion applications. By adjusting the overlap conduction between QA and QD, QB and QC, the CCFL current regulation is achieved. The overlap is adjusted when the power source voltage varies. The four output drive pins provide drive to two P-channel level shifters and two direct gate drive N-channel MOSFETs.

### 14. OZ976 Operation Principle

Referring to Figures 1 (page 8) and 5 (page 18), the OZ976 provides the DC reference voltage, enable signal, synchronized operating frequency, PWM dimming signals and protection services to each OZ972. Each OZ972 provides operating status to the OZ976 through TALK.

### 15. OZ976 Protection Block

#### VINS

The OZ976 provides VINS to sense the input power supply voltage to the inverter. When under-voltage lock out is triggered, the OZ976 disables the OZ972's through the ENA\_PP pin.

#### ENA

A logic high TTL signal to the ENA pin enables the operation of the IC. A logic low signal to the ENA pin disables the operation of the inverter. Toggling this signal allows the turn-on and turnoff of the inverter.

#### IND (Individual) and TALK

The IND feature is user programmable. When IND is set high, all OZ972s work individually. In this situation, when a lamp is damaged or open, the corresponding OZ972 will shut down and pull TALK low, indicating to the OZ976 that an abnormal situation exists. The OZ976 will ignore the falling edge of TALK and maintain system operation. When IND is set low, all OZ972s work as a group. Once the OZ976 detects a TALK falling edge, the OZ976 pulls ENA\_PP low to disable all the inverters. Refer to Figures 7 and 8 on pages 20 and 21, respectively.

#### ENA\_PP

The OZ976 ENA\_PP pin connects to all ENAs of OZ972. When VINS, ENA, IND and TALK are satisfied, ENA\_PP goes high to enable the operation of the OZ972s. The system will be disabled when VINS is in an under-voltage lock out condition or ENA is low. In addition, when TALK has a falling edge with IND set low, ENA\_PP goes low and disables the system. In this condition, only when VINS and ENA are satisfied, toggling VDDA will resume system operation.

#### 16. Operation Frequency

A resistor RT and capacitor CT determine the operating frequency of the OZ976. The frequency is calculated as follows:

$$f_{CLK[KHz]} = \frac{675 \cdot 10^3}{C_T[pF] \cdot R_T[k\Omega]}$$

The OZ976 also provides an optional striking frequency if desired. When RT1 is used, it is connected in parallel with RT during the ignition period, and provides a higher frequency for striking. After enable, OZ976 detects TALK pin's first rising edge and RT1 is disconnected.

CT is a saw-tooth waveform and its frequency is double the  $f_{CLK}$  operation frequency. CLK is a square waveform and its frequency is the operation frequency. Both of these signals are used by the OZ972 to control the output drivers, PDR\_A, NDR\_B, PDR\_C and NDR\_D.

#### **17. Reference Voltage**

OZ976 is the voltage source providing all OZ972 the reference voltage through REF pin. All OZ972s follow the REF voltage and generate internal references. The reference voltage is activated approximately 1ms before ENA\_PP goes high and it lasts 1ms after ENA\_PP goes low. The time delay relates to the resonator frequency of OSCA and OSCY.

#### **18. PWM Dimming Control**

OZ976 provides PWM dimming signals to each OZ972 with an equal phase delay.

#### Internal LCT Frequency

The internal pre-programmed PWM frequency T1 (see Case 2, page 23) is determined by a capacitor connected to the LCT pin. An approximation of the frequency can be calculated by:

f<sub>LCT</sub>[Hz] = \_\_\_\_\_

#### C<sub>LCT</sub>[nF]∙R<sub>T</sub>[kΩ]

$102 \bullet 10^3$

OZ972/OZ976

The peak and valley of the LCT signal is nominally 3V and 1V respectively. The VDIM signal is compared to the triangle wave in LCT and yields a proper pulse width to modulate the CCFL current. By programming POL, the positive or negative pulse width will be duplicated and imposed on the PWM signal. The designer defines the relationship between VDIM and panel brightness. Setting POL high, an increase in VDIM, will increase the panel brightness. Conversely, setting POL low, a decrease in VDIM, will increase the panel brightness.

#### PWM Frequency

Through VSYNC, PWM signals can be synchronized with an external control signal with a TTL level frequency range from 65Hz to 180Hz. If a VSYNC signal does not exist, the OZ976 uses the LCT signal to synchronize the PWM signals. All PWM signals are synchronized with either the internal (LCT) or external (VSYNC) signal. The PWM signals are twice the frequency of the internal or external signal.

#### **PWM Dimming Signals**

The PWM dimming signal frequency is extracted from either an internal LCT signal or from the external VSYNC signal. The pulse width of PWM dimming signal comes from the comparison result of LCT and VDIM. There is a fixed phase delay between sequential PWM dimming signals. The PWM Generator generates a new set of PWM dimming signals resulting from the combination of Pulse Width, X2 PWM dimming frequency and Phase Delay. All PWM signals have the same pulse width and frequency. The only difference among the PWM signals is the phase delay, which is determined by the PWM dimming period divided by the number of phases. No two PWM signals have the same phase shift amount.

#### SEL0 and SEL1

The SEL0 and SEL1 pins are used to select the number of lamps, from 6, 8, 10 and 12.

| Table 1. OZ976 Phase Select Log |

|---------------------------------|

|---------------------------------|

| SEL0 | SEL1 | No. of Phases |

|------|------|---------------|

| 0    | 0    | 6             |

| 0    | 1    | 8             |

| 1    | 0    | 10            |

| 1    | 1    | 12            |

#### L0 to L11

L0 to L11 are the PWM signal output pins. All of the outputs are a 3-state buffer.

#### 19. Resonator

A 4MHz resonator is used to provide a precise Pulse Width and frequency to the PWM Generator in order to generate the PWM dimming signals. OSCA and OSCY pins are provided to connect a resonator.

| Resonator | LCT/VSYNC         |  |  |

|-----------|-------------------|--|--|

|           | Minimum Frequency |  |  |

| 4MHz      | 61Hz              |  |  |

| 3.59MHz   | 55Hz              |  |  |

| 3MHz      | 46Hz              |  |  |

continuer 2050 Serial Number 2050

### **OZ972 TYPICAL APPLICATION CIRCUIT**

Note: Input LPWM signal to CN1 pin 11 (LPWM)

# SST TO NORMAL OPERATION

SST to OPEN LAMP- GROUP OPERATION

Figure 7

Figure 8

#### **CASE 1: EXTERNAL VSYNC SIGNAL** 6 LAMP APPLICATION WITH POL=1 VDIM LCT Τ1 Τ1 Comparison Result of W W VDIM/LCT Т1 Τ1 External VSYNC Τ2 Τ2 L0 W W W 1/2 T2 L1 W W w 1/2 T2 d L2 W W 1/2 T2 d L3 W W W 1/2 T2 d L4 w W W ۱۸ 1/2 T2 d L5 W W W d = 1/2 \* T2 \* 1/6 1/2 T2 d

OZ972/OZ976-DS-1.1

### PACKAGE INFORMATION - 16-Pin SOP: OZ972G Power Controller

# PACKAGE INFORMATION - 48-Pin LQFP: OZ976T Array Hub

| SYMBOL | MILLIMETER |      | INCH |       |       |       |

|--------|------------|------|------|-------|-------|-------|

| STWBUL | MIN.       | NOM. | MAX. | MIN.  | NOM.  | MAX.  |

| А      | 1.40       | 1.50 | 1.60 | 0.052 | 0.059 | 0.063 |

| A2     | 1.35       | 1.40 | 1.45 | 0.050 | 0.055 | 0.057 |

| b      | 0.17       | 0.22 | 0.27 | 0.007 | 0.009 | 0.011 |

| D1     | 6.90       | 7.00 | 7.10 | 0.272 | 0.276 | 0.280 |

| D      | 8.90       | 9.00 | 9.10 | 0.350 | 0.354 | 0.358 |

| E1     | 6.90       | 7.00 | 7.10 | 0.272 | 0.276 | 0.280 |

| E      | 8.90       | 9.00 | 9.10 | 0.350 | 0.354 | 0.358 |

| е      | -          | 0.50 | -    | -     | 0.020 | -     |

# **IMPORTANT NOTICE**

No portion of O<sub>2</sub>Micro specifications/datasheets or any of its subparts may be reproduced in any form, or by any means, without prior written permission from O<sub>2</sub>Micro.

O<sub>2</sub>Micro and its subsidiaries reserve the right to make changes to their datasheets and/or products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

O<sub>2</sub>Micro warrants performance of its products to the specifications applicable at the time of sale in accordance with O<sub>2</sub>Micro's standard warranty. Testing and other quality control techniques are utilized to the extent O<sub>2</sub>Micro deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customer acknowledges that O<sub>2</sub>Micro products are not designed, manufactured or intended for incorporation into any systems or products intended for use in connection with life support or other hazardous activities or environments in which the failure of the O<sub>2</sub>Micro products could lead to death, bodily injury, or property or environmental damage ("High Risk Activities"). O2Micro hereby disclaims all warranties, and O<sub>2</sub>Micro will have no liability to Customer or any third party, relating to the use of O<sub>2</sub>Micro products in connection with any High Risk Activities.

Any support, assistance, recommendation or information (collectively, "Support") that O<sub>2</sub>Micro may provide to you (including, without limitation, regarding the design, development or debugging of your circuit board or other application) is provided "AS IS." O<sub>2</sub>Micro does not make, and hereby disclaims, any warranties regarding any such Support, including, without limitation, any warranties of merchantability or fitness for a particular purpose, and any warranty that such Support will be accurate or error free or that your circuit board or other application will be operational or functional. O2Micro will have no liability to you under any serial Number legal theory in connection with your use of or reliance on such Support.

#### COPYRIGHT © 2004, O2Micro International Limited