## **DESCRIPTION**

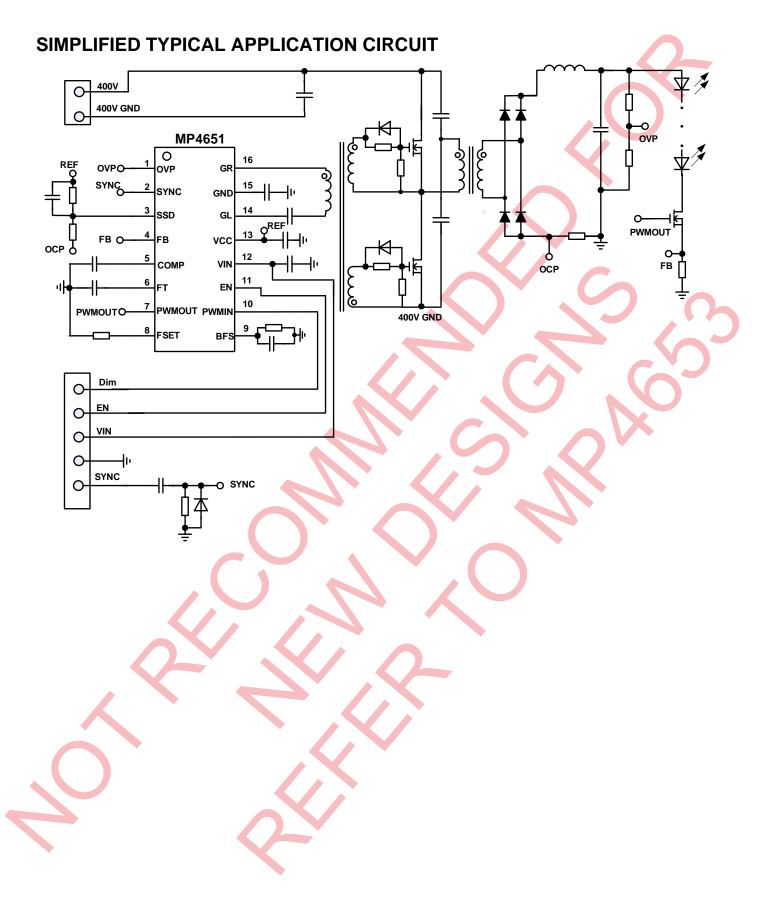

The MP4651 is a high performance off-line LED driver designed for powering the LEDs especially for high power isolated application.

The MP4651 utilizes fixed operating frequency PWM control. It outputs two 180 degree phase shifted driving signals for various external power stages. Its enhanced 9V gate driver provides adequate driving capability for the external MOSFETs and directly drives the external gate driving transformer.

The MP4651 implements fast and high contrast ratio PWM dimming to the LEDs. PWM dimming is controlled with either an external DC voltage or PWM signal. The burst dimming frequency can be synchronized to an external synchronizing signal.

The Built-in fault management features include open LED protection, short LED protection, over voltage protection, and over temperature protection. The protection interface is flexible for various setups and is easy to use. MP4651 integrates a delay timer to recover the system.

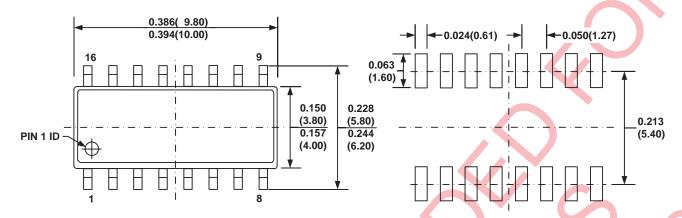

The MP4651 is available in a 16-pin SOIC package.

## **FEATURES**

- 9V Enhanced Gate Driver

- Programmable Fixed Operating Frequency

- Input Voltage Range from 9V to 30V

- DC or PWM Input Dimming Control

- Burst Dimming Frequency Synchronization

- Smart Fault Protection Interface

- Built-in Fault Management

- Built-in Delay Timer for System Recovery

- Available in a SOIC16 Package

## **APPLICATIONS**

- LCD TV and LCD Monitor

- Flat Panel Video Displays

- LED Lighting Applications

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

The MP4651 is covered by US Patents 6,683,422, 6,316,881, and 6,114,814. Other Patents Pending.

© 2011 MPS. All Rights Reserved.

## ORDERING INFORMATION

| Part Number* | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|---------|-------------|----------------------------------------|

| MP4651ES     | SOIC16  | MP4651ES    | -20°C to +85°C                         |

\* For Tape & Reel, add suffix -Z (e.g. MP4651ES-Z) For RoHS Compliant Packaging, add suffix -LF (e.g. MP4651ES-LF-Z

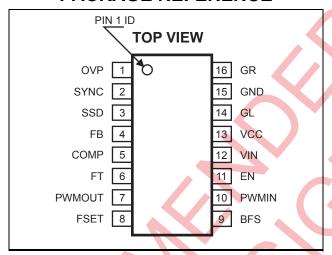

## PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| Input Voltage V <sub>IN</sub> | 35V                          |

|-------------------------------|------------------------------|

| GL, GR                        |                              |

| FB, SSD                       | 5.8V to +5.8V                |

| Other Pins                    |                              |

| Continuous Power Dissipation  | $(T_A = +25^{\circ}C)^{(2)}$ |

|                               | 2.5W                         |

| Junction Temperature          | 150°C                        |

| Lead Temperature (Solder)     | 260°C                        |

| Operating Frequency2          | 0kHz to 150kHz               |

| Storage Temperature           | 55°C to +150°C               |

| Recommended Operating C       | Conditions (3)               |

| Input Voltage V <sub>IN</sub> | 9V to 30V                    |

| Operating Frequency (Typical) | 50kHz                        |

Maximum Junction Temp. (T<sub>J</sub>) ...... +125°C

| Thermal Resistance (4 | $\theta_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|-----------------------|---------------|-------------------------|------|

| SOIC16                | 80            | 30                      | °C/W |

#### Notes:

- Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX)=(T_J(MAX)-$ T<sub>A</sub>)/ θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB

3

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                           | Symbol                     | Condition                               | Min  | Тур  | Max  | Units |  |

|-------------------------------------|----------------------------|-----------------------------------------|------|------|------|-------|--|

| Gate driver GL, GR                  |                            |                                         |      |      |      |       |  |

| Gate Pull-Down                      | $R_{GD}$                   |                                         |      | 2    |      | Ω     |  |

| Gate Pull-Up                        | $R_{GU}$                   |                                         |      | 4    |      | Ω     |  |

| Output Source Current               | I <sub>SOURCE</sub>        |                                         |      | 1    |      | Α     |  |

| Output Sink Current                 | I <sub>SINK</sub>          |                                         |      | 2    |      | Α     |  |

| Maximum Duty Cycle                  | D <sub>MAX</sub>           |                                         |      | 46%  |      |       |  |

| EN                                  |                            |                                         |      |      |      |       |  |

| EN Turn On Threshold                | $V_{EN-ON}$                |                                         | 2    |      |      | V     |  |

| EN Turn Off Threshold               | $V_{EN-OFF}$               |                                         |      |      | 1    | V     |  |

| Internal Pull-down Resistor         | R <sub>EN-IN</sub>         |                                         |      | 60   |      | kΩ    |  |

| <b>Brightness Dimming Control F</b> | lange                      |                                         |      |      |      |       |  |

| PWM Full Scale                      | $V_{PWM}$                  | DC input burst dimming                  | 1.1  | 1.2  | 1.3  | V     |  |

| PWM Logic Input Threshold           | $V_{TH	ext{-}PWM}$         | PWM dimming                             | 1.6  | 1.9  | 2.2  | V     |  |

| PWM Logic Input Hysteresis          | V <sub>TH-PWM-Hyst</sub>   | PWM dimming                             |      | 0.1  |      | V     |  |

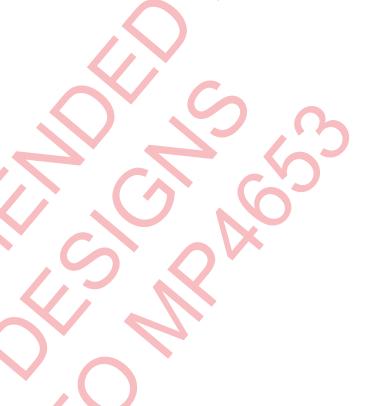

| Burst Frequency Set (BFS)           |                            |                                         |      |      |      |       |  |

| Source Current                      | I <sub>SRC(BFS)</sub>      | $V_{BFS} = 2V$                          | 120  | 140  | 170  | μΑ    |  |

| Lower Threshold                     | $V_{V(BFS)}$               |                                         | 2.2  | 2.4  | 2.6  | V     |  |

| Upper Threshold                     | V <sub>P(BFS)</sub>        |                                         | 3.3  | 3.55 | 3.8  | V     |  |

| Supply Current                      |                            |                                         |      |      |      |       |  |

| Supply Current (Enabled)            | I <sub>IN-EN</sub>         | No driver output                        |      | 1.5  | 2.5  | mA    |  |

| Supply Current (Disabled)           | I <sub>IN-OFF</sub>        | V <sub>IN</sub> =30V                    |      |      | 1    | μΑ    |  |

| Operating Frequency                 | f <sub>O</sub>             | 25kΩ FSET to GND                        | 46.5 | 50   | 53.5 | kHz   |  |

| Frequency Set Voltage               | $V_{FSET}$                 |                                         | 1.14 | 1.2  | 1.25 | V     |  |

| Output PWM Dimming Signal           | for LED (PWM)              | OUT)                                    |      |      |      |       |  |

| Logic High Voltage                  | V <sub>H-PWMOUT</sub>      | Normal Operation                        | 5V   | 6    | 6.5V | V     |  |

| Logic Low Voltage                   | V <sub>L-PWMOUT</sub>      | At Fault Condition,<br>25kΩ FSET to GND |      | 0.1  | 0.6V | V     |  |

| Output PWM Source Current           | I <sub>SOURCE</sub> PWMOUT | 100pF on PWMOUT pin                     |      | 3    |      | mA    |  |

| Output PWM Sink Current             | I <sub>SINK PWMOUT</sub>   | 100pF on PWMOUT pin                     |      | 20   |      | mA    |  |

| LED Current Feedback (FB)           |                            |                                         |      |      |      |       |  |

| Magnitude                           | V <sub>FB</sub>            |                                         | 0.57 | 0.6  | 0.63 | V     |  |

| Input resistance R <sub>FB IN</sub> |                            |                                         |      | 30   |      | kΩ    |  |

| Over Voltage Protection (OVP)       |                            |                                         |      |      |      |       |  |

| Over Voltage Protection Threshold   | V <sub>TH(OVP)</sub>       |                                         | 2.22 | 2.38 | 2.55 | V     |  |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                            | Symbol                              | Condition                                                                                          | Min  | Тур  | Max  | Units |  |  |

|--------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|

| Fault Timer (FT)                     |                                     |                                                                                                    |      |      |      |       |  |  |

| Threshold                            | $V_{th(FT)}$                        |                                                                                                    | 2.2  | 2.4  | 2.6  | V     |  |  |

| Source Current                       | I <sub>SOURCE(FT)</sub>             |                                                                                                    |      | 8    |      | μA    |  |  |

| Comp                                 |                                     |                                                                                                    |      |      |      |       |  |  |

| Clamp Voltage                        | $V_{COMP}$                          |                                                                                                    |      | 0.60 |      | V     |  |  |

| Reference Current                    | I <sub>COMP+</sub>                  |                                                                                                    |      | 20   |      | μA    |  |  |

| Pull Down Current at Fault Condition | I <sub>COMP-FAULT</sub>             | Fault Mode is triggered                                                                            |      | 30   |      | μA    |  |  |

| Burst Frequency Synchroniza          | tion (SYNC)                         |                                                                                                    | V/   |      |      |       |  |  |

| High logic level                     | V <sub>SYNC-H</sub>                 |                                                                                                    | 1.4  |      |      | V     |  |  |

| Low logic level                      | V <sub>SYNC-L</sub>                 |                                                                                                    |      |      | 0.7  | V     |  |  |

| Pulse width                          | t <sub>sync</sub>                   |                                                                                                    | 6    | 10   | 20   | μs    |  |  |

| Synchronizing Frequency              | f <sub>SYNC</sub>                   | DC input burst dimming,<br>Compared to the<br>frequency f <sub>BFS</sub> set by<br>BFS pin R and C | 110% | 120% |      | 75    |  |  |

| Fault Detection Threshold (SS        | Fault Detection Threshold (SSD, FB) |                                                                                                    |      |      |      |       |  |  |

| SSD Threshold                        | V <sub>SSD</sub>                    |                                                                                                    | 2.22 | 2.36 | 2.55 | V     |  |  |

| SSD Detection Delay Time             | T <sub>D SSD</sub>                  |                                                                                                    |      | 7    |      | μs    |  |  |

| FB threshold                         | V <sub>FB th</sub>                  |                                                                                                    | 1.1  | 1.2  | 1.3  | V     |  |  |

| FB Detection Delay Time              | T <sub>D</sub> FB                   |                                                                                                    |      | 7    |      | μs    |  |  |

| Output Gate Driver (VCC)             |                                     |                                                                                                    |      |      |      |       |  |  |

| Voltage                              | V <sub>VCC</sub>                    | No load                                                                                            | 8.7  | 9.7  | 10.5 | V     |  |  |

| Current                              | I <sub>vcc</sub>                    |                                                                                                    |      | 20   |      | mA    |  |  |

# **PIN FUNCTIONS**

| Pin# | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | OVP    | Over Voltage Protection. The output voltage is sensed by this pin through a voltage divider from the anode of the LED to ground. If the voltage at OVP exceeds 2.38V for 7us, the Fault Mode is triggered.                                                                                                                                                                                                                                                                                                                     |

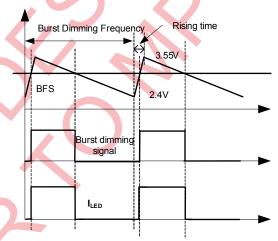

| 2    | SYNC   | Synchronization for the burst dimming frequency. Applying a synchronizing signal with a narrow pulse on this pin will synchronize the burst frequency on BFS pin. The frequency of the synchronizing signal should be higher than the frequency set by BFS pin.                                                                                                                                                                                                                                                                |

| 3    | SSD    | Short String Detection. A comparator is integrated in this pin for short string protection. If the voltage on this pin gets lower than 2.36V for 7us, the Fault Mode is triggered.                                                                                                                                                                                                                                                                                                                                             |

| 4    | FB     | LED Current Feedback Input. Connect this pin to the cathode of the LED and shunt a sense resistor to ground. The internal error amplifier sinks a current from the COMP pin proportional to the absolute value of the voltage at this pin. The average voltage at this pin is regulated to 0.6V reference voltage.  The voltage on this pin is also used for short string detection. When the voltage on this pin gets higher than 1.2V for 7us, the IC recognizes this as short string condition and triggers the Fault Mode. |

| 5    | COMP   | Feedback Compensation Node. Connect a compensation capacitor or a R-C network from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6    | FT     | Fault Timer. Connect a timing capacitor from this pin to GND to set the fault timer to recover the system. When the voltage on this pin gets higher than the 2.38V threshold, the IC recovers.                                                                                                                                                                                                                                                                                                                                 |

| 7    | PWMOUT | This pin outputs the PWM dimming signal to LED for fast dimming. At Fault Mode, the PWMOUT is pulled down.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8    | FSET   | Frequency Set. Connect a resistor from this pin to GND. This resistor sets the operating frequency of the MP4651. A 25kOhm resistor sets the operating frequency at typical 50kHz.                                                                                                                                                                                                                                                                                                                                             |

| 9    | BFS    | Burst Frequency Set. Connect a resistor in parallel with a capacitor from BFS to GND. The resistor and capacitor programs the burst dimming frequency. If the burst dimming is to be controlled by an external PWM signal, pull up BFS to VCC through a $20 k\Omega$ resistor and apply the PWM signal to the PWMIN pin.                                                                                                                                                                                                       |

| 10   | PWMIN  | Burst-Mode (Digital) Brightness Control Input. For DC input burst dimming, the voltage range from 0 V to 1.2V at PWMIN linearly sets the burst-mode duty cycle from 0 to 100%. For external PWM input dimming, directly apply the logic signal on this pin. The MP4651 has positive dimming polarity.                                                                                                                                                                                                                          |

| 11   | EN     | Enable Input. Pull EN high to turn on the chip, and pull EN low to turn it off.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12   | VIN    | Supply voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13   | VCC    | Linear Regulator Output and Bias Supply of the Gate Driver. It provides the supply for the gate driver and also the external control circuit, the typical value is 9.7V. Bypass VCC with a 1µF or larger ceramic capacitor.                                                                                                                                                                                                                                                                                                    |

| 14   | GL     | Driving signal output, 180 degree phase shifted of GR                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15   | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16   | GR     | Driving signal output, 180 degree phase shifted of GL                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

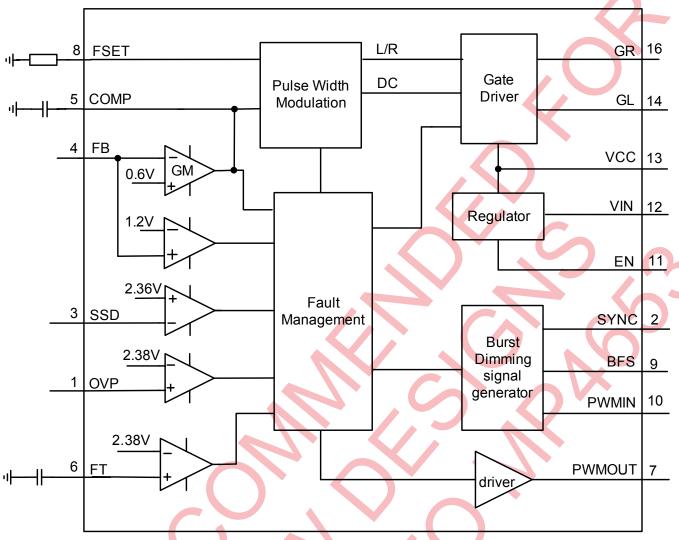

# **BLOCK DIAGRAM**

Figure 1—MP4651 Block Diagram

#### **DESIGN INFORMATION**

## **Steady State and Enable Control**

The MP4651 is a fixed operating frequency offline LED driver, specifically designed for the high power isolated applications. Powered by 9V to 30V input supplies, the MP4651 outputs two 180 degree phase shifted driving signals for the external power stages. Its enhanced 9V gate driver provides adequate driving capability to the external MOSFETs and directly drives the external gate driving transformer.

The MP4651 utilizes Pulse Width Modulation control to the system. The operating frequency is set by an external resistor connected from FSET pin to GND. The LED current is fed back to FB pin and compared with internal 0.6V reference Together voltage. with the integrator compensation network on COMP pin, which is connected to the output of the error amplifier, the output LED current is accurately regulated. The voltage on COMP pin is compared with the internal oscillator and generates duty cycle modulated signals to control the external power switches.

The system power is controlled by EN pin. When the chip is enabled, the built-in regulator for VCC is powered up and the internal circuit starts.

#### **Brightness Control**

MP4651 implements burst dimming (digital brightness) of the LED. The MP4651 has a built-in burst oscillator which can generate a triangle waveform on the BFS pin. Burst dimming can be achieved by either a DC voltage input or external PWM signal.

When burst dimming with a DC input voltage, add a capacitor in parallel with a resistor on BFS pin to set the burst frequency and apply the DC voltage on the PWMIN pin to program the burst duty cycle.

The burst frequency can be synchronized to an external frequency. Applying a synchronizing frequency signal with narrow pulse on SYNC pin can synchronize the burst frequency. The synchronizing frequency should be higher than the burst frequency set by the BFS pin. Please refer to SYNC pin description for details.

When burst dimming with external PWM signal, pull up BFS pin to VCC through a  $20k\Omega$  resistor and apply the PWM signal on PWMIN pin.

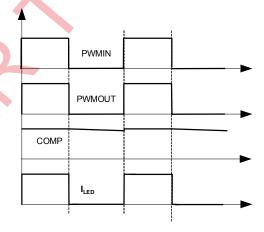

## Fast and High Contrast Ratio PWM Dimming

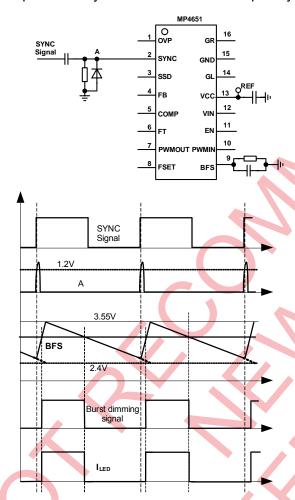

The MP4651 implements fast and high contrast ratio PWM dimming to the WLED. The PWM dimming signal (controlled by a DC input voltage or direct PWM signal) is outputted on PWMOUT pin to drive the external MOSFET in series with the LEDs, therefore the LED current rises up immediately when PWM dimming signal is effective.

The PWM dimming signal is also used to disconnect the compensation network (on comp pin, a capacitor or a R-C network) from the error amplifier at PWM off interval, and so that the compensation network voltage is hold at this interval and gets nearly immediately to the steady state value when PWM signal is effective. It eliminates the control loop response time and realizes fast dimming.

The MP4651 strictly controls the sequence of the driving signals. Both the sequence of GL and GR signals and the delay time between PWM dimming signal and driving signals are accurately fixed. Therefore, for each time of PWM dimming, the driving signals are exactly the same and so does the output power delivered to the load. It eliminates the possibility of flicker at small PWM dimming pulse and thus realizes the high contrast ratio PWM dimming.

Figure 2—Fast and High Contrast Ratio PWM Dimming

© 2011 MPS. All Rights Reserved.

#### **Fault Protection**

System fault management facilities include the over voltage protection, short string protection and a delay timer for system recovery.

The output voltage is monitored by the OVP pin through a voltage divider. Once the voltage on OVP pin exceeds 2.38V for 7us, the MP4651 recognizes this as open condition and triggers Fault Mode.

The SSD pin is used for short string detection. When the voltage on SSD pin gets lower than 2.36V for 7us, the MP4651 recognizes this as short string condition and triggers the Fault Mode.

FB pin also functions as short string protection. When the voltage on FB pin is higher than 1.2V for 7us, the IC triggers the Fault Mode.

At Fault Mode, the outputs of the gate drivers GL and GR are disabled, the PWMOUT signal is pulled down and the COMP capacitor is discharged by a 30uA sourcing current. The fault timer is started. An 8uA current source charges the FT capacitor, and when FT voltage hits 2.38V, system recovers. It enables the output driving signals, releases the COMP, resets the fault flag and pulls down the FT pin.

#### APPLICATION INFORMATION

## Pin 1 (OVP):

Over Voltage Protection: This pin is used for over voltage protection. The output voltage is monitored by this pin and when the voltage on this pin exceeds 2.38V for 7us, the Fault Mode is triggered.

#### Pin 3 (SSD):

Short String Detection: This pin is used for short string protection, when the voltage on this pin gets lower than 2.36V for 7us, the IC treats it as short string condition and triggers the Fault Mode.

## Pin 4 (FB):

<u>LED Current Feedback.</u> This pin is used for LED current regulation. The voltage on this pin is regulated with 0.6V average value.

FB pin also functions as short sting protection. When the voltage on FB gets higher than 1.2V for 7us, the IC triggers the Fault Mode.

## Pin 5 (COMP):

This pin is used for compensation. Connect a 1~47nF capacitor from COMP to GND. This cap should be X7R ceramic. The value of this cap determines the stability of the LED current regulation.

#### Pin 6 (FT):

Connect a capacitor from this pin to GND to set the fault timer. It sets the time to recover the system when a fault condition is detected.

$$T_{FT} = \frac{2.38V \times C_{FT}}{8uA}$$

A 10nF capacitor on FT sets the delay time around 3ms

#### Pin 8 (FSET):

Connect a resistor from this pin to GND to set the operating frequency (f<sub>o</sub>). The value for this resistor R1 is calculated by

$$R1 = \frac{1.25 \times 10^9}{f_0}$$

For R1 =  $25k\Omega$ , operating frequency will be 50kHz.

## Pin 7 (PWMOUT):

This pin outputs the burst dimming signal to the LED for fast PWM dimming. Connect this pin directly to the gate of the dimming MOSFET in series of the LED.

## Pin 10 (PWMIN):

This pin is used for burst brightness control. For DC input burst dimming, the DC voltage on this pin controls the burst percentage on the output. The signal is filtered for optimal operation. A voltage ranging from 0 to 1.2V on PWMIN programs the burst dimming duty cycle from 0 to 100%.

For direct PWM burst dimming, Pull BFS high to VCC through a  $20k\Omega$  resistor and connect PWMIN pin to a logic level PWM signal. Logic High is Burst On and a logic Low is Burst Off.

### Pin 9 (BFS):

BFS pin is used to set the burst dimming frequency. Connect a resistor ( $R_{BFS}$ ) in parallel with a capacitor ( $C_{BFS}$ ) on this pin to set the burst dimming frequency, as shown in figure 3.

Figure 3—Burst Mode with DC Input Voltage at PWMIN Pin

These values are determined as follows:

Set a percentage of the rising time, where:

$$\mathsf{D}_{\mathsf{rise}} = \mathsf{t}_{\mathsf{rise}} \times \mathsf{f}_{\mathsf{Burst}}$$

R<sub>BFS</sub> and C<sub>BFS</sub> are determined by:

$$R_{\text{BFS}} \approx 21.16k \left(\frac{1}{D_{\text{rise}}} - 1\right) + 21.43k$$

$$C_{\text{BFS}} = \frac{1 - D_{\text{rise}}}{f_{\text{Burst}} \times R_{\text{BFS}} \times 0.405}$$

For  $D_{rise}$ = 0.1,  $f_{Burst}$  = 200Hz, then  $R_{BFS}$  = 212k,  $C_{BFS}$  = 52nF

For direct PWM burst dimming, pull BFS high to VCC through a  $20k\Omega$  resistor and apply the PWM signal to PWMIN pin.

## Pin 2 (SYNC):

Burst frequency synchronization. This pin is used to synchronize the burst dimming frequency. Applying a synchronizing frequency signal with small pulse will synchronize the burst frequency.

Figure 4—Synchronized DC Input Burst Dimming

Figure 4 shows the synchronized DC input burst dimming. The synchronizing signal is filtered by a high pass filter. Its rising edge is caught and used for synchronizing the triangle waveform on

BFS pin. The synchronizing frequency should be higher than that set by BFS pin and the amplitude of the synchronizing signal should be higher than 1.4V.

Table 1—Function Mode

| Function                                                              | Pin Connection |                                       |                  |  |

|-----------------------------------------------------------------------|----------------|---------------------------------------|------------------|--|

| Function                                                              | PWM            | BFS                                   | SYNC             |  |

| Burst Mode with DC<br>Input Voltage                                   | 0V to<br>1.2V  | C <sub>BFS</sub> , R <sub>BFS</sub>   | GND              |  |

| Burst Mode with DC<br>Input Voltage and<br>Synchronizing<br>frequency | 0V to<br>1.2V  | $C_{BFS}$ , $R_{BFS}$                 | R,C,D<br>network |  |

| Burst Mode with<br>External PWM Source                                | PWM            | To VCC<br>through<br>20kΩ<br>resistor | GND              |  |

Burst Brightness Polarity: 100% duty cycle at PWM voltage 1.2V.

## Pin 11 (EN):

Pull this pin high to enable the chip, and pull it low to disable the chip.

## Pin 12 (VIN):

Supply voltage input. Bypass the supply voltage with a 0.1uF or greater ceramic cap. This cap should be placed close to the IC.

## Pin 13 (VCC):

This pin provides the gate driver supply voltage, its typical value is 9.7V. Connect a 1uF or greater ceramic capacitor on this pin to bypass the supply voltage. This voltage is also used to supply the external control circuit.

#### Pin 14(GL), Pin 16 (GR):

Gate driving signals output. GL and GR are 180 degree phase shifted driving signals. With its enhanced driving capability, GL and GR are able to directly drive the externally MOSFET in the off-line system through a gate driving transformer. Connect two  $5\Omega$  resistors in series with GL and GR to reduce the EMI noise.

A 2.2nF Y capacitor is recommended to be placed between the primary reference ground and secondary reference ground.

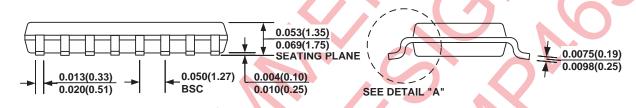

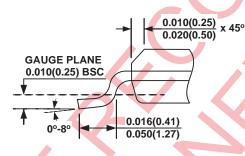

### PACKAGE INFORMATION

#### SOIC16

**TOP VIEW**

RECOMMENDED LAND PATTERN

**FRONT VIEW**

SIDE VIEW

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AC.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.