January 2006

# LM4935 Boomer<sup>®</sup> Audio Power Amplifier Series Audio Sub-System with Dual-Mode Stereo Headphone & Mono High Efficiency Loudspeaker Amplifiers and Multi-Purpose ADC

## **1.0 General Description**

The LM4935 is an integrated audio subsystem that supports both analog and digital audio functions. The LM4935 includes a high quality stereo DAC, a mono ADC, a multipurpose SAR ADC, a stereo headphone amplifier, which supports output cap-less (OCL) or AC-coupled (SE)modes of operation, a mono earpiece amplifier and a mono high efficiency loudspeaker amplifier. It is designed for demanding applications in mobile phones and other portable devices.

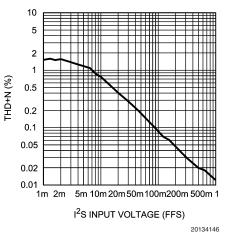

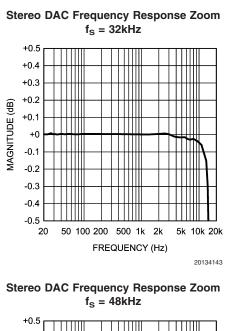

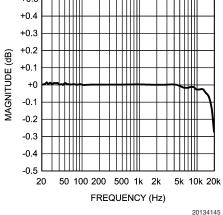

The LM4935 features a bi-directional I<sup>2</sup>S serial interface for full range audio and an I<sup>2</sup>C or SPI compatible interface for control. The stereo DAC path features an SNR of 88 dB with an 18-bit 48 kHz input. In SE mode the headphone amplifier delivers at least 33 mW<sub>BMS</sub> to a  $32\Omega$  single-ended stereo load with less than 1% distortion (THD+N) when  $A\_V_{\rm DD}$  = 3.3V. The mono earpiece amplifier delivers at least 115  $mW_{\text{BMS}}$  to a 32  $\!\Omega$  bridged-tied load with less than 1% distortion (THD+N) when  $A_V_{DD}$  = 3.3V. The mono speaker amplifier delivers up to 600 mW into an  $8\Omega$  load with less than 1% distortion when  $LS_{DD} = 3.3V$  and up to 1.3W when  $LS_V_{DD}$  = 5.0V. The LM4935 also contains a general purpose SAR ADC for housekeeping duties such as battery and temperature monitoring. This can also be used for analog volume control of the output stages and can trigger interrupt events.

The LM4935 employs advanced techniques to reduce power consumption, to reduce controller overhead to speed development time and to eliminate click and pop. Boomer audio power amplifiers were designed specifically to provide high guality output power with a minimal amount of external components. It is therefore ideally suited for mobile phone and other low voltage applications where minimal power consumption, PCB area and cost are primary requirements.

## 2.0 Applications

- Smartphones

- Mobile Phones and Multimedia Terminals

- PDAs, Internet Appliances and Portable Gaming

- Portable DVD/CD/AAC/MP3 Players

- Digital Cameras/Camcorders

## 3.0 Key Specifications

- P<sub>HP (AC-COUP)</sub> @ A\_V<sub>DD</sub> = 3.3V, 32Ω, 1% THD 33 mW

- P<sub>HP (OCL)</sub> @ A\_V<sub>DD</sub> = 3.3V, 32Ω, 1% THD 31 mW 1.3 W

- P<sub>LS</sub> @ LS\_V<sub>DD</sub> = 5V, 8Ω, 1% THD

- P<sub>LS</sub> @ LS\_V<sub>DD</sub> = 4.2V, 8Ω, 1% THD 900 mW 600 mW

- P<sub>LS</sub> @ LS\_V<sub>DD</sub> = 3.3V, 8Ω, 1% THD

- Supply Voltage Range  $BB_V_{DD} = 1.8V$  to 4.5V,  $D_V_{DD} \& PLL_V_{DD} = 2.7V$  to 4.5V  $LS_V_{DD} \& A_V_{DD} = 2.7V$  to 5.5V

- Shutdown Current 1.1 µA

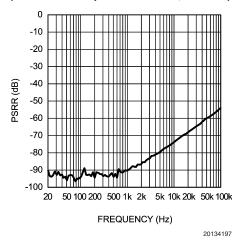

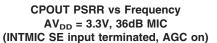

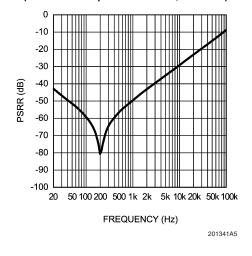

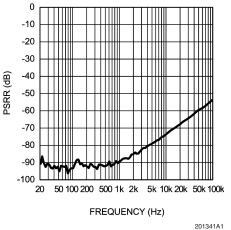

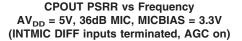

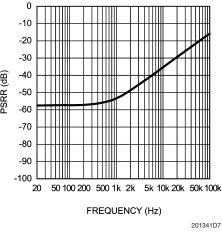

- PSRR @ 217 Hz, A\_V<sub>DD</sub> = 3.3V, (Headphone) 60 dB

- SNR (Stereo DAC to AUXOUT) 88 dB (typ)

- SNR (Mono ADC from Cell Phone In) 90 dB (typ)

- SNR (Aux In to Headphones) 98 dB (typ)

## 4.0 Features

- 18-bit stereo DAC

- 16-bit mono ADC

- 12-bit 4 input multipurpose SAR ADC

- 8 kHz to 48 kHz stereo audio playback

- 8 kHz to 48 kHz mono recording

- 1 Hz to 13.888 kHz sample rate on all 4 SAR channels

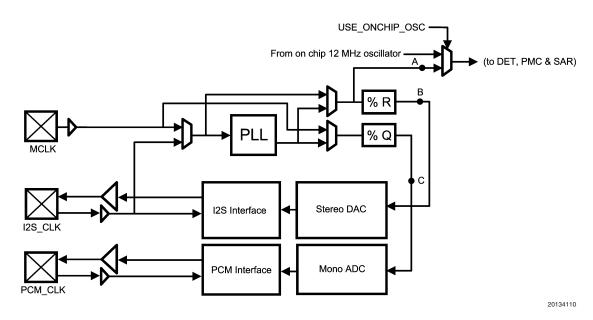

- Bidirectional PCM/I<sup>2</sup>S compatible audio interface Sigma-Delta PLL for operation from any clock at any sample rate

- Low power clock network operation if 12 MHz system clock is available

- Read/write I<sup>2</sup>C or SPI compatible control interface

- 33mW stereo headphone amplifier at 3.3V

- OCL or AC-coupled headphone operation

- Automatic headphone & microphone detection

- Support for internal and external microphones

- Automatic gain control for microphone input

- High efficiency BTL 8Ω amplifier, 600 mW @ 3.3V

- 115 mW earpiece amplifier at 3.3V

- Differential audio I/O for external cellphone module

- Mono differential auxiliary output

- Stereo auxiliary inputs

- Differential microphone input for internal microphone

- Flexible audio routing from input to output

- 32 Step volume control for mixers with 1.5 dB steps

- 16 Step volume control for microphone in 2 dB steps

- Programmable sidetone attenuation in 3 dB steps

- DC Volume Control

- Two configurable GPIO ports

- Programmable voltage triggers on SAR channels

- Multi-function IRQ output

- Micro-power shutdown mode

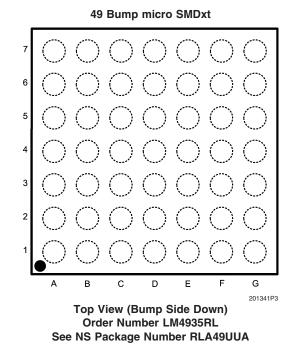

- Available in the 4 x 4 mm 49 bump micro SMDxt package

Boomer® is a registered trademark of National Semiconductor Corporation

LM4935

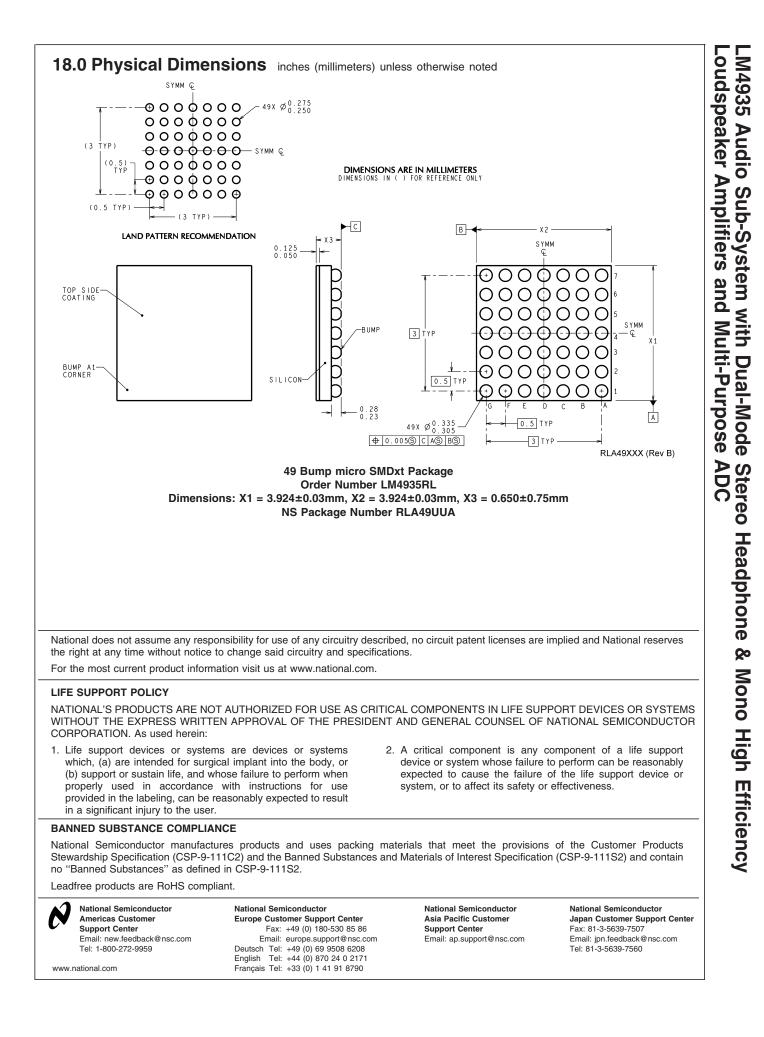

## 5.0 LM4935 Overview

**FIGURE 1. Conceptual Schematic**

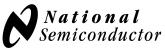

FIGURE 2. Example Application in Multimedia Mobile Phone

| 1.0 General Description                         | 1  |

|-------------------------------------------------|----|

| 2.0 Applications                                | 1  |

| 3.0 Key Specifications                          |    |

| 4.0 Features                                    |    |

| 5.0 LM4935 Overview                             |    |

| 6.0 Typical Application                         |    |

| 7.0 Connection Diagrams                         |    |

| 7.1 PIN TYPE DEFINITIONS                        |    |

| 8.0 Absolute Maximum Ratings                    |    |

| 9.0 Operating Ratings                           |    |

| 10.0 Electrical Characteristics                 |    |

| 11.0 System Control                             |    |

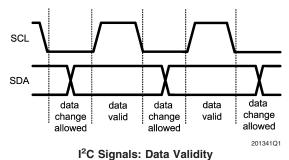

| 11.1 I <sup>2</sup> C SIGNALS                   |    |

| 11.2 I <sup>2</sup> C DATA VALIDITY             | 17 |

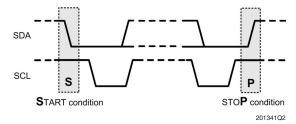

| 11.3 I <sup>2</sup> C START AND STOP CONDITIONS |    |

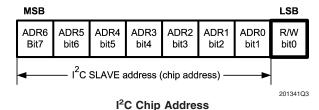

| 11.4 TRANSFERRING DATA                          |    |

| 11.5 I <sup>2</sup> C TIMING PARAMETERS         | 19 |

| 12.0 Status & Control Registers                 | 21 |

| 12.1 BASIC CONFIGURATION REGISTER               |    |

| 12.2 CLOCKS CONFIGURATION REGISTER              |    |

| 12.3 LM4935 CLOCK NETWORK                       |    |

| 12.4 COMMON CLOCK SETTINGS FOR THE DAC & ADC    | 25 |

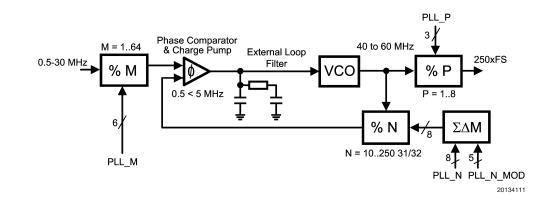

| 12.5 PLL M DIVIDER CONFIGURATION REGISTER       | 26 |

| 12.6 PLL N DIVIDER CONFIGURATION REGISTER       |    |

| 12.7 PLL P DIVIDER CONFIGURATION REGISTER       | 28 |

| 12.8 PLL N MODULUS CONFIGURATION REGISTER       | 29 |

| 12.9 FURTHER NOTES ON PLL PROGRAMMING           |    |

| 12.10 ADC_1 CONFIGURATION REGISTER              |    |

| 12.11 ADC_2 CONFIGURATION REGISTER              |    |

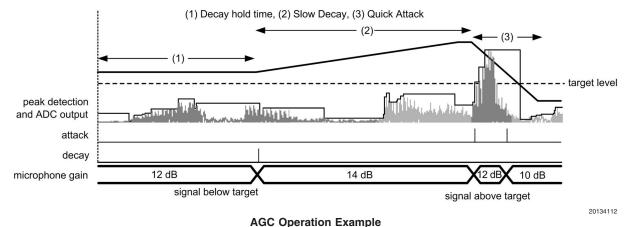

| 12.12 AGC_1 CONFIGURATION REGISTER              |    |

| 12.13 AGC_2 CONFIGURATION REGISTER              | 35 |

| 12.14 AGC_3 CONFIGURATION REGISTER              |    |

| 12.15 AGC OVERVIEW                              |    |

| 12.16 MIC_1 CONFIGURATION REGISTER              |    |

| 12.17 MIC_2 CONFIGURATION REGISTER              |    |

| 12.18 SIDETONE ATTENUATION REGISTER             |    |

| 12.19 CP_INPUT CONFIGURATION REGISTER           | 41 |

| 12.20 AUX_LEFT CONFIGURATION REGISTER           |    |

| 12.21 AUX_RIGHT CONFIGURATION REGISTER          | 43 |

| 12.22 DAC CONFIGURATION REGISTER                |    |

| 12.23 CP_OUTPUT CONFIGURATION REGISTER          |    |

| 12.24 AUX_OUTPUT CONFIGURATION REGISTER         |    |

| 12.25 LS_OUTPUT CONFIGURATION REGISTER          | 47 |

| 12.26 HP_OUTPUT CONFIGURATION REGISTER          |    |

| 12.27 EP_OUTPUT CONFIGURATION REGISTER          |    |

| 12.28 DETECT CONFIGURATION REGISTER             |    |

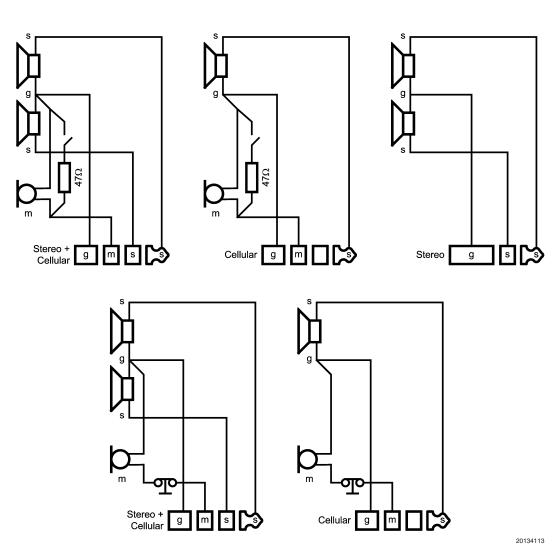

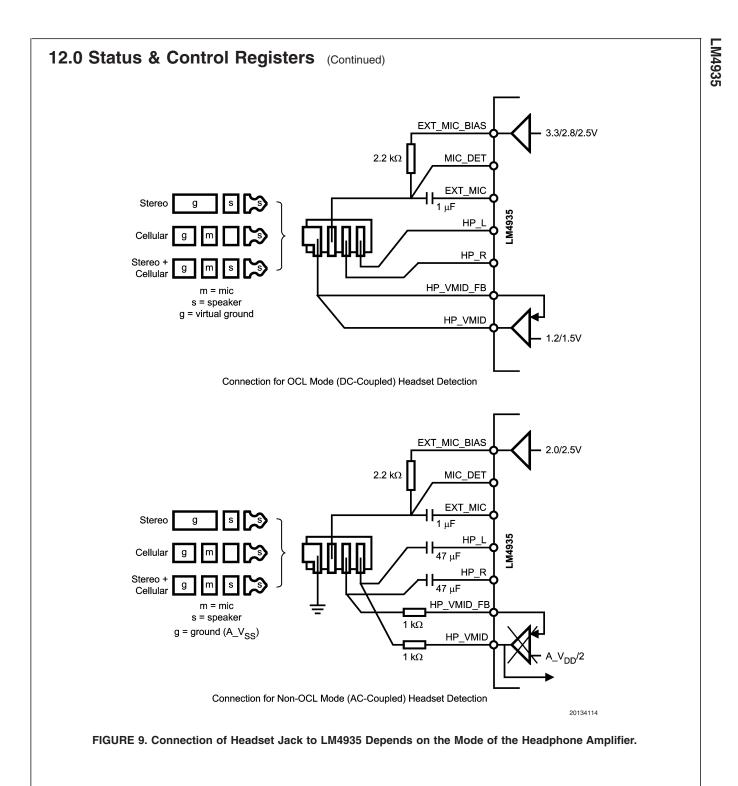

| 12.29 HEADSET DETECT OVERVIEW                   |    |

| 12.30 STATUS REGISTER                           |    |

| 12.31 AUDIO INTERFACE CONFIGURATION REGISTER    |    |

| 12.32 DIGITAL AUDIO DATA FORMATS                | 56 |

| 12.33 GPIO CONFIGURATION REGISTER               |    |

| 12.34 SAR CHANNELS 0 & 1 CONFIGURATION REGISTER |    |

| 12.35 SAR CHANNELS 2 & 3 CONFIGURATION REGISTER |    |

| 12.36 SAR DATA 0 TO 3 REGISTERS                 |    |

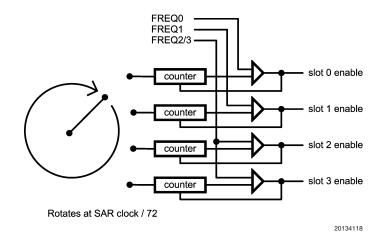

| 12.37 SAR OVERVIEW                              |    |

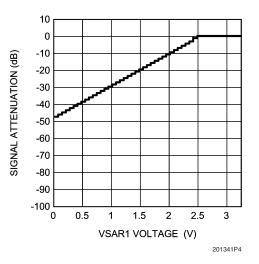

| 12.38 DC VOLUME CONFIGURATION REGISTER          |    |

| 12.39 SAR TRIGGER 1 CONFIGURATION REGISTER      |    |

| 12.40 SAR TRIGGER 1 MSBs CONFIGURATION REGISTER |    |

| 12.41 SAR TRIGGER 2 CONFIGURATION REGISTER      |    |

| 12.42 SAR TRIGGER 2 MSBs CONFIGURATION REGISTER |    |

| 12.43 DEBUG REGISTER                            |    |

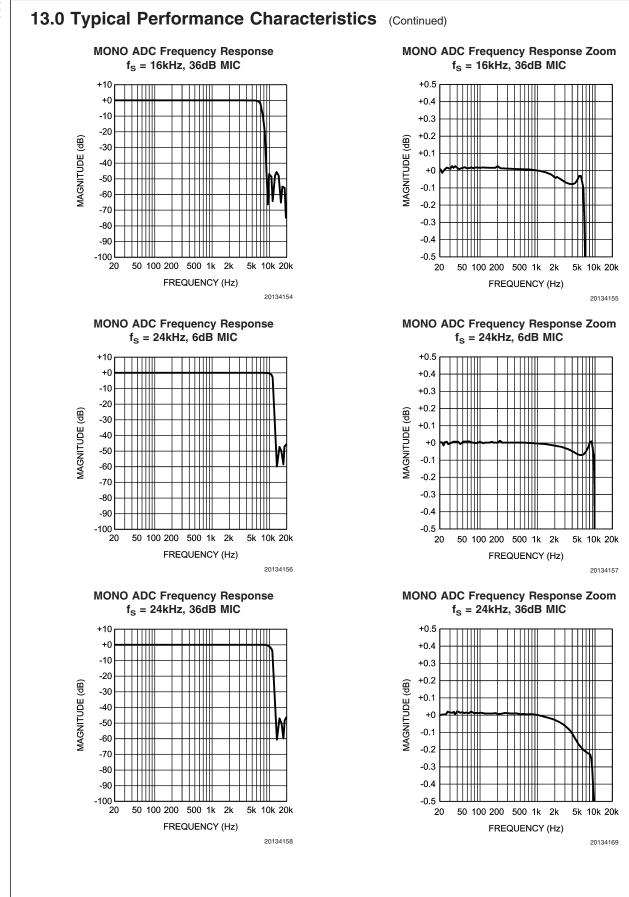

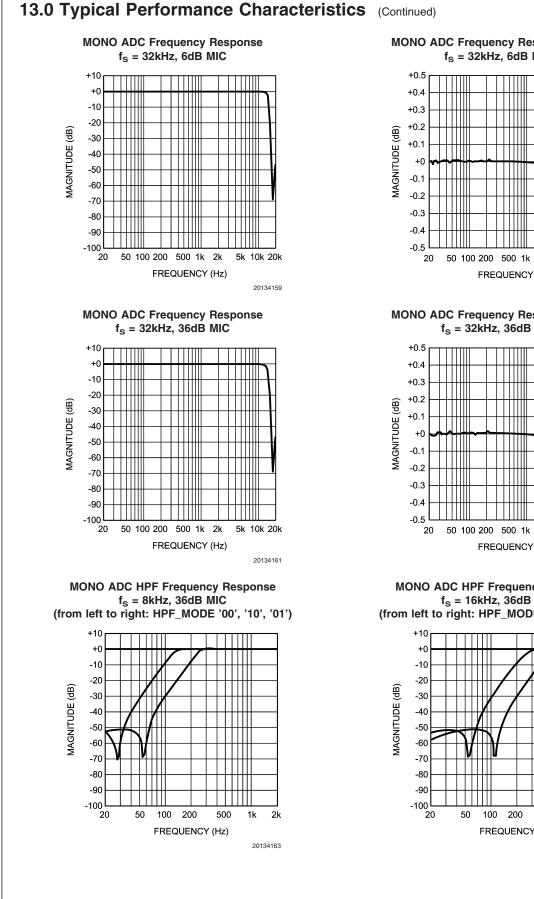

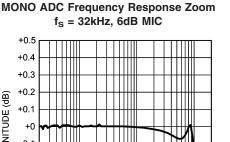

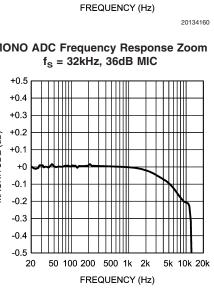

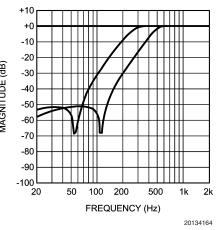

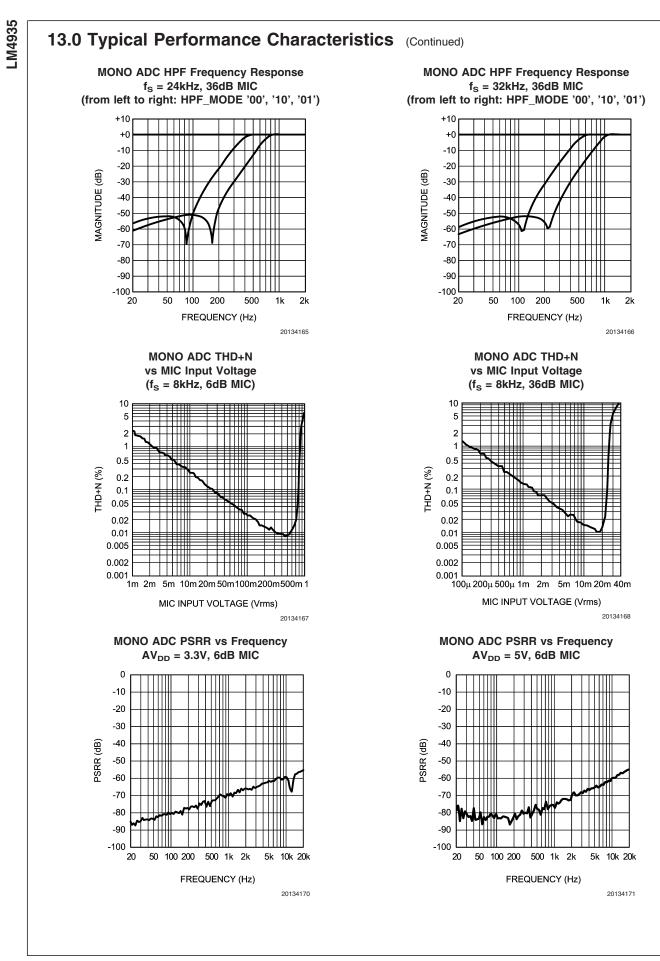

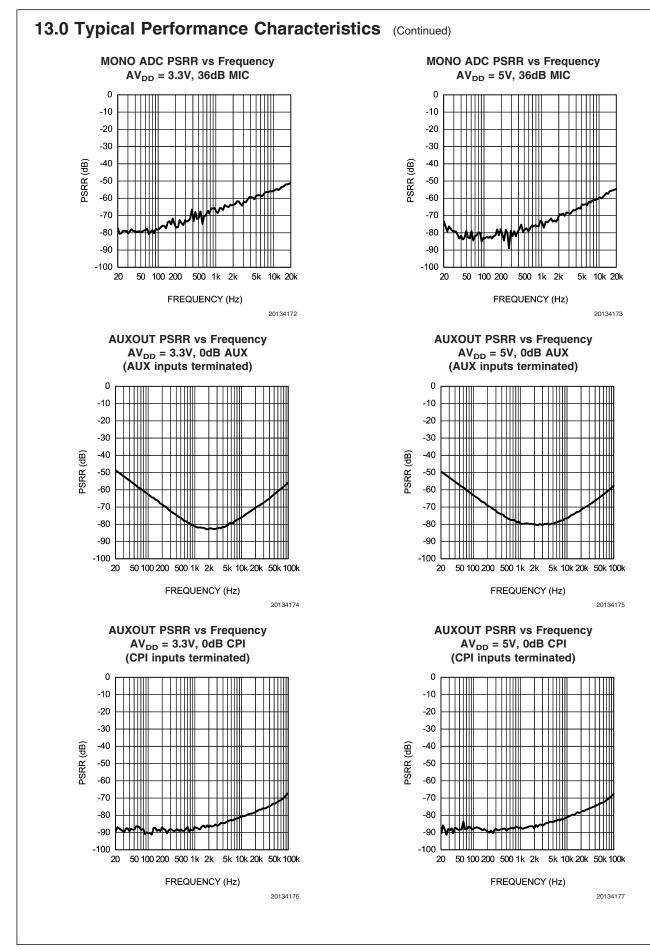

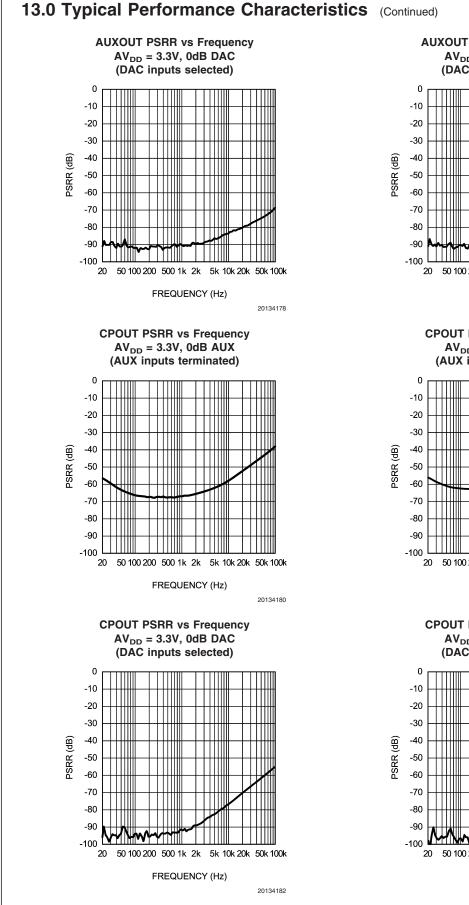

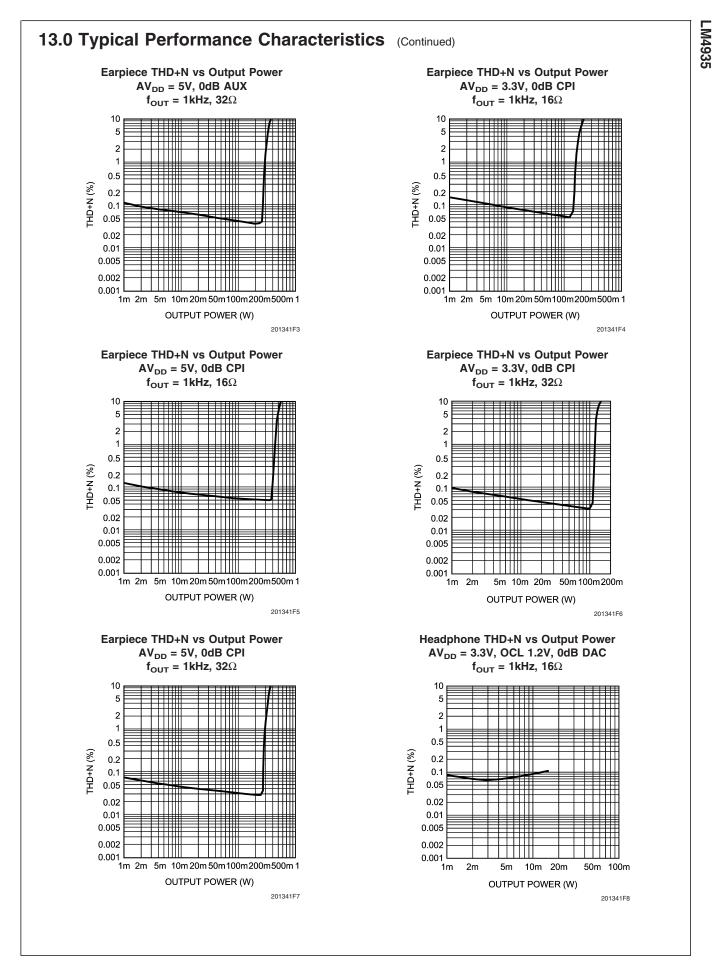

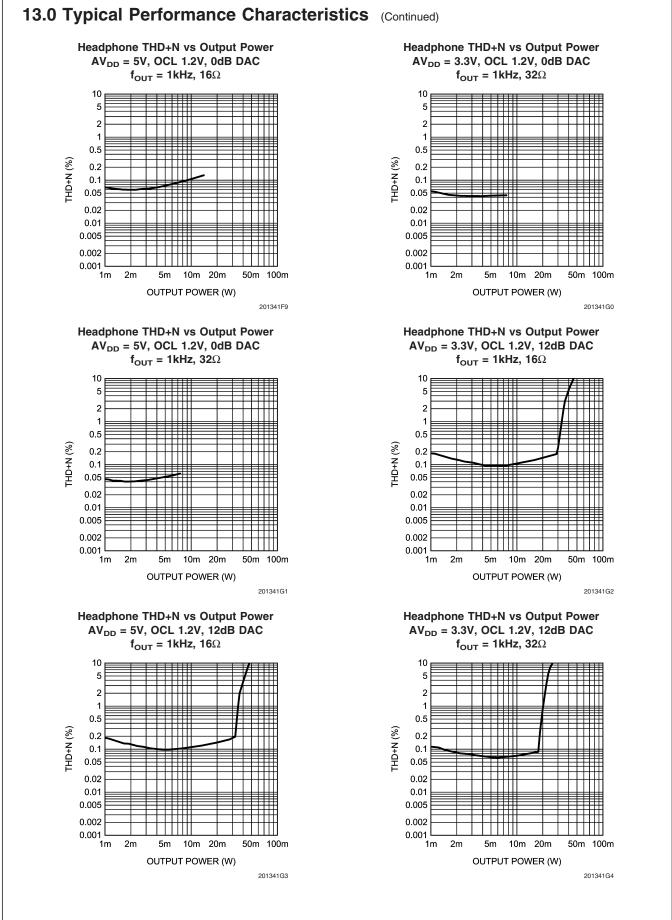

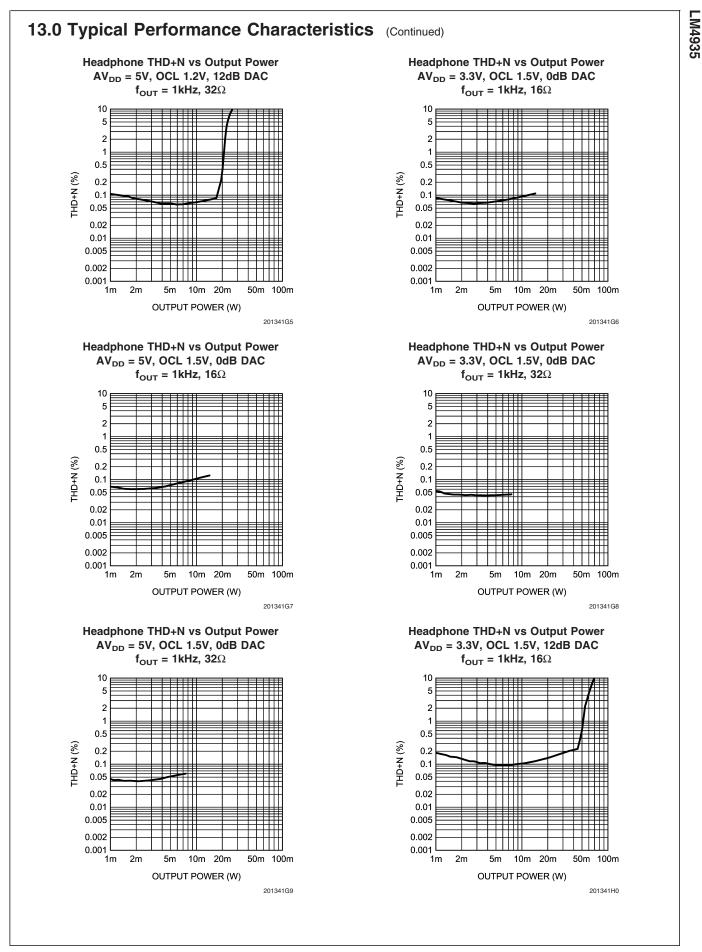

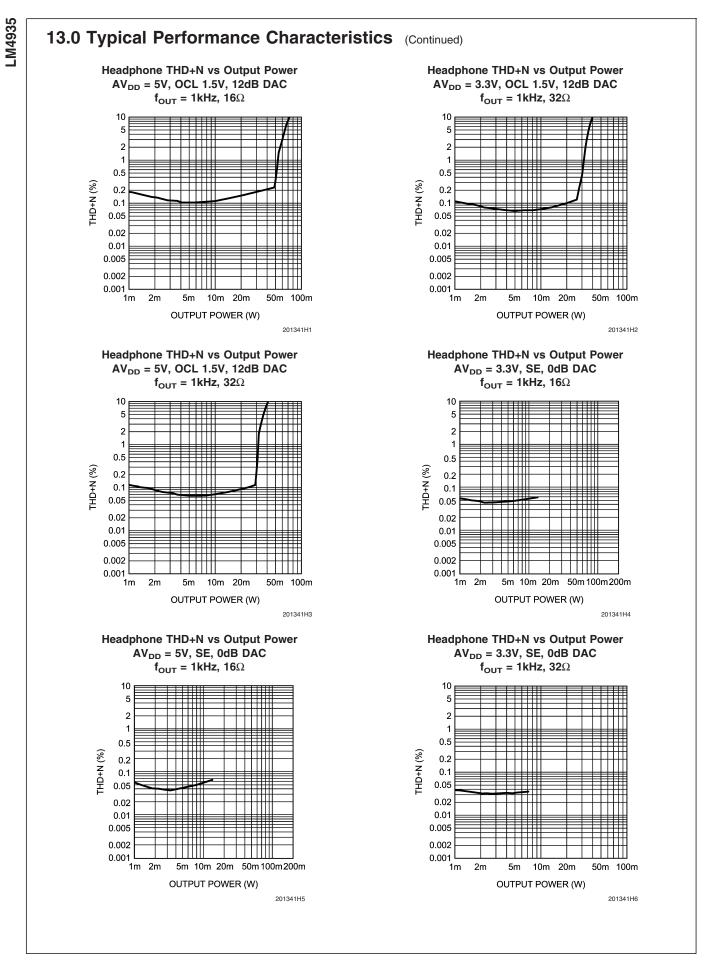

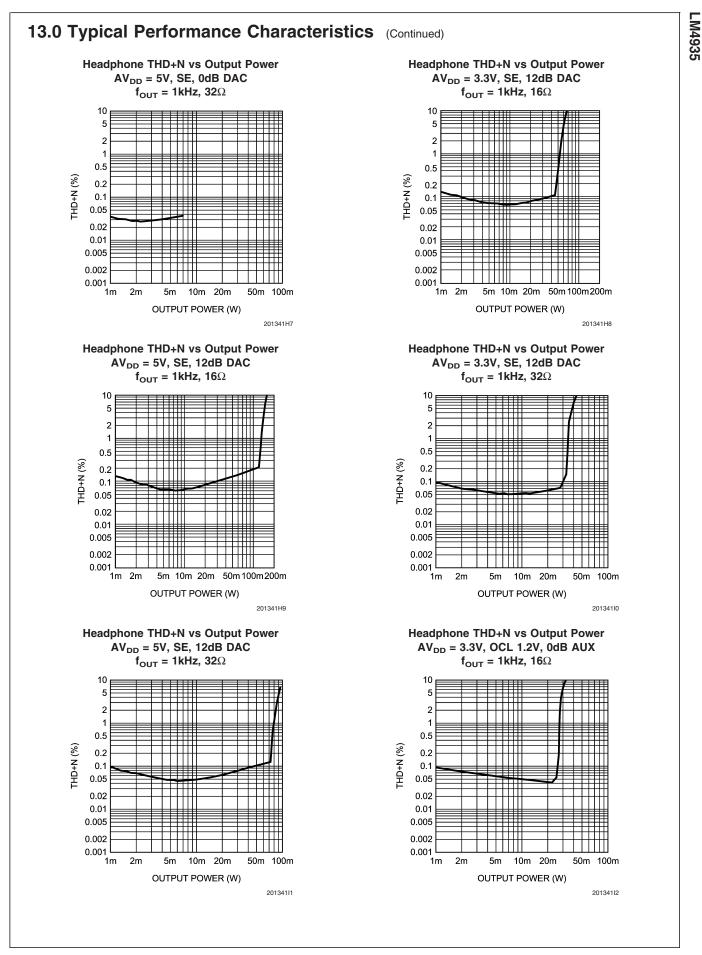

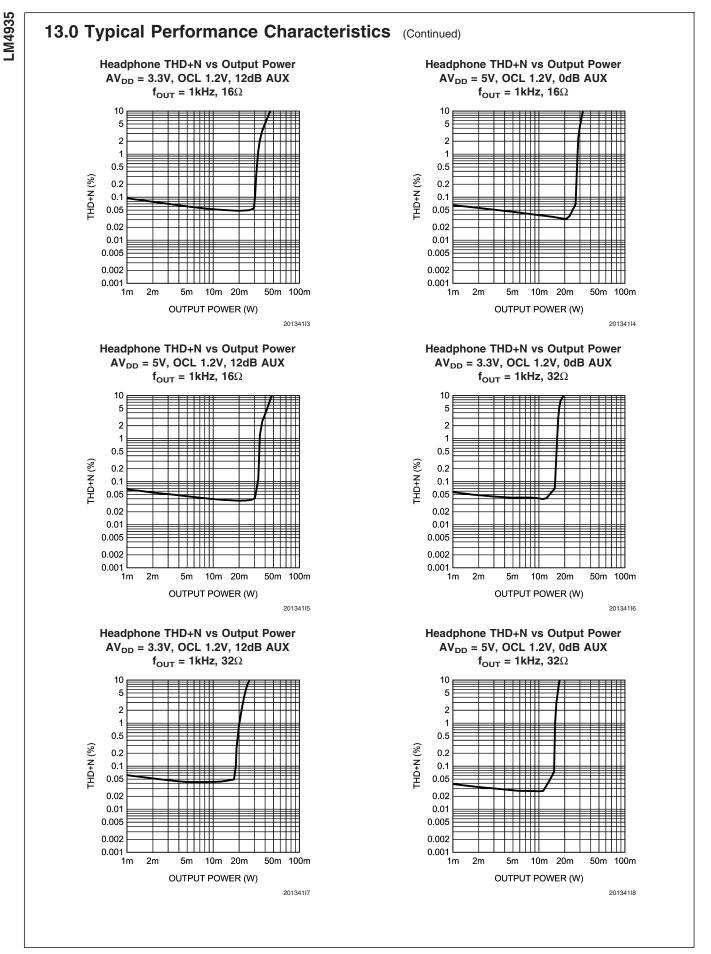

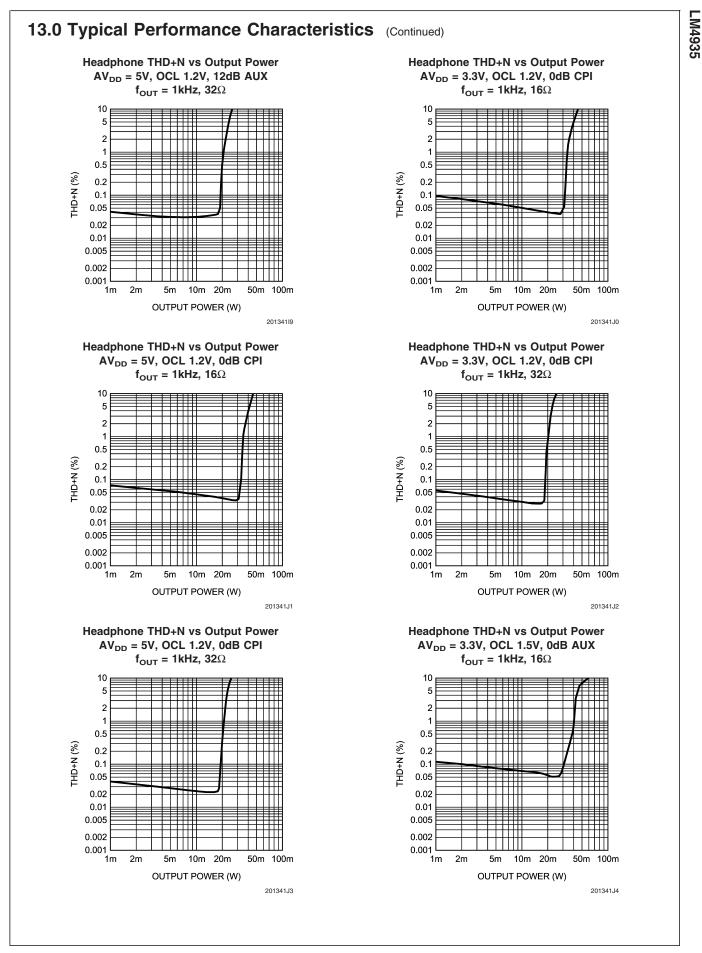

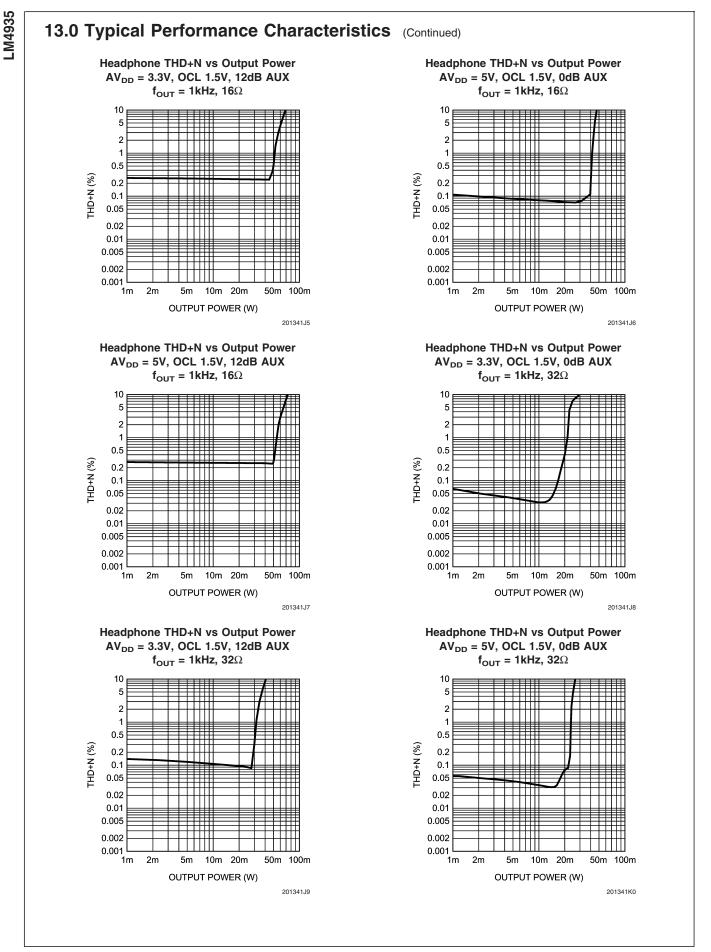

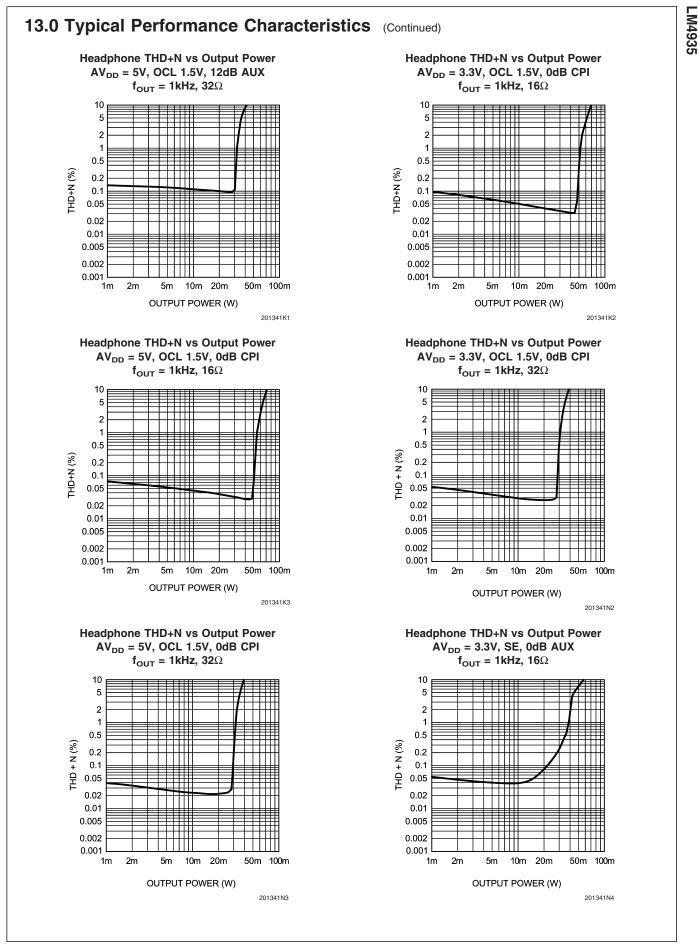

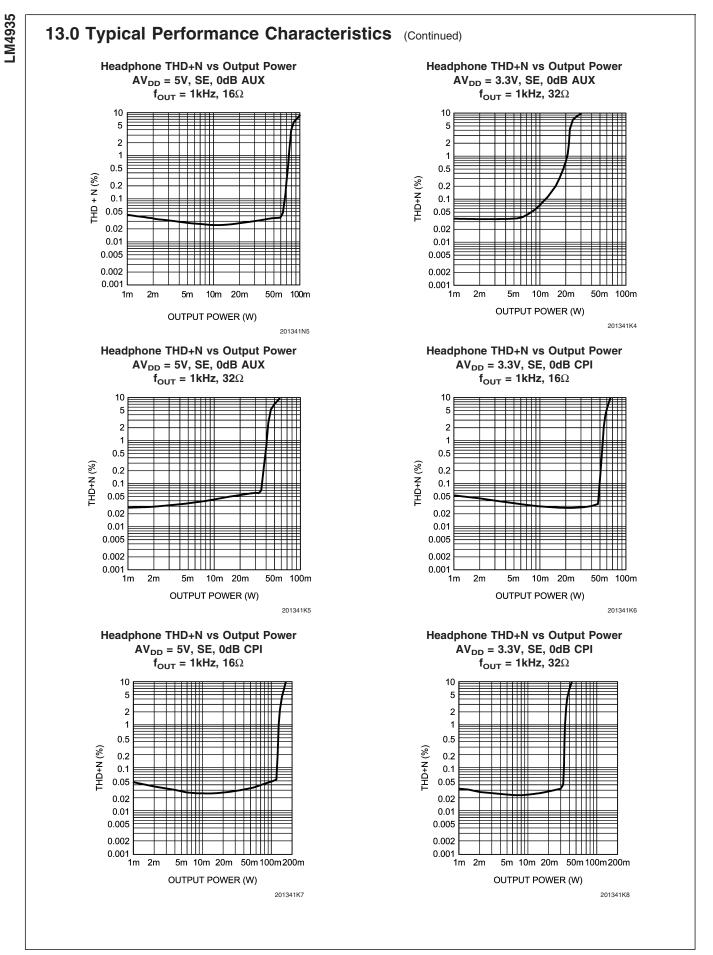

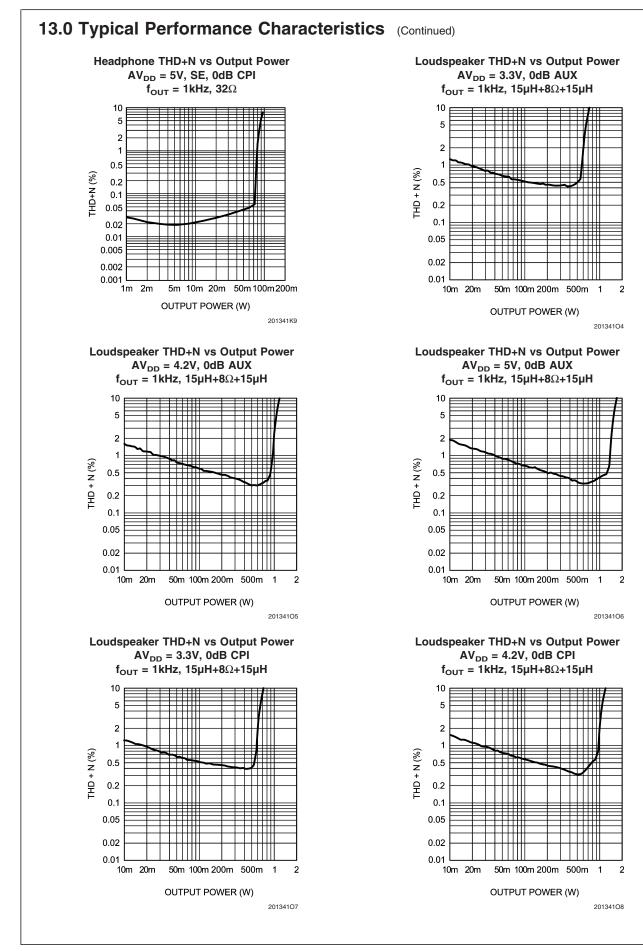

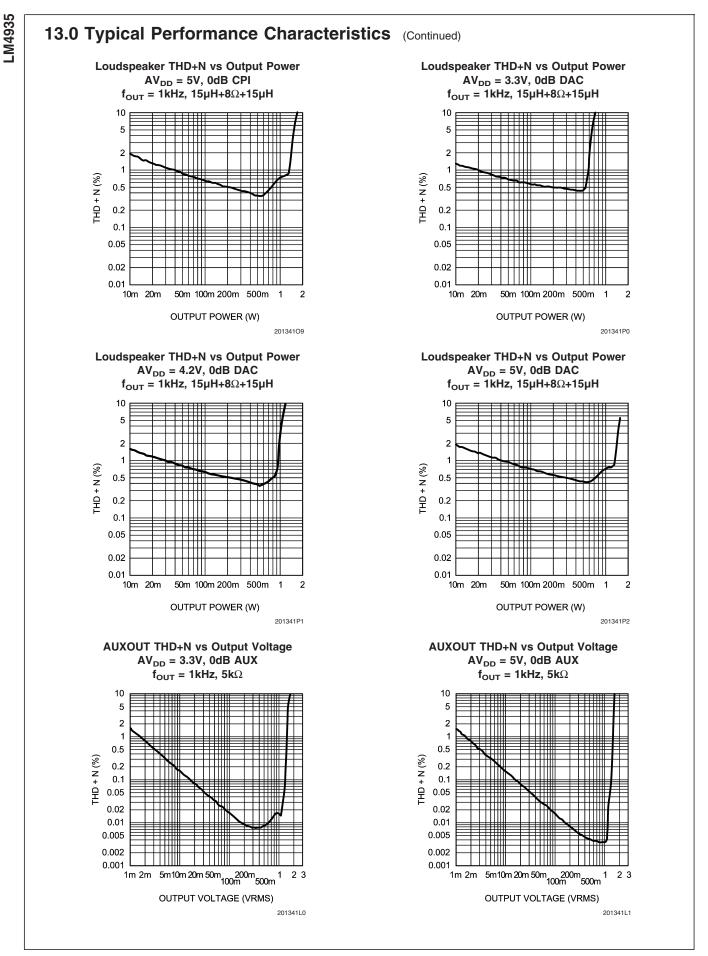

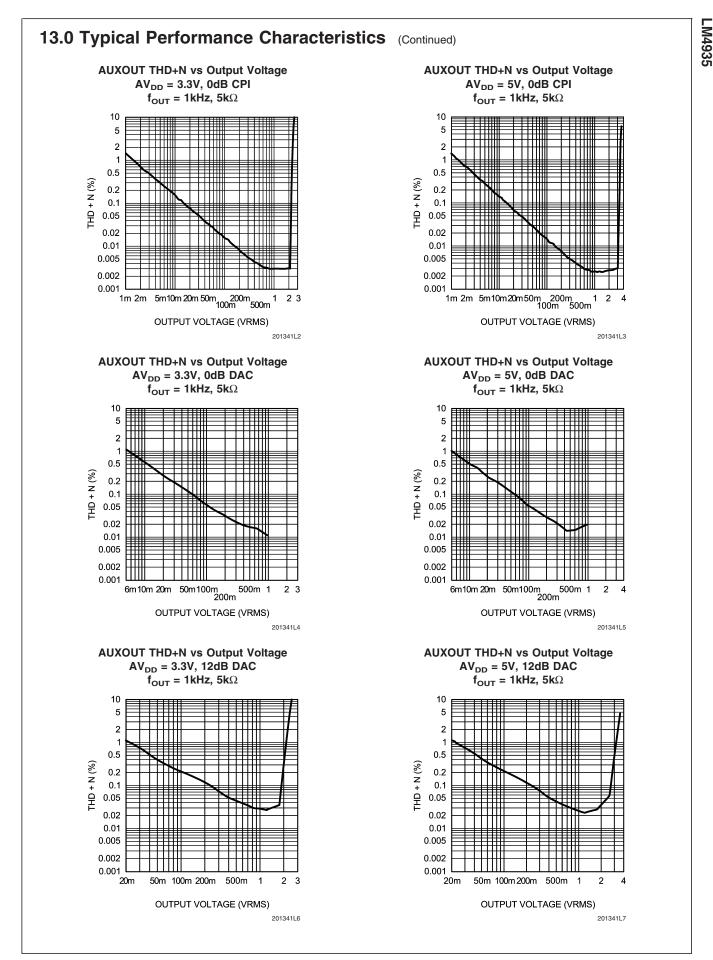

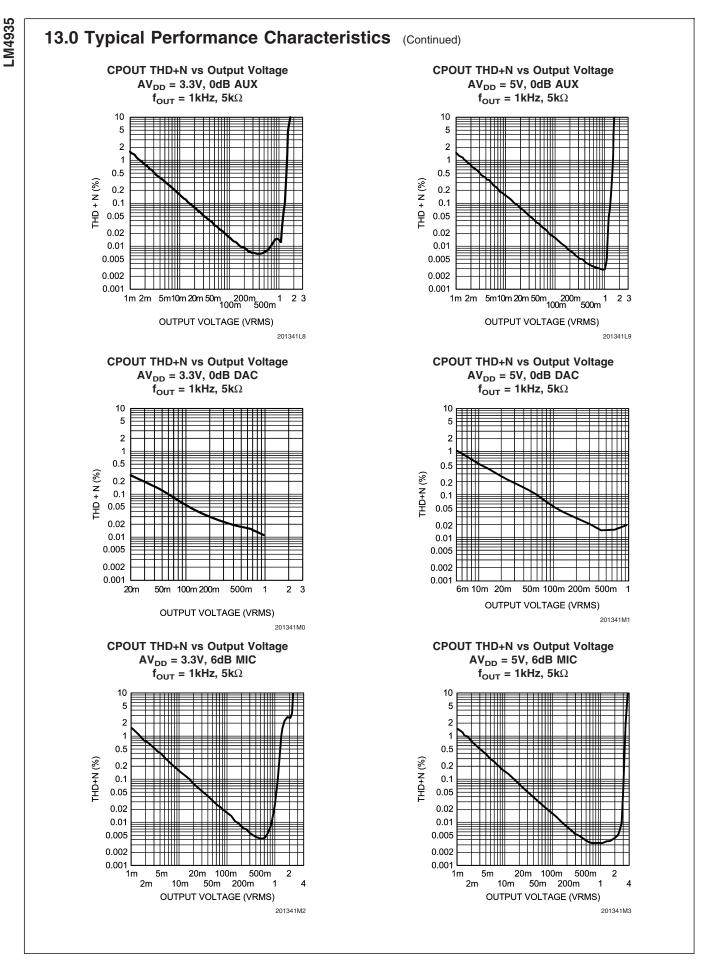

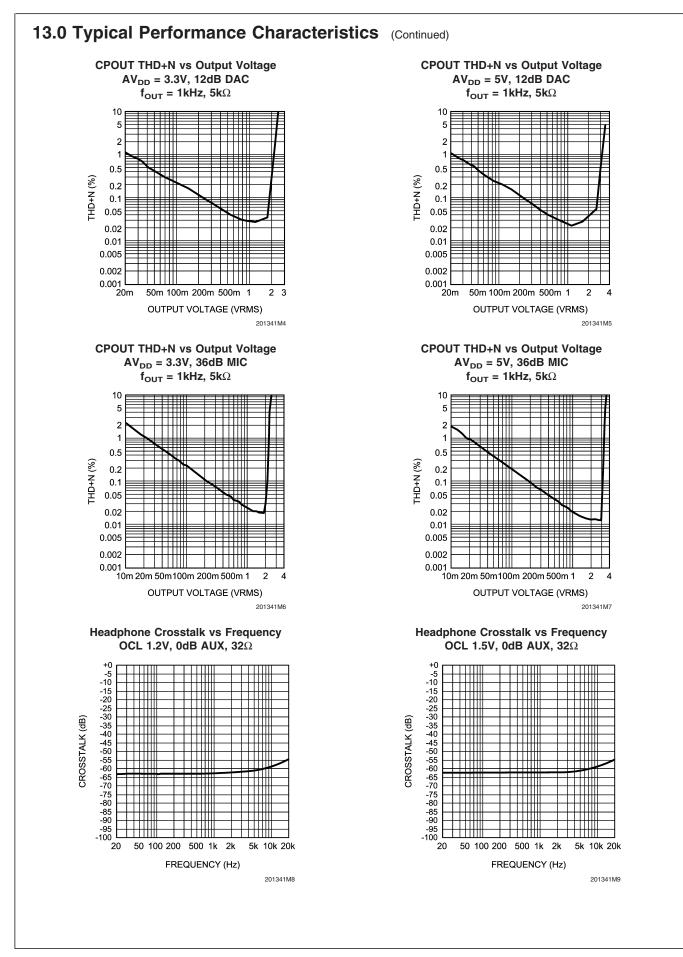

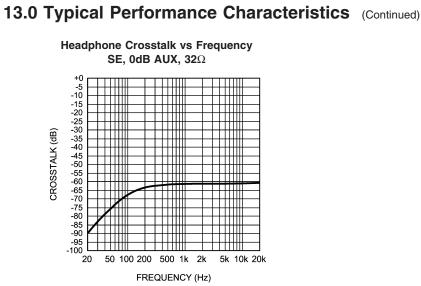

| 13.0 Typical Performance Characteristics        | 69 |

# LM4935

# Table of Contents (Continued)

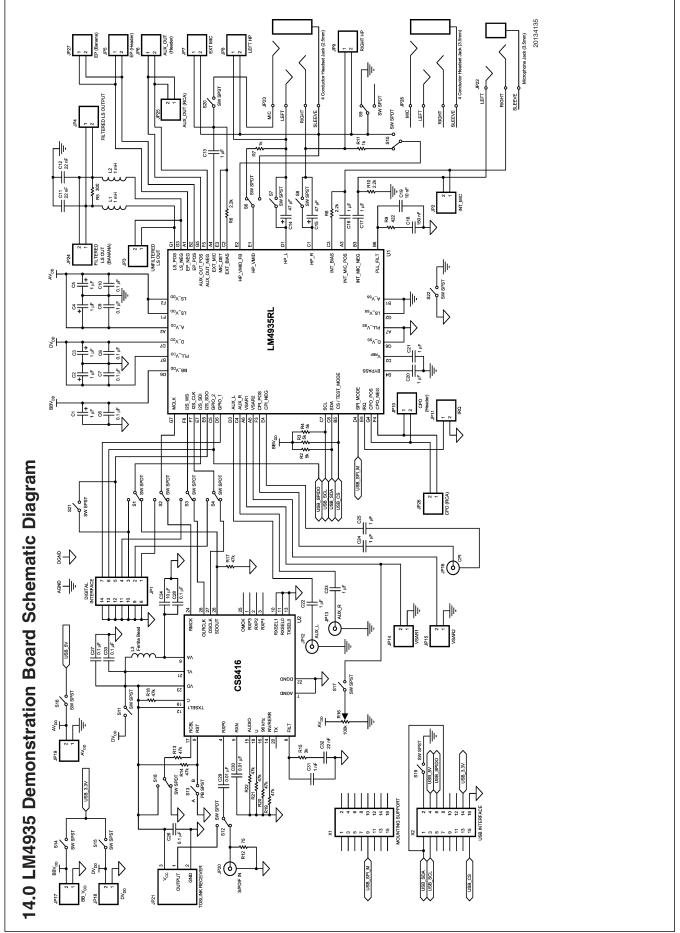

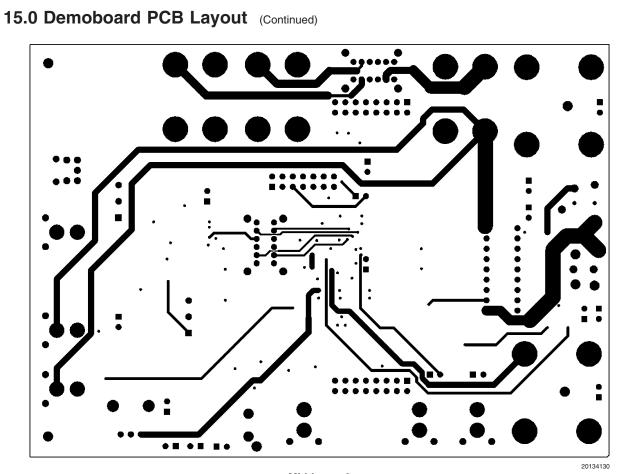

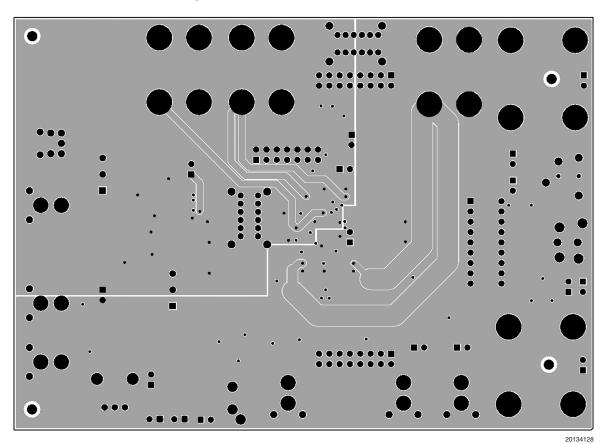

| 14.0 LM4935 Demonstration Board Schematic Diagram | 105 |

|---------------------------------------------------|-----|

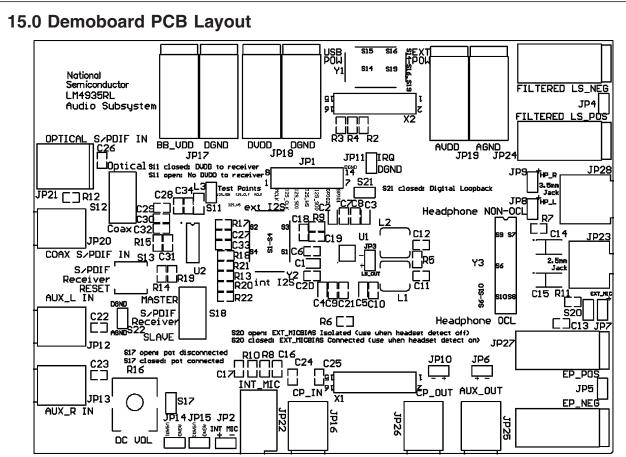

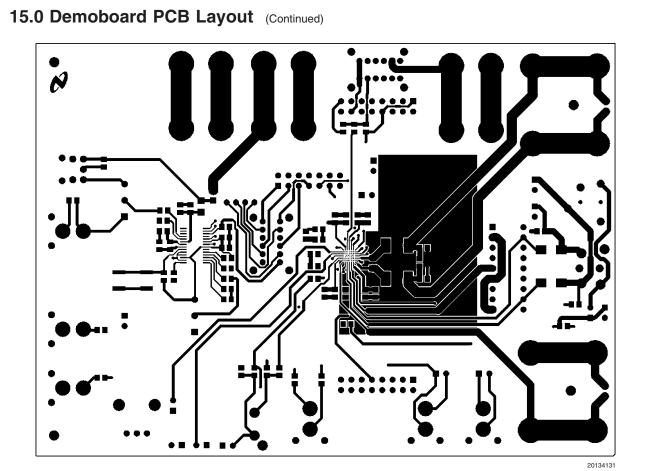

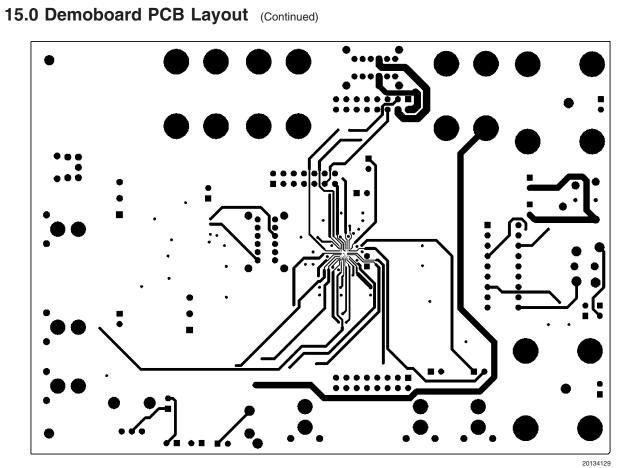

| 15.0 Demoboard PCB Layout                         | 106 |

| 16.0 Product Status Definitions                   | 111 |

| 17.0 Revision History                             | 112 |

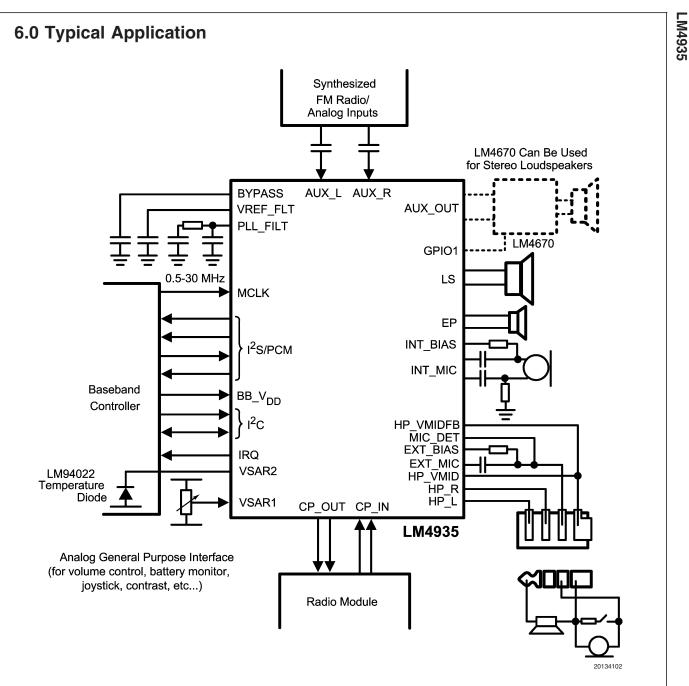

| 18.0 Physical Dimensions                          | 113 |

# 7.0 Connection Diagrams

49 Bump micro SMDxt Marking XYTT GG7 Pin A1 20134107 Top View XY — Date Code TT — Die Traceability G — Boomer G7 — LM4935RL

# 7.0 Connection Diagrams (Continued)

# **Pin Descriptions**

| Pin    | Pin Name            | Туре    | Direction | Description                                                                                                                                                  |

|--------|---------------------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | EP_NEG              | Analog  | Output    | Earpiece negative output                                                                                                                                     |

| A2     | A_V <sub>DD</sub>   | Supply  | Input     | Headphone and mixer V <sub>DD</sub>                                                                                                                          |

| A3     | INT_MIC_POS         | Analog  | Input     | Internal microphone positive input                                                                                                                           |

| A4     | EXT_MIC             | Analog  | Input     | External microphone input                                                                                                                                    |

| A5     | VSAR2               | Analog  | Input     | Input to SAR channel 2                                                                                                                                       |

| A6     | VSAR1               | Analog  | Input     | Input to SAR channel 1                                                                                                                                       |

| A7     | PLL_V <sub>SS</sub> | Supply  | Input     | PLL V <sub>SS</sub>                                                                                                                                          |

| B1     | A_V <sub>SS</sub>   | Supply  | Input     | Headphone and mixer V <sub>SS</sub>                                                                                                                          |

| B2     | EP_POS              | Analog  | Output    | Earpiece positive output                                                                                                                                     |

| B3     | INT_MIC_NEG         | Analog  | Input     | Internal microphone negative input                                                                                                                           |

| B4     | BYPASS              | Analog  | Inout     | A_V <sub>DD</sub> /2 filter point                                                                                                                            |

| B5     | TEST_MODE/CS        | Digital | Input     | If SPI_MODE = 1, then this pin becomes $\overline{CS}$ . If SPI_MODE = 0,<br>and TEST_MODE/ $\overline{CS}$ = 1, then this places the LM4935 into test mode. |

| B6     | PLL_FILT            | Analog  | Inout     | Filter point for PLL VCO input                                                                                                                               |

| B7     | PLL_V <sub>DD</sub> | Supply  | Input     | PLL $V_{DD}$                                                                                                                                                 |

| C1     | HP_R                | Analog  | Output    | Headphone Right Output                                                                                                                                       |

| C2     | EXT_BIAS            | Analog  | Output    | External microphone supply (2.0/2.5/2.8/3.3V)                                                                                                                |

| C3     | INT_BIAS            | Analog  | Output    | 2.0V/2.5V ultra-clean supply for internal microphone                                                                                                         |

| C4     | AUX_R               | Analog  | Input     | Right Analog Input                                                                                                                                           |

| C5     | GPIO_2              | Digital | Inout     | General Purpose I/O 2                                                                                                                                        |

| C6     | SDA                 | Digital | Inout     | Control Data, I2C_SDA or SPI_SDI                                                                                                                             |

| C7     | SCL                 | Digital | Input     | Control Clock, I2C_SCL or SPI_SCK                                                                                                                            |

| D1     | HP_L                | Analog  | Output    | Headphone Left Output                                                                                                                                        |

| D2     | VREF_FLT            | Analog  | Inout     | Filter point for the microphone power supply                                                                                                                 |

| D3     | AUX_L               | Analog  | Input     | Left Analog Input                                                                                                                                            |

| D4     | SPI_MODE            | Digital | Input     | Control mode select 1 = SPI, 0 = I2C (or test)                                                                                                               |

| <br>D5 | GPIO_1              | Digital | Inout     | General Purpose I/O 1                                                                                                                                        |

| D6     | BB_V <sub>DD</sub>  | Supply  | Input     | Baseband $V_{DD}$ for the digital I/Os                                                                                                                       |

| D7     | D_V <sub>DD</sub>   | Supply  | Input     | Digital $V_{DD}$                                                                                                                                             |

| E1     | HP_VMID             | Analog  | Inout     | Virtual Ground for Headphones in OCL mode, otherwise 1st headset detection input                                                                             |

| E2     | HP_VMID_FB          | Analog  | Inout     | VMID Feedback in OCL mode, otherwise a 2nd headset detection input                                                                                           |

| E3     | MIC_DET             | Analog  | Input     | Headset insertion/removal and Microphone presence detection input                                                                                            |

| <br>E4 | CPI_NEG             | Analog  | Input     | Cell Phone analog input negative                                                                                                                             |

| E5     | IRQ                 | Digital | Output    | Interrupt request signal (NOT open drain)                                                                                                                    |

| E6     | I2S_SDO             | Digital | Output    | I2S Serial Data Out                                                                                                                                          |

| <br>E7 | 12S_SDI             | Digital | Input     | I2S Serial Data Input                                                                                                                                        |

| <br>F1 | LS_V <sub>DD</sub>  | Supply  | Input     | Loudspeaker V <sub>DD</sub>                                                                                                                                  |

| F2     | LS_V <sub>DD</sub>  | Supply  | Input     | Loudspeaker V <sub>DD</sub>                                                                                                                                  |

| F3     | CPI_POS             | Analog  | Input     | Cell Phone analog input positive                                                                                                                             |

|        | CPO_NEG             | Analog  | Output    | Cell Phone analog output negative                                                                                                                            |

| F5     | AUX_OUT_NEG         | Analog  | Output    | Auxiliary analog output negative                                                                                                                             |

| <br>F6 | 12S_WS              | Digital | Inout     | I2S Word Select Signal (can be master or slave)                                                                                                              |

| F7     | I2S_CLK             | Digital | Inout     | I2S Clock Signal (can be master or slave)                                                                                                                    |

| G1     | LS_POS              | Analog  | Output    | Loudspeaker positive output                                                                                                                                  |

| G2     | LS_V <sub>ss</sub>  | Supply  | Input     | Loudspeaker V <sub>SS</sub>                                                                                                                                  |

| G3     | LS_NEG              | Analog  | Output    | Loudspeaker negative output                                                                                                                                  |

| G4     | CPO_POS             | Analog  | Output    | Cell Phone analog output positive                                                                                                                            |

| G5     | AUX_OUT_POS         | Analog  | Output    | Auxiliary analog output positive                                                                                                                             |

| 40     |                     | . maiog | Carpar    |                                                                                                                                                              |

## 7.0 Connection Diagrams (Continued)

## Pin Descriptions (Continued)

| Pin | Pin Name   | Туре    | Direction | Description                        |

|-----|------------|---------|-----------|------------------------------------|

| G6  | $D_V_{SS}$ | Supply  | Input     | Digital V <sub>SS</sub>            |

| G7  | MCLK       | Digital | Input     | Input clock from 0.5 MHz to 30 MHz |

#### 7.1 PIN TYPE DEFINITIONS never driven. Digital Output-A pin that is driven by the device and Analog Input— A pin that is used by the analog and is never driven by the device. Supplies are should not be driven by another device to part of this classification. avoid contention. Analog Output— A pin that is driven by the device and Digital Inout— A pin that is either open drain (I2C\_SDA) or a bidirectional CMOS in/out. In the should not be driven by external sources. later case the direction is selected by a Analog Inout— A pin that is typically used for filtering a control register within the LM4935. DC signal within the device, Passive components can be connected to these pins.

Digital Input— A pin that is used by the digital but is

## 8.0 Absolute Maximum Ratings

#### (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Analog Supply Voltage<br>(A_V <sub>DD</sub> & LS_V <sub>DD</sub> )<br>Digital Supply Voltage | 6.0V               |

|----------------------------------------------------------------------------------------------|--------------------|

| $(BB_V_{DD} \& D_V_{DD} \& PLL_V_{DD})$                                                      | 6.0V               |

| Storage Temperature                                                                          | –65°C to +150°C    |

| Power Dissipation (Note 3)                                                                   | Internally Limited |

| ESD Susceptibility                                                                           |                    |

| Human Body Model (Note 4)                                                                    | 2500V              |

| Machine Model (Note 5)                                                                       | 200V               |

Junction Temperature $150^{\circ}C$ Thermal Resistance $\theta_{JA} - RLA49$  (soldered downto PCB with 2in<sup>2</sup> 1oz. copperplane) $60^{\circ}C/W$ Soldering Information

## 9.0 Operating Ratings

| -40°C to +85°C |

|----------------|

|                |

| 2.7V to 4.5V   |

| 1.8V to 4.5V   |

| 2.7V to 5.5V   |

|                |

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated  $PLL_V_{DD} = 3.3V$ ,  $D_V_{DD} = 3.3V$ ,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C.

|                    |                          |                                                                           | LM49                |                   |             |

|--------------------|--------------------------|---------------------------------------------------------------------------|---------------------|-------------------|-------------|

| Symbol             | Parameter                | Conditions                                                                | Typical<br>(Note 6) | Limit<br>(Note 7) | Units       |

| DC CURREN          | T CONSUMPTION            |                                                                           | , ,                 | , ,               |             |

|                    |                          | Chip Mode '00', f <sub>MCLK</sub> = 13MHz                                 | 0.7                 |                   | μA          |

| DI <sub>SD</sub>   | Digital Shutdown Current | Chip Mode '00', f <sub>MCLK</sub> = 19.2MHz                               | 0.7                 | 5                 | μA<br>(max) |

|                    |                          | Chip Mode '01', f <sub>MCLK</sub> = 13MHz                                 | 1.5                 |                   | mA          |

| DI <sub>ST</sub>   | Digital Standby Current  | Chip Mode '01', f <sub>MCLK</sub> = 19.2MHz                               | 2.2                 | 3                 | mA<br>(max) |

|                    |                          | Chip Mode '10', f <sub>MCLK</sub> = 13MHz,<br>DAC, ADC, SAR OFF           | 1.5                 |                   | mA          |

| DI .               | Digital Active Current   | Chip Mode '10', f <sub>MCLK</sub> = 19.2MHz,<br>DAC, ADC, SAR OFF         | 2.2                 |                   | mA          |

| DI <sub>DD</sub>   |                          | Chip Mode '10', f <sub>MCLK</sub> = 13MHz<br>DAC, ADC, SAR ON             | 11.2                |                   | mA          |

|                    |                          | Chip Mode '10', f <sub>MCLK</sub> = 19.2MHz,<br>DAC, ADC, SAR ON          | 16.2                | 20                | mA<br>(max) |

| Al <sub>SD</sub>   | Analog Shutdown Current  | Chip Mode '00'                                                            | 0.2                 | 3                 | μA<br>(max) |

| Al <sub>st</sub>   | Analog Standby Current   | Chip Mode '01',<br>No headset inserted                                    | 0.2                 | 3                 | μA<br>(max) |

|                    |                          | All Outputs OFF, SE MODE                                                  | 6.1                 |                   | mA          |

|                    |                          | All Outputs OFF, OCL MODE                                                 | 5.7                 |                   | mA          |

| Al <sub>DD</sub>   | Analog Active Current    | All Outputs ON, SE MODE                                                   | 18.3                |                   | mA          |

|                    |                          | All Outputs ON, OCL MODE                                                  | 18.7                | 28                | mA<br>(max) |

|                    | PLL Active Current       | f <sub>MCLK</sub> = 13 MHz<br>f <sub>PLLOUT</sub> = 12 MHz, PLL ON only   | 4.2                 |                   | mA          |

| PLLI <sub>DD</sub> |                          | f <sub>MCLK</sub> = 19.2 MHz<br>f <sub>PLLOUT</sub> = 12 MHz, PLL ON only | 6.2                 |                   | mA          |

| ADCI <sub>DD</sub> | ADC Active Current       | f <sub>MCLK</sub> = 13MHz, ADC ON only                                    | 2.5                 |                   | mA          |

|                    |                          | f <sub>MCLK</sub> = 19.2MHz, ADC ON only                                  | 3.6                 |                   | mA          |

LM4935

LM4935

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated PLL\_V<sub>DD</sub> = 3.3V,  $D_V_{DD}$  = 3.3V, BB\_V<sub>DD</sub> = 1.8V, A\_V<sub>DD</sub> = 3.3V, LS\_V<sub>DD</sub> = 3.3V. The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|                      |                                 |                                                   | LM49                | )35               |        |

|----------------------|---------------------------------|---------------------------------------------------|---------------------|-------------------|--------|

| Symbol               | Parameter                       | Conditions                                        | Typical<br>(Note 6) | Limit<br>(Note 7) | Units  |

| DC CURREN            | IT CONSUMPTION                  |                                                   |                     |                   |        |

|                      |                                 | f <sub>MCLK</sub> = 13MHz, DAC ON only;           | 7.4                 |                   | mA     |

| DACIDD               | DAC Active Current              | PLL OFF, f <sub>S</sub> = 48kHz                   | 7.4                 |                   |        |

| DAOIDD               |                                 | $f_{MCLK}$ = 19.2MHz, DAC ON only                 | 10.7                |                   | mA     |

|                      |                                 | PLL OFF; f <sub>S</sub> = 48kHz                   | 10.7                |                   |        |

| SARIDD               | SAR Active Current              | f <sub>MCLK</sub> = 13MHz, SAR ON only            | 1.6                 |                   | mA     |

| 0,                   |                                 | f <sub>MCLK</sub> = 19.2MHz, SAR ON only          | 2.3                 |                   | mA     |

| LSI <sub>DD</sub>    | Loudspeaker Quiescent Current   | LS ON only                                        | 8.8                 |                   | mA     |

| HPIDD                | Headphone Quiescent Current     | HP ON only, SE MODE                               | 3.5                 |                   | mA     |

|                      |                                 | HP ON only, OCL MODE                              | 3.9                 |                   | mA     |

| EPI <sub>DD</sub>    | Earpiece Quiescent Current      | EP ON only                                        | 4.4                 |                   | mA     |

| AUXI <sub>DD</sub>   | AUXOUT Quiescent Current        | AUXOUT ON only                                    | 4.8                 |                   | mA     |

| CPOUTI <sub>DD</sub> | CPOUT Quiescent Current         | CPOUT ON only                                     | 4.8                 |                   | mA     |

| LOUDSPEAK            | KER AMPLIFIER                   |                                                   |                     |                   |        |

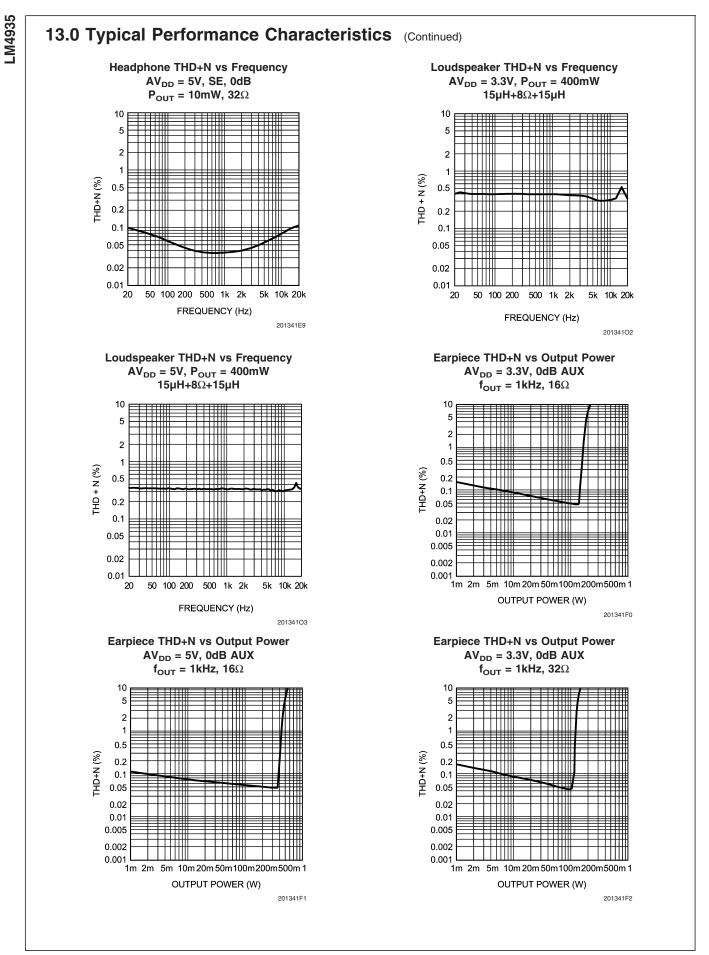

| P <sub>LS</sub>      | Max Loudspeaker Power           | $8\Omega$ load, LS_V <sub>DD</sub> = 5V           | 1.3                 |                   | W      |

|                      |                                 | $8\Omega$ load, LS_V <sub>DD</sub> = 4.2V         | 0.9                 |                   | W      |

|                      |                                 | $8\Omega$ load, LS_V <sub>DD</sub> = 3.3V         | 0.6                 | 0.44              | W (min |

| LS <sub>THD+N</sub>  | Loudspeaker Harmonic Distortion | $8\Omega$ load, LS_V <sub>DD</sub> = 3.3V,        | 0.4                 |                   | 0/     |

|                      |                                 | $P_{O} = 400 \text{mW}$                           | 0.4                 |                   | %      |

| LS <sub>EFF</sub>    | Efficiency                      | 0 dB Input                                        | 84                  |                   | %      |

|                      |                                 | MCLK = 12.000 MHz                                 | 04                  |                   | /0     |

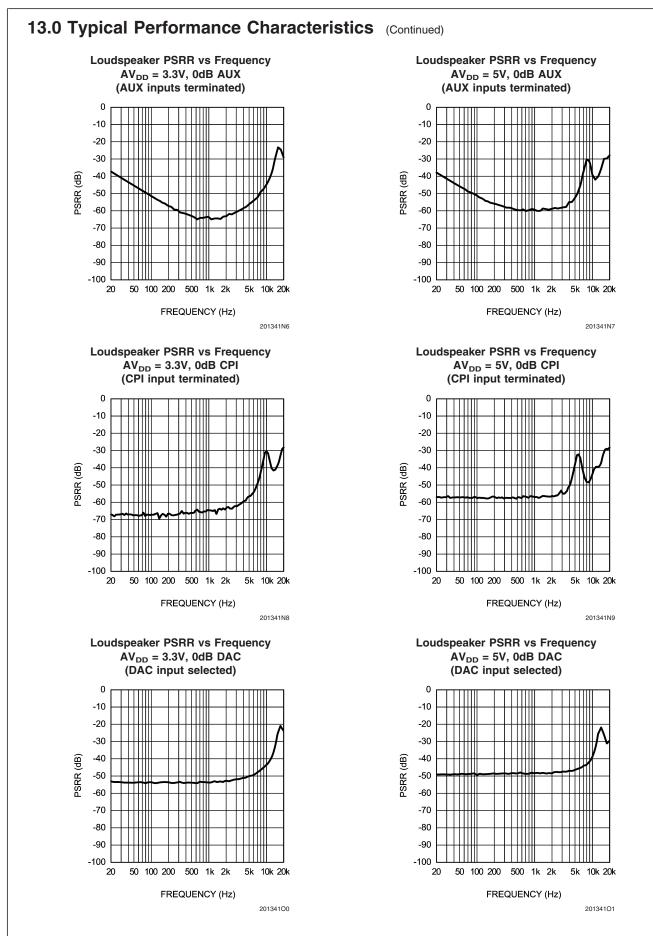

| PSRR <sub>LS</sub>   | Power Supply Rejection Ration   | AUX inputs terminated                             |                     |                   |        |

|                      | (Loudspeaker)                   | $C_{BYPASS} = 1.0 \ \mu F$                        | 54                  |                   | dB     |

|                      |                                 | $V_{\text{RIPPLE}} = 200 \text{ mV}_{\text{P-P}}$ | 01                  |                   | üD     |

|                      |                                 | f <sub>RIPPLE</sub> = 217 Hz                      |                     |                   |        |

| $SNR_{LS}$           | Signal to Noise Ratio           | From 0 dB Analog AUX input at                     | 76                  |                   | dB     |

|                      |                                 | 1 kHz, A-weighted                                 | -                   |                   | -      |

| e <sub>N</sub>       | Output Noise                    | A-weighted                                        | 350                 |                   | μV     |

| V <sub>os</sub>      | Offset Voltage                  |                                                   | 7                   |                   | mV     |

|                      | EAMPLIFIER                      | 1                                                 | 1                   |                   |        |

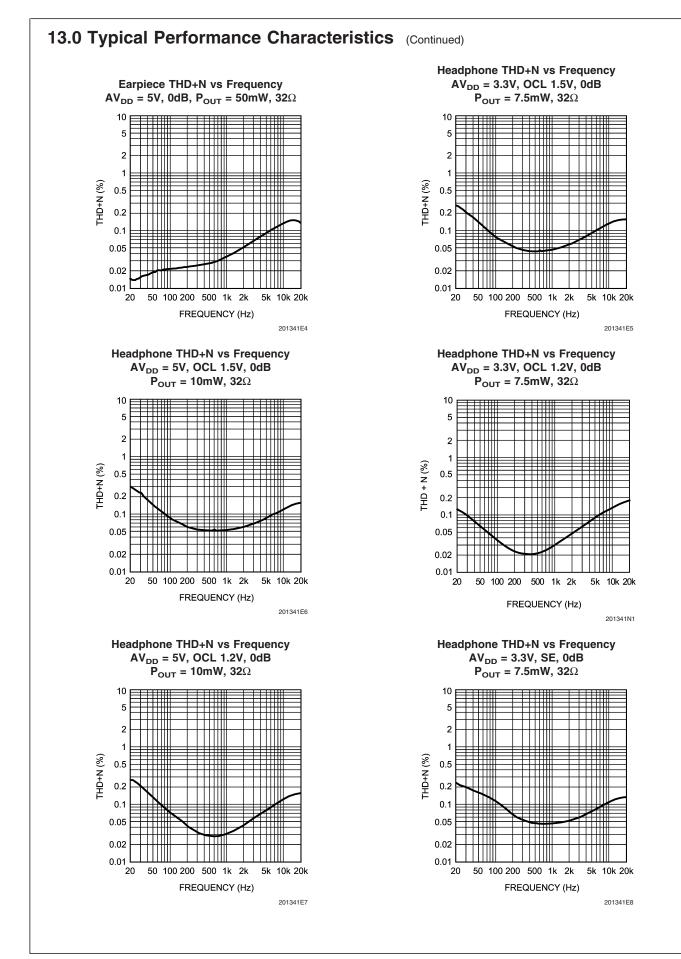

| P <sub>HP</sub>      | Headphone Power                 | 32Ω load, 3.3V, SE                                | 33                  | 20                | mW     |

|                      |                                 |                                                   |                     |                   | (min)  |

|                      |                                 | 16Ω load, 3.3V, SE                                | 52                  |                   | mW     |

|                      |                                 | 32Ω load, 3.3V, OCL, VCM = 1.5V                   | 31                  |                   | mW     |

|                      |                                 | 32Ω load, 3.3V, OCL, VCM = 1.2V                   | 20                  |                   | mW     |

|                      |                                 | 16Ω load, 3.3V, OCL, VCM = 1.5V                   | 50                  |                   | mW     |

|                      |                                 | 16Ω load, 3.3V, OCL, VCM = 1.2V                   | 32                  |                   | mW     |

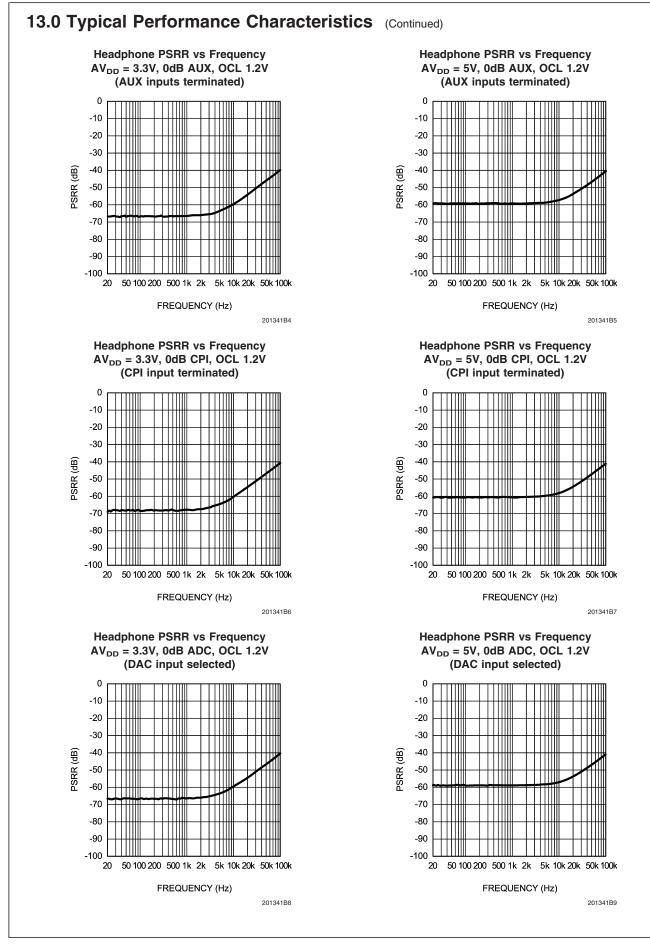

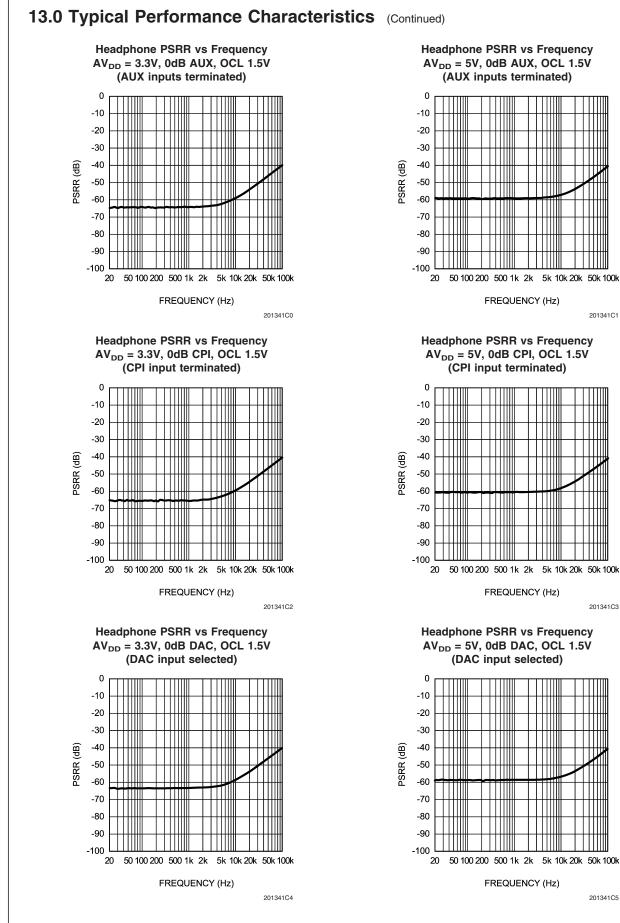

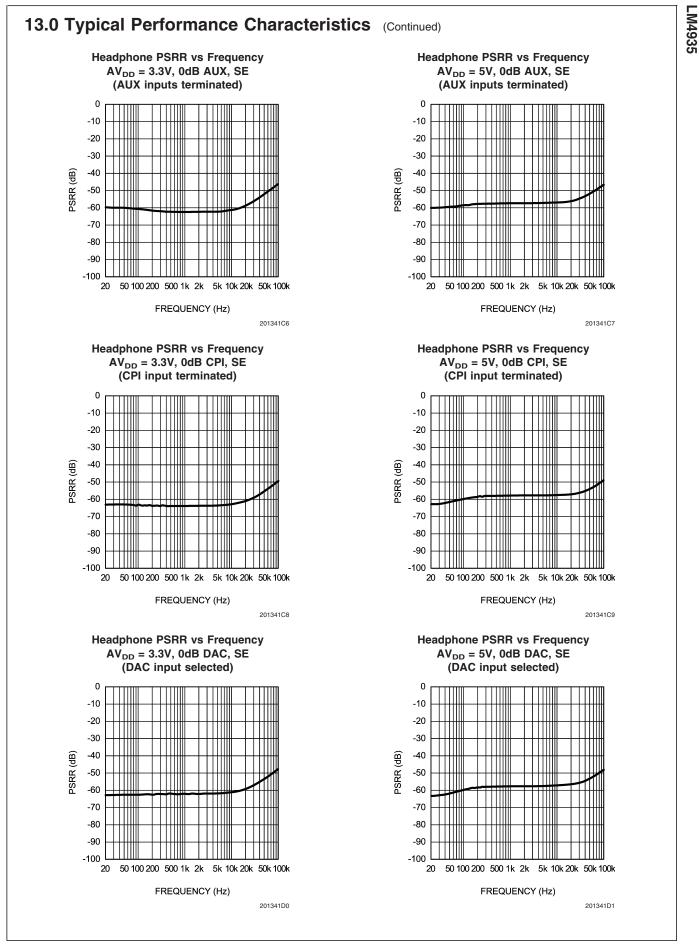

|                      |                                 | AUX inputs terminated                             |                     |                   |        |

|                      |                                 | $C_{BYPASS} = 1.0 \ \mu F$                        |                     |                   |        |

|                      |                                 | $V_{\text{RIPPLE}} = 200 \text{ mV}_{\text{P-P}}$ |                     |                   |        |

|                      | Power Supply Rejection Ratio    | f <sub>RIPPLE</sub> = 217 Hz                      |                     |                   |        |

| PSRR <sub>HP</sub>   | (Headphones)                    | SE Mode                                           | 60                  |                   | dB     |

|                      |                                 | OCL Mode                                          | 68                  |                   | dB     |

|                      |                                 | VCM = 1.2V                                        |                     |                   |        |

|                      |                                 | OCL Mode                                          | 65                  |                   | dB     |

|                      |                                 | VCM = 1.5V                                        |                     | 1                 |        |

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated  $PLL_V_{DD} = 3.3V$ ,  $D_V_{DD} = 3.3V$ ,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|                    |                                            |                                                   | LM49                |                   |                  |

|--------------------|--------------------------------------------|---------------------------------------------------|---------------------|-------------------|------------------|

| Symbol             | Parameter                                  | Conditions                                        | Typical<br>(Note 6) | Limit<br>(Note 7) | Units            |

| HEADPHON           |                                            | •                                                 |                     |                   |                  |

|                    |                                            | From 0dB Analog AUX input                         |                     |                   |                  |

|                    |                                            | A-weighted                                        |                     |                   |                  |

|                    |                                            | SE Mode                                           | 98                  |                   | dB               |

| SNR <sub>HP</sub>  | Signal to Noise Ratio                      | OCL Mode                                          | 97                  |                   | dB               |

|                    |                                            | VCM = 1.2V                                        |                     |                   | 40               |

|                    |                                            | OCL Mode                                          | 96                  |                   | dB               |

|                    |                                            | VCM = 1.5V                                        | _                   |                   |                  |

| $HP_{THD+N}$       | Headphone Harmonic Distortion              | $32\Omega$ load, $3.3V$ , $P_0 = 7.5mW$           | 0.05                |                   | %                |

| e <sub>N</sub>     | Output Noise                               | A-weighted                                        | 12                  |                   | μV               |

| $\Delta A_{CH-CH}$ | Stereo Channel-to-Channel Gain<br>Mismatch |                                                   | 0.3                 |                   | dB               |

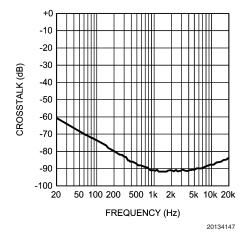

| v                  | Starge Creestell                           | SE Mode                                           | 61                  |                   | dB               |

| X <sub>talk</sub>  | Stereo Crosstalk                           | OCL Mode                                          | 63                  |                   | dB               |

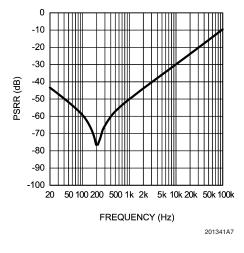

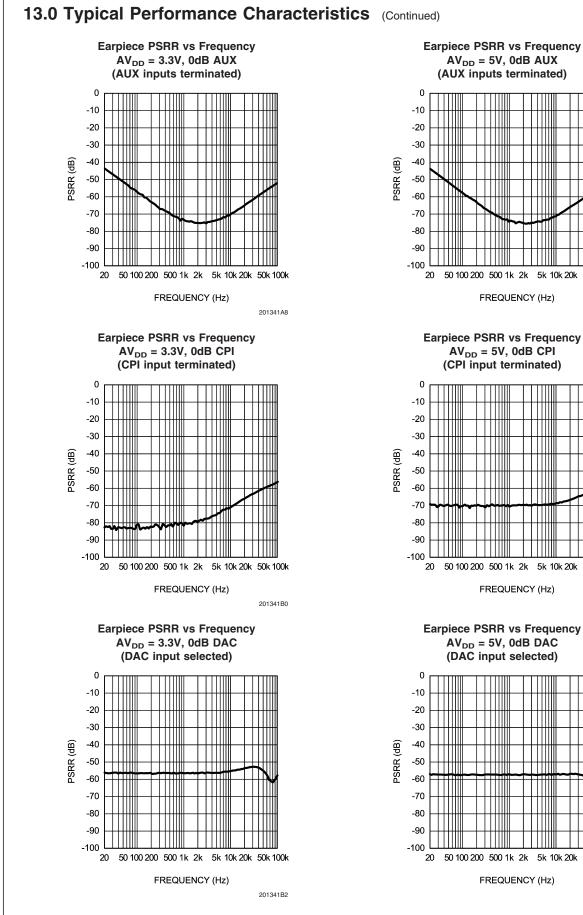

| EARPIECE           | AMPLIFIER                                  |                                                   |                     | ı                 |                  |

| P <sub>EP</sub>    | Earpiece Power                             | 32Ω load, 3.3V                                    | 115                 | 100               | mW<br>(min)      |

|                    |                                            | 16Ω load, 3.3V                                    | 150                 |                   | mW               |

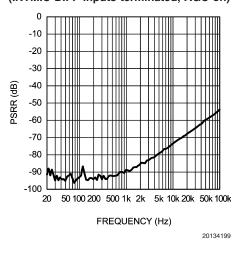

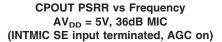

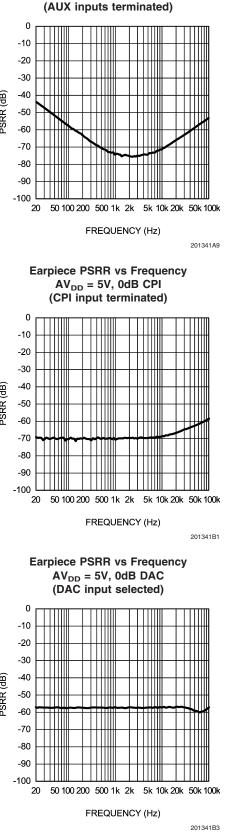

| PSRR <sub>EP</sub> | Power Supply Rejection Ratio               | AUX inputs terminated                             |                     |                   |                  |

|                    | (Earpiece)                                 | C <sub>BYPASS</sub> = 1.0 µF                      | 05                  |                   | ٩D               |

|                    |                                            | $V_{\text{RIPPLE}} = 200 \text{ mV}_{\text{P-P}}$ | 65                  |                   | dB               |

|                    |                                            | F <sub>RIPPLE</sub> = 217 Hz                      |                     |                   |                  |

| SNR <sub>EP</sub>  | Signal to Noise Ratio                      | From 0dB Analog AUX input,                        | 98                  |                   | dB               |

|                    |                                            | A-weighted                                        |                     |                   | UD               |

| $EP_{THD+N}$       | Earpiece Harmonic Distortion               | $32\Omega$ load, $3.3V$ , $P_O = 50mW$            | 0.04                |                   | %                |

| e <sub>N</sub>     | Output Noise                               | A-weighted                                        | 24                  |                   | μV               |

| V <sub>os</sub>    | Offset Voltage                             |                                                   | 15                  |                   | mV               |

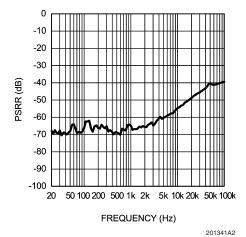

| AUXOUT AN          | MPLIFIER                                   |                                                   |                     |                   |                  |

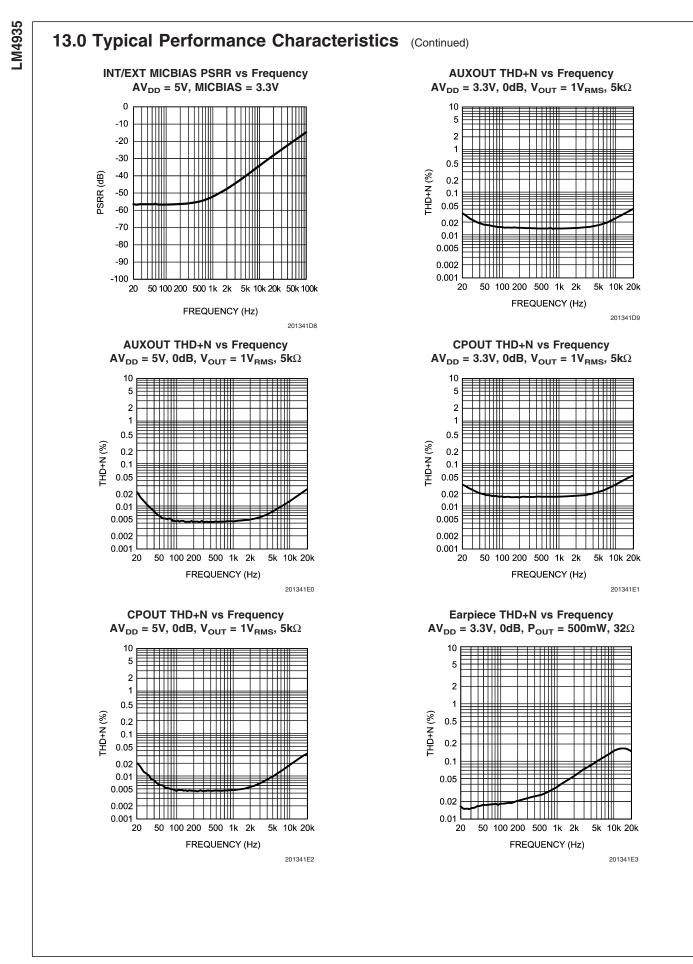

| THD+N              | Total Harmonic Distortion + Noise          | $V_{O} = 1V_{RMS}$ , 5k $\Omega$ load             | 0.02                |                   | %                |

| PSRR               | Power Supply Rejection Ratio               | AUX inputs terminated                             |                     |                   |                  |

|                    |                                            | $C_{BYPASS} = 1.0 \mu F$                          | 70                  |                   | dB               |

|                    |                                            | V <sub>RIPPLE</sub> = 200mVPP                     |                     |                   | 0.2              |

|                    |                                            | f <sub>RIPPLE</sub> = 217Hz                       |                     |                   |                  |

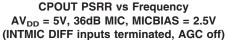

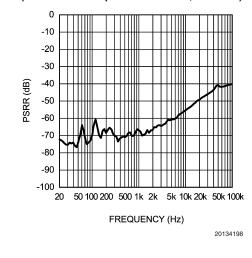

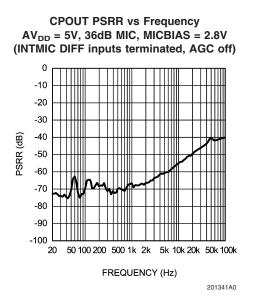

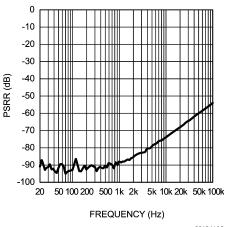

| CP_OUT AN          |                                            |                                                   | 1                   |                   |                  |

| THD+N              | Total Harmonic Distortion + Noise          | $V_{O} = 1V_{RMS}$ , 5k $\Omega$ load             | 0.02                |                   | %                |

| PSRR               | Power SUpply Rejection Ratio               | $C_{BYPASS} = 1.0 \mu F$                          |                     |                   |                  |

|                    |                                            | $V_{\text{RIPPLE}} = 200 \text{mVPP}$             | 68                  |                   | dB               |

|                    |                                            | f <sub>RIPPLE</sub> = 217Hz                       |                     |                   |                  |

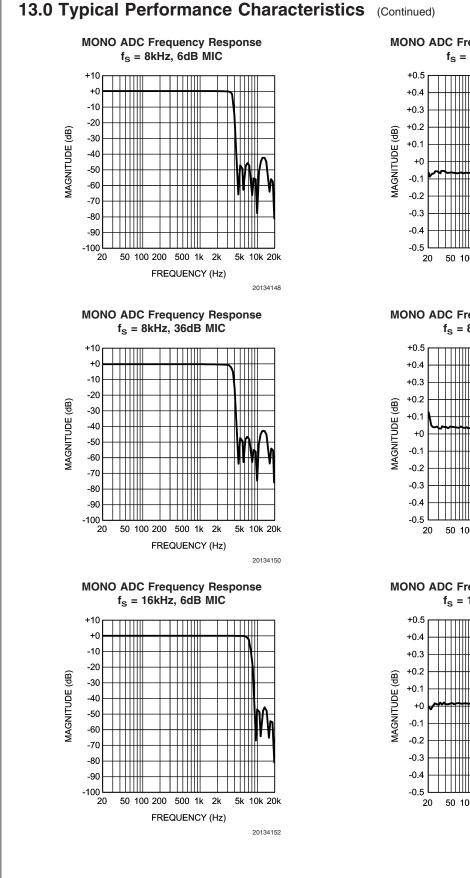

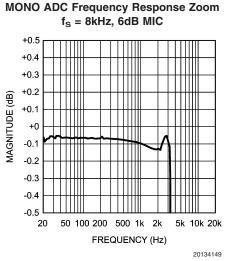

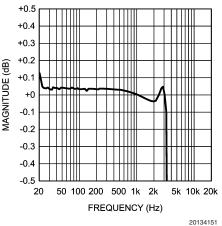

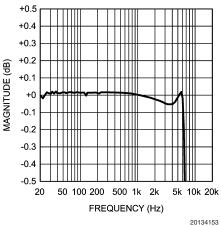

| MONO ADC           |                                            | 1                                                 | 10.05               | 1 1               |                  |

| R <sub>ADC</sub>   | ADC Ripple                                 |                                                   | ±0.25               |                   | dB               |

| PB <sub>ADC</sub>  | ADC Passband                               | Lower (HPF Mode 1), f <sub>S</sub> = 8 kHz        | 300                 |                   | Hz               |

|                    |                                            | Upper                                             | 3470                |                   | Hz               |

| SBA <sub>ADC</sub> | ADC Stopband Attenuation                   | Above Passband                                    | 60                  |                   | dB               |

|                    |                                            | HPF Notch, 50 Hz/60 Hz (worst case)               | 58                  |                   | dB               |

| SNR <sub>ADC</sub> | ADC Signal to Noise Ratio                  | From CPI, A-weighted                              | 90                  |                   | dB               |

| ADCLEVEL           | ADC Full Scale Input Level                 |                                                   | 1                   |                   | V <sub>RMS</sub> |

LM4935

LM4935

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated PLL\_V<sub>DD</sub> = 3.3V,  $D_V_{DD}$  = 3.3V, BB\_V<sub>DD</sub> = 1.8V, A\_V<sub>DD</sub> = 3.3V, LS\_V<sub>DD</sub> = 3.3V. The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|                          | Parameter                   | Conditions                                                                  | LM49                | 1                 |                  |

|--------------------------|-----------------------------|-----------------------------------------------------------------------------|---------------------|-------------------|------------------|

| Symbol                   |                             |                                                                             | Typical<br>(Note 6) | Limit<br>(Note 7) | Units            |

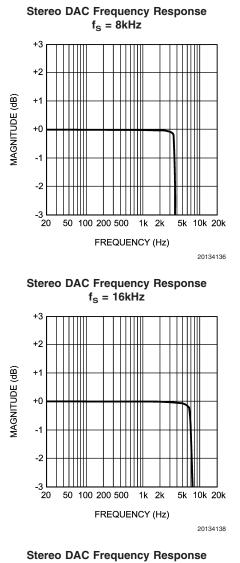

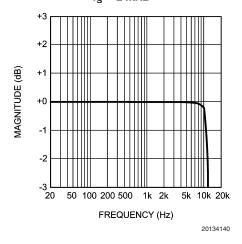

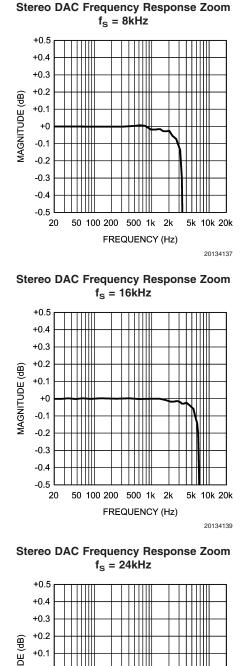

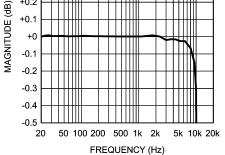

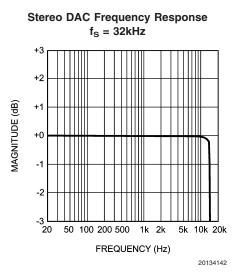

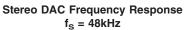

| STEREO DAC               |                             |                                                                             |                     |                   |                  |

| R <sub>DAC</sub>         | DAC Ripple                  |                                                                             | 0.1                 |                   | dB               |

| PB <sub>DAC</sub>        | DAC Passband                |                                                                             | 20                  |                   | kHz              |

| SBA <sub>DAC</sub>       | DAC Stopband Attenuation    |                                                                             | 70                  |                   | dB               |

| SNR <sub>DAC</sub>       | DAC Signal to Noise Ratio   | A-weighted, AUXOUT                                                          | 88                  |                   | dB               |

| DR <sub>DAC</sub>        | DAC Dynamic Range           |                                                                             | 96                  |                   | dB               |

| DAC <sub>LEVEL</sub>     | DAC Full Scale Output Level |                                                                             | 1                   |                   | V <sub>RMS</sub> |

| PLL                      |                             |                                                                             |                     | 1                 | 1                |

| F <sub>IN</sub>          | Input Frequency Range       | Min                                                                         | 0.5                 |                   | MHz              |

|                          |                             | Max                                                                         | 30                  |                   | MHz              |

| I2S/PCM                  |                             | I                                                                           |                     | 1                 |                  |

|                          |                             | f <sub>s</sub> = 48kHz; 16 bit mode                                         | 1.536               |                   | MHz              |

| t                        |                             | $f_s = 48$ kHz; 25 bit mode                                                 | 2.4                 |                   | MHz              |

| f <sub>I2SCLK</sub>      | I2S CLK Frequency           | f <sub>s</sub> = 8kHz; 16 bit mode                                          | 0.256               |                   | MHz              |

|                          |                             | f <sub>s</sub> = 8kHz; 25 bit mode                                          | 0.4                 |                   | MHz              |

|                          |                             | f <sub>S</sub> = 48kHz; 16 bit mode                                         | 0.768               |                   | MHz              |

| _                        |                             | f <sub>s</sub> = 48kHz; 25 bit mode                                         | 1.2                 |                   | MHz              |

| f <sub>PCMCLK</sub>      | PCM CLK Frequency           | f <sub>s</sub> = 8kHz; 16 bit mode                                          | 0.128               |                   | MHz              |

|                          |                             | f <sub>S</sub> = 8kHz; 25 bit mode                                          | 0.2                 |                   | MHz              |

| DC <sub>I2S_CLK</sub>    | I2S_CLK Duty Cycle          | Min                                                                         |                     | 40                | % (mi            |

| 123_0LK                  |                             | Max                                                                         |                     | 60                | %                |

|                          | I2S_WS Duty Cycle           |                                                                             | 50                  | 00                | (max<br>%        |

| DC <sub>I2S_WS</sub>     |                             |                                                                             | 50                  |                   | /0               |

|                          | I2C Data Setup Time         | Pofor to Pa 19 for more dotaile                                             |                     | 100               | no (mi           |

| T <sub>I2CSET</sub>      | I2C Data Setup Time         | Refer to Pg. 18 for more details           Refer to Pg. 18 for more details |                     | 100<br>300        | ns (m            |

| T <sub>I2CHOLD</sub>     |                             | nelei lo Fy. To foi more details                                            |                     | 300               | ns (mi           |

| _                        | Enable Setup Time           |                                                                             |                     | 100               | ns (m            |

| T <sub>SPISETENB</sub>   |                             |                                                                             |                     |                   |                  |

| T <sub>SPIHOLD-ENB</sub> | Enable Hold Time            |                                                                             |                     | 100               | ns (m            |

|                          | Data Setup Time             |                                                                             |                     | 100               | ns (m            |

| T <sub>SPIHOLDD</sub>    | Data Hold Time              |                                                                             |                     | 100               | ns (m            |

| T <sub>SPICL</sub>       | Clock Low Time              |                                                                             |                     | 500               | ns (m            |

|                          | Clock High Time             |                                                                             |                     | 500               | ns (m            |

| VOLUME CON               |                             |                                                                             | 40 5                | 1                 | -10-             |

|                          |                             | Minimum Gain w/ AUX_BOOST OFF                                               | -46.5               |                   | dB               |

| VCR <sub>AUX</sub>       | AUX Volume Control Range    | Maximum Gain w/ AUX_BOOST<br>OFF                                            | 0                   |                   | dB               |

| AUA                      |                             | Minimum Gain w/ AUX_BOOST ON                                                | -34.5               |                   | dB               |

|                          |                             | Maximum Gain w/ AUX_BOOST ON                                                | 12                  |                   | dB               |

|                          |                             | Minimum Gain w/ DAC_BOOST OFF                                               | -46.5               |                   | dB               |

|                          |                             | Maximum Gain w/ DAC_BOOST                                                   | 0                   |                   | dB               |

| VCR <sub>DAC</sub>       | DAC Volume Control Range    | OFF<br>Minimum Gain w/ DAC_BOOST ON                                         | -34.5               |                   | 심다               |

|                          |                             |                                                                             |                     |                   | dB               |

|                          |                             | Maximum Gain w/ DAC_BOOST ON                                                | 12                  |                   | dB               |

| VCR <sub>CPIN</sub>      | CPIN Volume Control Range   | Minimum Gain                                                                | -34.5               |                   | dB               |

| 5                        |                             | Maximum Gain                                                                | 12                  |                   | dB               |

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated  $PLL_V_{DD} = 3.3V$ ,  $D_V_{DD} = 3.3V$ ,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|                     |                                             |              | LM49     |          |       |

|---------------------|---------------------------------------------|--------------|----------|----------|-------|

| Symbol              | Parameter                                   | Conditions   | Typical  | Limit    | Units |

|                     |                                             |              | (Note 6) | (Note 7) |       |

| VOLUME CO           | ONTROL                                      | ^<br>        | •        |          |       |

|                     | VCR <sub>MIC</sub> MIC Volume Control Range | Minimum Gain | 6        |          | dB    |

| VCR <sub>MIC</sub>  |                                             | Maximum Gain | 36       |          | dB    |

| VCR <sub>SIDE</sub> | SIDETONE Volume Control Range               | Minimum Gain | -30      |          | dB    |

|                     |                                             | Maximum Gain | 0        |          | dB    |

| SS <sub>AUX</sub>   | AUX VCR Stepsize                            |              | 1.5      |          | dB    |

| SS <sub>DAC</sub>   | DAC VCR Stepsize                            |              | 1.5      |          | dB    |

| SS <sub>CPIN</sub>  | CPIN VCR Stepsize                           |              | 1.5      |          | dB    |

| SS <sub>MIC</sub>   | MIC VCR Stepsize                            |              | 2        |          | dB    |

| SS <sub>SIDE</sub>  | SIDETONE VCR Stepsize                       |              | 3        |          | dB    |

LM4935

LM4935

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated PLL\_V<sub>DD</sub> = 3.3V,  $D_V_{DD}$  = 3.3V, BB\_V<sub>DD</sub> = 1.8V, A\_V<sub>DD</sub> = 3.3V, LS\_V<sub>DD</sub> = 3.3V. The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|           |                                                                                        |                                                                                        | LM4935              |                   |        |

|-----------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|-------------------|--------|

| Symbol    | Parameter                                                                              | Conditions                                                                             | Typical<br>(Note 6) | Limit<br>(Note 7) | Units  |

| UDIO PATH | GAIN W/ STEREO (bit 6 of 0x00h) E                                                      | NABLED (AUX_L & AUX_R signals ide                                                      |                     | lected onto       | mixer) |

|           |                                                                                        | Minimum Gain from AUX input,<br>BOOST OFF                                              | -34.5               |                   | dB     |

|           | Loudspeaker Audio Path Gain                                                            | Maximum Gain from AUX input,<br>BOOST OFF                                              | 12                  |                   | dB     |

|           |                                                                                        | Minimum Gain from CPI input                                                            | -22.5               |                   | dB     |

|           |                                                                                        | Maximum Gain from CPI input                                                            | 24                  |                   | dB     |

|           |                                                                                        | Minimum Gain from AUX input,<br>BOOST OFF                                              | -52.5               |                   | dB     |

|           |                                                                                        | Maximum Gain from AUX input,<br>BOOST OFF                                              | -6                  |                   | dB     |

|           |                                                                                        | Minimum Gain from CPI input                                                            | -40.5               |                   | dB     |

|           | Headphone Audio Path Gain                                                              | Maximum Gain from CPI input                                                            | 6                   |                   | dB     |

|           |                                                                                        | Minimum Gain from MIC input using<br>SIDETONE path w/ VCR <sub>MIC</sub> gain =<br>6dB | -30                 |                   | dB     |

|           | Maximum Gain from MIC input using<br>SIDETONE path w/ VCR <sub>MIC</sub> gain =<br>6dB | 0                                                                                      |                     | dB                |        |

|           |                                                                                        | Minimum Gain from AUX input,<br>BOOST OFF                                              | -40.5               |                   | dB     |

|           |                                                                                        | Maximum Gain from AUX input,<br>BOOST OFF                                              | 6                   |                   | dB     |

|           |                                                                                        | Minimum Gain from CPI input                                                            | -28.5               |                   | dB     |

|           | Earpiece Audio Path Gain                                                               | Maximum Gain from CPI input                                                            | 18                  |                   | dB     |

|           |                                                                                        | Minimum Gain from MIC input using<br>SIDETONE path w/ VCR <sub>MIC</sub> gain =<br>6dB | -18                 |                   | dB     |

|           |                                                                                        | Maximum Gain from MIC input using<br>SIDETONE path w/ VCR <sub>MIC</sub> gain =<br>6dB | 12                  |                   | dB     |

|           |                                                                                        | Minimum Gain from AUX input,<br>BOOST OFF                                              | -46.5               |                   | dB     |

|           | AUXOUT Audio Path Gain                                                                 | Maximum Gain from AUX input,<br>BOOST OFF                                              | 0                   |                   | dB     |

|           |                                                                                        | Minimum Gain from CPI input                                                            | -34.5               |                   | dB     |

|           |                                                                                        | Maximum Gain from CPI input                                                            | 12                  |                   | dB     |

|           |                                                                                        | Minimum Gain from AUX input,<br>BOOST OFF                                              | -46.5               |                   | dB     |

|           | CPOUT Audio Path Gain                                                                  | Maximum Gain from AUX input,<br>BOOST OFF                                              | 0                   |                   | dB     |

|           |                                                                                        | Minimum Gain from MIC input                                                            | 6                   |                   | dB     |

|           |                                                                                        | Maximum Gain from MIC input                                                            | 36                  |                   | dB     |

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated  $PLL_V_{DD} = 3.3V$ ,  $D_V_{DD} = 3.3V$ ,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

|             |                            |                                                                  | LM4935              |                   |       |  |

|-------------|----------------------------|------------------------------------------------------------------|---------------------|-------------------|-------|--|

| Symbol      | Parameter Conditions       |                                                                  | Typical<br>(Note 6) | Limit<br>(Note 7) | Units |  |

| Total DC Po | wer Dissipation            |                                                                  |                     |                   |       |  |

|             |                            | DAC ( $f_s = 48$ kHz) and HP ON                                  |                     |                   |       |  |

|             |                            | f <sub>MCLK</sub> = 12MHz, PLL OFF                               | 57                  |                   | mW    |  |

|             | MP3 Mode Power Dissipation | f <sub>MCLK</sub> = 13MHz, PLL ON<br>f <sub>PLLOUT</sub> = 12MHz | 63                  |                   | mW    |  |

|             |                            | $f_{MCLK}$ = 19.2MHz, PLL ON<br>$f_{PLLOUT}$ = 12MHz             | 64                  |                   | mW    |  |

|             |                            | AUX Inputs selected and HP ON                                    |                     |                   |       |  |

|             | EM Made Dewer Dissinction  | f <sub>MCLK</sub> = 12MHz, PLL OFF                               | 24                  |                   | mW    |  |

|             | FM Mode Power Dissipation  | f <sub>MCLK</sub> = 13MHz, PLL OFF                               | 25                  |                   | mW    |  |

|             |                            | f <sub>MCLK</sub> = 19.2MHz, PLL OFF                             | 27                  |                   | mW    |  |

|             |                            | PCM DAC ( $f_S$ = 8kHz) + ADC ( $f_S$ = 8kHz) and EP ON          |                     |                   |       |  |

|             | VOICE CODEC Mode Power     | f <sub>MCLK</sub> = 12MHz, PLL OFF                               | 49                  |                   | mW    |  |

|             | Dissipation                | f <sub>MCLK</sub> = 13MHz, PLL OFF                               | 50                  |                   | mW    |  |

|             |                            | $f_{MCLK}$ = 19.2MHz, PLL ON<br>$f_{PLLOUT}$ = 12MHz             | 56                  |                   | mW    |  |

|             |                            | CP IN selected. EP and CPOUT ON                                  |                     |                   |       |  |

|             | VOICE Module Mode Power    | f <sub>MCLK</sub> = 12MHz, PLL OFF                               | 30                  |                   | mW    |  |

|             | Dissipation                | f <sub>MCLK</sub> = 13MHz, PLL OFF                               | 31                  |                   | mW    |  |

|             |                            | f <sub>MCLK</sub> = 19.2MHz, PLL OFF                             | 33                  |                   | mW    |  |

LM4935

**10.0 Electrical Characteristics** (Notes 1, 2) Unless otherwise stated  $PLL_V_{DD} = 3.3V$ ,  $D_V_{DD} = 3.3V$ ,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C. (Continued)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits.

Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

**Note 2:** All voltages are measured with respect to the relevant  $V_{SS}$  pin unless otherwise specified. All grounds should be coupled as close as possible to the device. **Note 3:** The maximum power dissipation must be de-rated at elevated temperatures and is dictated by  $TJ_{MAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum

allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower.

Note 4: Human body model: 100pF discharged through a  $1.5 k\Omega$  resistor.

Note 5: Machine model: 220pF - 240pF discharged through all pins.

Note 6: Typical values are measured at  $25^{\circ}C$  and represent the parametric norm.

Note 7: Limits are guaranteed to Nationals AOQL (Average Outgoing Quality Level).

Note 8: Best operation is achieved by maintaining  $3.0V < A_V_{DD} < 5.0$  and  $3.0V < D_V_{DD} < 3.6V$  and  $A_V_{DD} > D_V_{DD}$ .

Note 9: Digital shutdown current is measured with system clock set for PLL output while the PLL is disabled.

Note 10: Disabling or bypassing the PLL will usually result in an improvement in noise measurements.

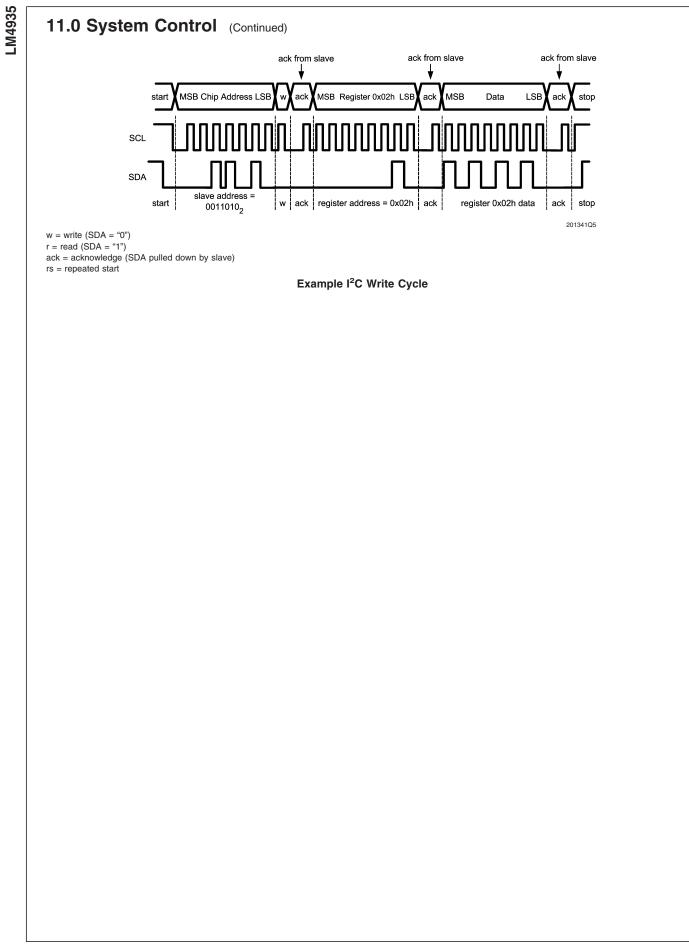

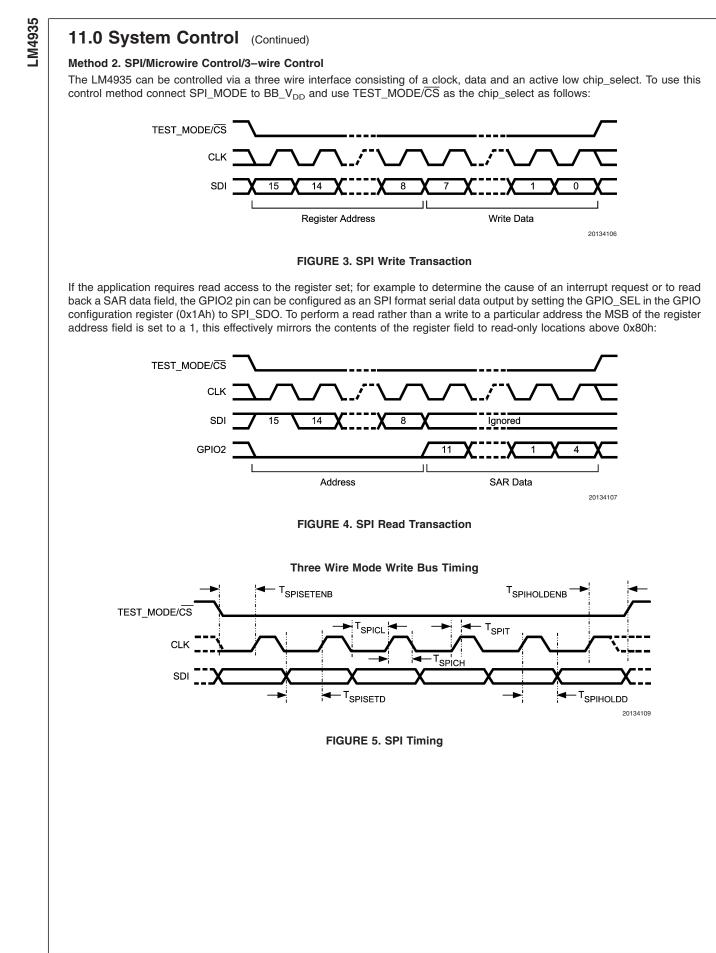

## 11.0 System Control

#### Method 1. I<sup>2</sup>C Compatible Interface

#### 11.1 I<sup>2</sup>C SIGNALS

In I<sup>2</sup>C mode the LM4935 pin SCL is used for the I<sup>2</sup>C clock SCL and the pin SDA is used for the I<sup>2</sup>C data signal SDA. Both these signals need a pull-up resistor according to I<sup>2</sup>C specification. The I<sup>2</sup>C slave address for LM4935 is **0011010<sub>2</sub>**.

#### 11.2 I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

#### 11.3 I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the  $I^2C$  session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The  $I^2C$  master always generates START and STOP bits. The  $I^2C$  bus is considered to be busy after START condition and free after STOP condition. During data transmission,  $I^2C$  master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

#### **11.4 TRANSFERRING DATA**

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9<sup>th</sup> clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM4935 address is **0011010**<sub>2</sub>. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Register changes take an effect at the SCL rising edge during the last ACK from slave.

## 11.0 System Control (Continued)

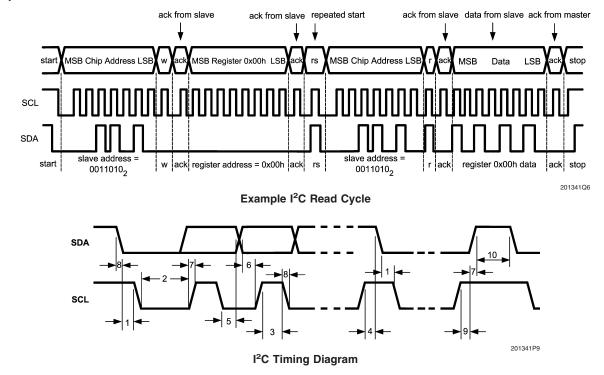

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the Read Cycle waveform.

#### 11.5 I<sup>2</sup>C TIMING PARAMETERS

| Symbol         | Parameter                                                       | Limit                | Units |    |

|----------------|-----------------------------------------------------------------|----------------------|-------|----|

|                |                                                                 | Min                  | Мах   |    |

| 1              | Hold Time (repeated) START Condition                            | 0.6                  |       | μs |

| 2              | Clock Low Time                                                  | 1.3                  |       | μs |

| 3              | Clock High Time                                                 | 600                  |       | ns |

| 4              | Setup Time for a Repeated START Condition                       | 600                  |       | ns |

| 5              | Data Hold Time (Output direction, delay generated by LM4935)    | 300                  | 900   | ns |

| 5              | Data Hold Time (Input direction, delay generated by the Master) | 0                    | 900   | ns |

| 6              | Data Setup Time                                                 | 100                  |       | ns |

| 7              | Rise Time of SDA and SCL                                        | 20+0.1C <sub>b</sub> | 300   | ns |

| 8              | Fall Time of SDA and SCL                                        | 15+0.1C <sub>b</sub> | 300   | ns |

| 9              | Set-up Time for STOP condition                                  | 600                  |       | ns |

| 10             | Bus Free Time between a STOP and a START Condition              | 1.3                  |       | μs |

| C <sub>b</sub> | Capacitive Load for Each Bus Line                               | 10                   | 200   | pF |

NOTE: Data guaranteed by design

| Address<br>0x00h<br>0x01h<br>0x02h<br>0x03h<br>0x04h<br>0x05h<br>0x06h | Register<br>BASIC<br>CLOCKS<br>PLL_M | 7<br>OCL         | 6           | 5              |                |              |               |          |         |

|------------------------------------------------------------------------|--------------------------------------|------------------|-------------|----------------|----------------|--------------|---------------|----------|---------|

| 0x01h<br>0x02h<br>0x03h<br>0x04h<br>0x05h                              | CLOCKS                               | OCL              |             | •              | 4              | 3            | 2             | 1        | 0       |

| 0x02h<br>0x03h<br>0x04h<br>0x05h                                       |                                      |                  | STEREO      | CAP_           | SIZE           | USE_OSC      | PLL_ENB       | CHP_     | MODE    |

| 0x03h<br>0x04h<br>0x05h                                                | PLL M                                |                  |             | R_D            | VIV            |              |               | ADCLK    | DACCLK  |

| 0x04h<br>0x05h                                                         |                                      | PLLINPUT         |             |                | PLL_M          |              |               |          | RSVD    |

| 0x05h                                                                  | PLL_N                                |                  |             |                | PLL_I          | N            |               |          |         |

|                                                                        | PLL_P                                | RSVD             |             | Q_DIV          |                |              | PLL_P         |          | RSVD    |

| 0x06h                                                                  | PLL_MOD                              | RSVD             | DITHEF      | LEVEL          |                | F            | PLL_N_MOD     |          |         |

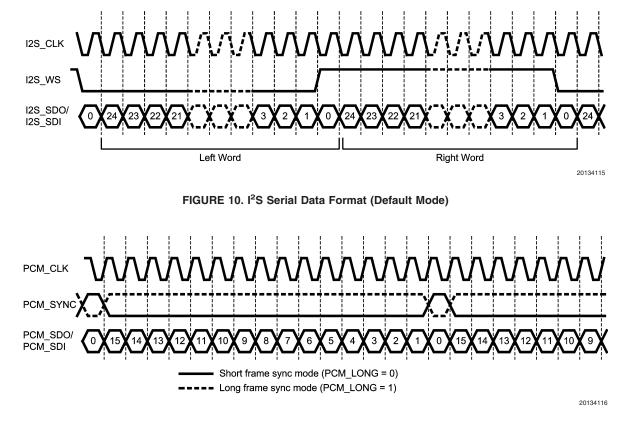

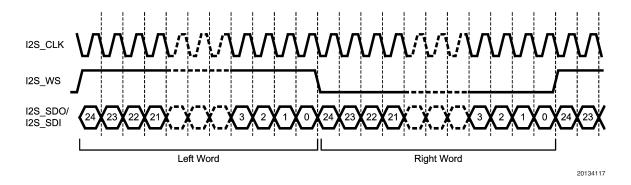

|                                                                        | ADC_1                                | HPF_N            | IODE        | SAMPLI         | E_RATE         | RIGHT        | LEFT          | CPI      | MIC     |

| 0x07h                                                                  | ADC_2                                | IF216            | ADC_I2SM    | AGO            | C_FRAME_TI     | ME           | ADCMUTE       | COMPND   | U/ALAW  |

| 0x08h                                                                  | AGC_1                                | NOISE_           | GATE_THRE   | SHOLD          | NG_ON          | A            | GC_TARGE      | Г        | AGC_ENB |

| 0x09h                                                                  | AGC_2                                | AGC_TIGHT        |             | AGC_DECAY      | ,              |              | AGC_MA        | X_GAIN   |         |

| 0x0Ah                                                                  | AGC_3                                | A                | GC_ATTACK   |                |                | AGO          | C_HOLD_TIM    | 1E       |         |

| 0x0Bh                                                                  | MIC_1                                |                  | INT_EXT     | SE_DIFF        | MUTE           |              | PREAM         | P_GAIN   |         |

| 0x0Ch                                                                  | MIC_2                                |                  |             | BTN_DEBO       | UNCE_TIME      | BTNTYPE      | MIC_BIAS_     | VOLTAGE  | VCMVOLT |

| 0x0Dh                                                                  | SIDETONE                             |                  |             |                |                |              | SIDETONI      | E_ATTEN  |         |

| 0x0Eh                                                                  | CP_INPUT                             |                  |             | MUTE           |                | (            | CPI_LEVEL     |          |         |

| 0x0Fh                                                                  | AUX_LEFT                             | AUX_DAC          | MUTE        | BOOST          |                | AUX          | LEFT_LEV      | EL       |         |