## **LP3874-ADJ**

# 0.8A Fast Ultra Low Dropout Linear Regulators

## **General Description**

The LP3874-ADJ fast ultra low-dropout linear regulators operate from a +2.5V to +7.0V input supply. These ultra low dropout linear regulators respond very quickly to step changes in load, which makes them suitable for low voltage microprocessor applications. The LP3874-ADJ is developed on a CMOS process which allows low quiescent current operation independent of output load current. This CMOS process also allows the LP3874-ADJ to operate under extremely low dropout conditions.

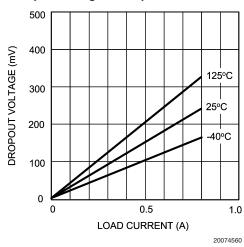

**Dropout Voltage:** Ultra low dropout voltage; typically 24mV at 80mA load current and 240mV at 0.8A load current.

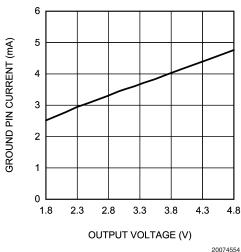

Ground Pin Current: Typically 6mA at 0.8A load current.

**Shutdown Mode:** Typically 10nA quiescent current when the shutdown pin is pulled low.

**Adjustable Output Voltage:** The output voltage may be programmed via two external resistors.

#### **Features**

- Ultra low dropout voltage

- Low ground pin current

- Load regulation of 0.04%

- 10nA quiescent current in shutdown mode

- Guaranteed output current of 0.8A DC

- Available in TO-263, TO-220 and SOT-223 packages

- Minimum output capacitor requirements

- Overtemperature/overcurrent protection

- -40°C to +125°C junction temperature range

#### **Applications**

- Microprocessor power supplies

- GTL, GTL+, BTL, and SSTL bus terminators

- Power supplies for DSPs

- SCSI terminator

- Post regulators

- High efficiency linear regulators

- Battery chargers

- Other battery powered applications

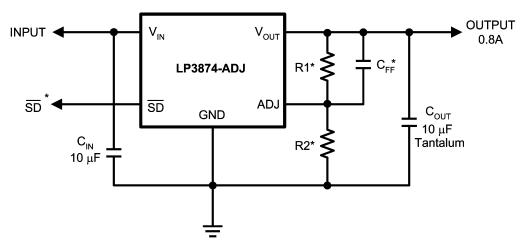

# **Typical Application Circuit**

$$V_{OUT} = 1.216 \times (1 + \frac{R1}{R2})$$

\*See Application Hints

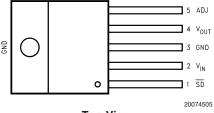

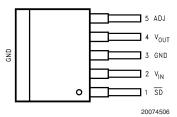

# **Connection Diagrams**

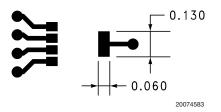

Top View TO220-5 Package Bent, Staggered Leads

Top View SOT223-5 Package

Top View TO263-5 Package

# Pin Description for TO220-5 and TO263-5 Packages

| Pin # | LP3874-ADJ       |                    |  |  |

|-------|------------------|--------------------|--|--|

|       | Name             | Function           |  |  |

| 1     | SD               | Shutdown           |  |  |

| 2     | V <sub>IN</sub>  | Input Supply       |  |  |

| 3     | GND              | Ground             |  |  |

| 4     | V <sub>OUT</sub> | Output Voltage     |  |  |

| 5     | ADJ              | Set Output Voltage |  |  |

# Pin Description for SOT223-5 Package

| Pin # | LP3874-ADJ       |                    |  |  |

|-------|------------------|--------------------|--|--|

|       | Name             | Function           |  |  |

| 1     | SD               | Shutdown           |  |  |

| 2     | V <sub>IN</sub>  | Input Supply       |  |  |

| 3     | V <sub>OUT</sub> | Output Voltage     |  |  |

| 4     | ADJ              | Set Output Voltage |  |  |

| 5     | GND              | Ground             |  |  |

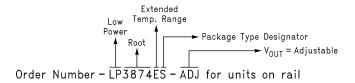

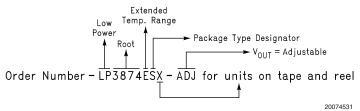

# **Ordering Information**

Package Type Designator is "T" for TO220 package, "S" for TO263 package, and "MP" for SOT223-5 package.

**TABLE 1. Package Marking and Ordering Information**

| Output<br>Voltage | Order Number   | Description<br>(Current, Option) | Package Type | Package Marking | Supplied As:           |

|-------------------|----------------|----------------------------------|--------------|-----------------|------------------------|

| ADJ               | LP3874EMP-ADJ  | 0.8A, Adj                        | SOT223-5     | LHKB            | 1000 Units on Tape and |

|                   |                |                                  |              |                 | Reel                   |

| ADJ               | LP3874EMPX-ADJ | 0.8A, Adj                        | SOT223-5     | LHKB            | 2000 Units on Tape and |

|                   |                |                                  |              |                 | Reel                   |

| ADJ               | LP3874ES-ADJ   | 0.8A, Adj                        | TO263-5      | LP3874ES-ADJ    | Rail                   |

| ADJ               | LP3874ESX-ADJ  | 0.8A, Adj                        | TO263-5      | LP3874ES-ADJ    | Tape and Reel          |

| ADJ               | LP3874ET-ADJ   | 0.8A, Adj                        | TO220-5      | LP3874ET-ADJ    | Rail                   |

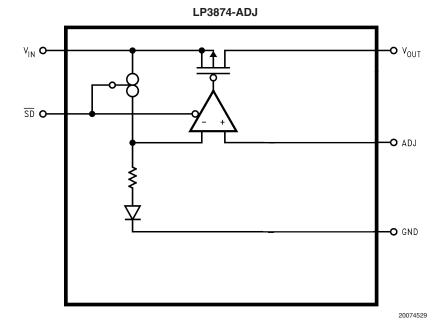

# **Block Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Storage Temperature Range -65°C to +150°C

Lead Temperature

(Soldering, 5 sec.) 260°C

ESD Rating (Note 3) 2 kV

Internally Limited

Power Dissipation (Note 2) Input Supply Voltage (Survival) -0.3V to +7.5V

Shutdown Input Voltage

-0.3V to 7.5V(Survival)

Output Voltage (Survival), (Note

6), (Note 7) -0.3V to +6.0VI<sub>OUT</sub> (Survival) Short Circuit Protected

## **Operating Ratings**

Input Supply Voltage (Operating),

2.5V to 7.0V (Note 10)

Shutdown Input Voltage

-0.3V to 7.0V (Operating)

Maximum Operating Current (DC) A8.0

Operating Junction Temp. Range -40°C to +125°C

## **Electrical Characteristics LP3874-ADJ**

Limits in standard typeface are for  $T_{ij} = 25$ °C, and limits in **boldface type** apply over the **full operating temperature range**. Unless otherwise specified:  $V_{IN} = V_{O(NOM)} + 1V$ ,  $I_L = 10$  mA,  $C_{OUT} = 10\mu F$ ,  $V_{SD} = 2V$ .

| Symbol                             | Parameter                                      | Conditions                                                        | Тур                 | <b>LP3874-ADJ</b> (Note 5) |                       | Units |

|------------------------------------|------------------------------------------------|-------------------------------------------------------------------|---------------------|----------------------------|-----------------------|-------|

|                                    |                                                |                                                                   | (Note 4)            | Min                        | Max                   |       |

| $V_{ADJ}$                          | Adjust Pin Voltage                             | $V_{OUT} + 1V \le V_{IN} \le 7V$ $10 \text{ mA} \le I_L \le 0.8A$ | 1.216               | 1.198<br><b>1.180</b>      | 1.234<br><b>1.253</b> | V     |

| I <sub>ADJ</sub>                   | Adjust Pin Input Voltage                       | $V_{OUT} + 1V \le V_{IN} \le 7V$ $10 \text{ mA} \le I_L \le 0.8A$ | 10                  |                            | 100                   | nA    |

| $\Delta V_{OL}$                    | Output Voltage Line<br>Regulation (Note 8)     | $V_{OUT} + 1V \le V_{IN} \le 7.0V$                                | 0.02<br><b>0.06</b> |                            |                       | %     |

| $\Delta V_{O} / \Delta I_{OUT}$    | Output Voltage Load<br>Regulation<br>(Note 8)  | 10 mA ≤ I <sub>L</sub> ≤ 0.8A                                     | 0.04<br><b>0.1</b>  |                            |                       | %     |

| V <sub>IN</sub> - V <sub>OUT</sub> | Dropout Voltage<br>(Note 9)                    | I <sub>L</sub> = 80 mA                                            | 24                  |                            | 35<br><b>40</b>       | mV    |

|                                    |                                                | I <sub>L</sub> = 0.8A                                             | 240                 |                            | 300<br><b>350</b>     |       |

| I <sub>GND</sub>                   | Ground Pin Current In<br>Normal Operation Mode | I <sub>L</sub> = 80 mA                                            | 5                   |                            | 9<br><b>10</b>        | m A   |

|                                    |                                                | I <sub>L</sub> = 0.8A                                             | 6                   |                            | 14<br><b>15</b>       | mA    |

| I <sub>GND</sub>                   | Ground Pin Current In<br>Shutdown Mode         | $V_{SD} \le 0.3V$ $-40^{\circ}C \le T_{J} \le 85^{\circ}C$        | 0.01                |                            | 10<br><b>50</b>       | μΑ    |

| I <sub>O(PK)</sub>                 | Peak Output Current                            | V <sub>O</sub> ≥ V <sub>O(NOM)</sub> - 4%                         | 1                   |                            |                       | Α     |

| Short Circuit                      | Protection                                     | •                                                                 | •                   | •                          | '                     |       |

| I <sub>sc</sub>                    | Short Circuit Current                          |                                                                   | 2.3                 |                            |                       | Α     |

# Electrical Characteristics LP3874-ADJ (Continued)

Limits in standard typeface are for  $T_J = 25^{\circ}C$ , and limits in **boldface type** apply over the **full operating temperature range**. Unless otherwise specified:  $V_{IN} = V_{O(NOM)} + 1V$ ,  $I_L = 10$  mA,  $C_{OUT} = 10\mu F$ ,  $V_{SD} = 2V$ .

| Symbol            | Parameter            | Conditions                                                             | Typ<br>(Note 4) | <b>LP3874-ADJ</b> (Note 5) |     | Units    |

|-------------------|----------------------|------------------------------------------------------------------------|-----------------|----------------------------|-----|----------|

|                   |                      |                                                                        |                 | Min                        | Max |          |

| Shutdown Ir       | nput                 |                                                                        | •               |                            |     |          |

| M                 | Shutdown Threshold   | Output = High                                                          | V <sub>IN</sub> | 2                          |     | V        |

| $V_{SDT}$         |                      | Output = Low                                                           | 0               |                            | 0.3 | V        |

| T <sub>dOFF</sub> | Turn-off delay       | I <sub>L</sub> = 0.8A                                                  | 20              |                            |     | μs       |

| T <sub>dON</sub>  | Turn-on delay        | I <sub>L</sub> = 0.8A                                                  | 25              |                            |     | μs       |

| I <sub>SD</sub>   | SD Input Current     | $V_{SD} = V_{IN}$                                                      | 1               |                            |     | nA       |

| AC Paramet        | ers                  |                                                                        |                 |                            |     |          |

| PSRR              | Ripple Rejection     | $V_{IN} = V_{OUT} + 1V$ $C_{OUT} = 10uF$ $V_{OUT} = 3.3V, f = 120Hz$   | 73              |                            |     | dB       |

|                   |                      | $V_{IN} = V_{OUT} + 0.5V$ $C_{OUT} = 10uF$ $V_{OUT} = 3.3V, f = 120Hz$ | 57              |                            |     |          |

| $\rho_{n(I/f)}$   | Output Noise Density | f = 120Hz                                                              | 0.8             |                            |     | μV       |

| e <sub>n</sub>    | Output Noise Voltage | $BW = 10Hz - 100kHz$ $V_{OUT} = 2.5V$                                  | 150             |                            |     | μV (rms) |

|                   |                      | BW = $300Hz - 300kHz$<br>V <sub>OUT</sub> = $2.5V$                     | 100             |                            |     |          |

**Note 1:** Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and test conditions, see Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: At elevated temperatures, devices must be derated based on package thermal resistance. The devices in TO220 package must be derated at  $\theta_{jA} = 50^{\circ}\text{C/W}$  (with  $0.5\text{in}^2$ , 1oz. copper area), junction-to-ambient (with no heat sink). The devices in the TO263 surface-mount package must be derated at  $\theta_{jA} = 60^{\circ}\text{C/W}$  (with  $0.5\text{in}^2$ , 1oz. copper area), junction-to-ambient. The SOT-223 package must be derated at  $\theta_{jA} = 90^{\circ}\text{C/W}$  (with  $0.5\text{in}^2$ , 1oz. copper area), junction-to-ambient.

- Note 3: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

- Note 4: Typical numbers are at 25°C and represent the most likely parametric norm.

- Note 5: Limits are guaranteed by testing, design, or statistical correlation.

- Note 6: If used in a dual-supply system where the regulator load is returned to a negative supply, the output must be diode-clamped to ground.

- **Note 7:** The output PMOS structure contains a diode between the V<sub>IN</sub> and V<sub>OUT</sub> terminals. This diode is normally reverse biased. This diode will get forward biased if the voltage at the output terminal is forced to be higher than the voltage at the input terminal. This diode can typically withstand 200mA of DC current and 1Amp of peak current.

- **Note 8:** Output voltage line regulation is defined as the change in output voltage from the nominal value due to change in the input line voltage. Output voltage load regulation is defined as the change in output voltage from the nominal value due to change in load current.

- **Note 9:** Dropout voltage is defined as the minimum input to output differential voltage at which the output drops 2% below the nominal value. Dropout voltage specification applies only to output voltages of 2.5V and above. For output voltages below 2.5V, the drop-out voltage is nothing but the input to output differential, since the minimum input voltage is 2.5V.

- Note 10: The minimum operating value for  $V_{IN}$  is equal to either  $[V_{OUT(NOM)} + V_{DROPOUT}]$  or 2.5V, whichever is greater.

# $\begin{tabular}{ll} \textbf{Typical Performance Characteristics} & \textbf{Unless ohterwise specified: } \textbf{T}_{J} = 25^{\circ} \textbf{C}, \ \textbf{C}_{OUT} = 10 \mu \textbf{F}, \\ \textbf{C}_{IN} = 10 \mu \textbf{F}, \ \textbf{S/D pin is tied to } \textbf{V}_{IN}, \ \textbf{V}_{OUT} = 2.5 \textbf{V}, \ \textbf{V}_{IN} = \textbf{V}_{O(NOM)} + 1 \textbf{V}, \ \textbf{I}_{L} = 10 \ \text{mA} \\ \end{tabular}$

#### **Dropout Voltage vs Output Load Current**

# Ground Current vs Output Voltage $I_L = 0.8A$

2007 104

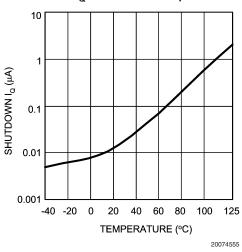

#### Shutdown $I_Q$ vs Junction Temperature

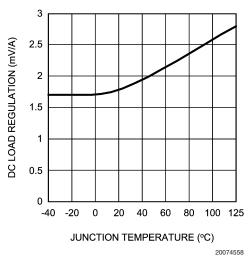

#### DC Load Reg. vs Junction Temperature

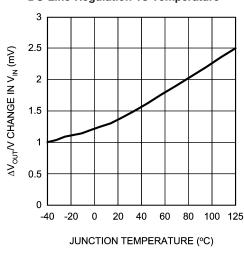

#### **DC Line Regulation vs Temperature**

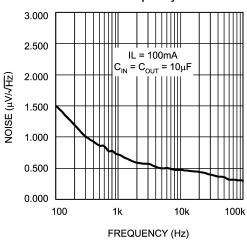

Noise vs Frequency

20074561

# $\begin{tabular}{ll} \textbf{Typical Performance Characteristics} & \textbf{Unless ohterwise specified:} & \textbf{T}_J = 25 ^{\circ} \textbf{C}, & \textbf{C}_{OUT} = 10 \mu \textbf{F}, \\ \textbf{C}_{IN} = 10 \mu \textbf{F}, & \textbf{S/D pin is tied to V}_{IN}, & \textbf{V}_{OUT} = 2.5 \textbf{V}, & \textbf{V}_{IN} = \textbf{V}_{O(NOM)} + 1 \textbf{V}, & \textbf{I}_L = 10 \text{ mA} \\ \end{tabular}$

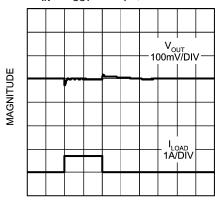

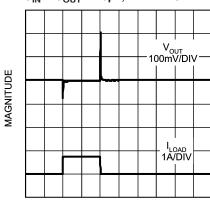

TIME (50µs/DIV)

20074576

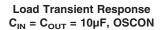

# Load Transient Response

TIME (50µs/DIV)

20074578

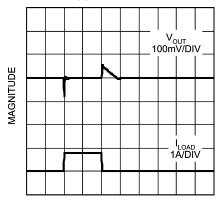

# Load Transient Response $C_{IN} = C_{OUT} = 100 \mu F$ , TANTALUM

TIME (50µs/DIV)

20074580

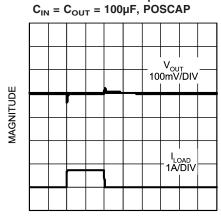

# Load Transient Response $C_{IN} = C_{OUT} = 100 \mu F$ , OSCON

TIME (50µs/DIV)

20074577

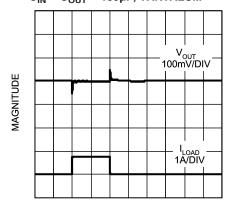

# Load Transient Response $C_{IN} = C_{OUT} = 10\mu F$ , TANTALUM

TIME (50µs/DIV)

20074579

### **Application Hints**

#### SETTING THE OUTPUT VOLTAGE

The output voltage is set using the resistors R1 and R2 (see Typical Application Circuit). The output is also dependent on the reference voltage (typically 1.216V) which is measured at the ADJ pin. The output voltage is given by the equation:

$$V_{OUT} = V_{ADJ} x (1 + R1 / R2)$$

This equation does not include errors due to the bias current flowing in the ADJ pin which is typically about 10 nA. This error term is negligible for most applications. If R1 is >  $100 \mathrm{k}\Omega$  , a small error may be introduced by the ADJ bias current.

The tolerance of the external resistors used contributes a significant error to the output voltage accuracy, with 1% resistors typically adding a total error of approximately 1.4% to the output voltage (this error is in addition to the tolerance of the reference voltage at  $V_{\rm AD,I}$ ).

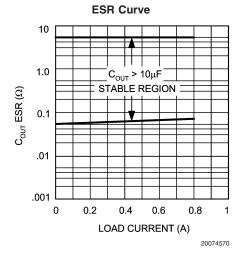

#### **EXTERNAL CAPACITORS**

Like any low-dropout regulator, external capacitors are required to assure stability. These capacitors must be correctly selected for proper performance.

**INPUT CAPACITOR:** An input capacitor of at least  $10\mu F$  is required. Ceramic, Tantalum, or Electrolytic capacitors may be used, and capacitance may be increased without limit.

**OUTPUT CAPACITOR:** An output capacitor is required for loop stability. It must be located less than 1 cm from the device and connected directly to the output and ground pins using traces which have no other currents flowing through them (see PCB Layout section).

The minimum value of output capacitance that can be used for stable full-load operation is  $10\mu F$ , but it may be increased without limit. The output capacitor must have an ESR value as shown in the stable region of the curve (below). Tantalum capacitors are recommended for the output capacitor.

#### **C<sub>FF</sub>** (Feed Forward Capacitor)

The capacitor  $C_{FF}$  is required to add phase lead and help improve loop compensation. The correct amount of capacitance depends on the value selected for R1 (see Typical Application Circuit). The capacitor should be selected such that the zero frequency as given by the equation shown below is approximately 45 kHz:

$$Fz = 45,000 = 1 / (2 \times \pi \times R1 \times C_{EE})$$

A good quality ceramic with X5R or X7R dielectric should be used for this capacitor.

#### **SELECTING A CAPACITOR**

It is important to note that capacitance tolerance and variation with temperature must be taken into consideration when selecting a capacitor so that the minimum required amount of capacitance is provided over the full operating temperature range. In general, a good Tantalum capacitor will show very little capacitance variation with temperature, but a ceramic may not be as good (depending on dielectric type). Aluminum electrolytics also typically have large temperature variation of capacitance value.

Equally important to consider is a capacitor's ESR change with temperature: this is not an issue with ceramics, as their ESR is extremely low. However, it is very important in Tantalum and aluminum electrolytic capacitors. Both show increasing ESR at colder temperatures, but the increase in aluminum electrolytic capacitors is so severe they may not be feasible for some applications (see Capacitor Characteristics Section).

#### **CAPACITOR CHARACTERISTICS**

**CERAMIC:** For values of capacitance in the 10 to 100  $\mu$ F range, ceramics are usually larger and more costly than tantalums but give superior AC performance for bypassing high frequency noise because of very low ESR (typically less than 10 m $\Omega$ ). However, some dielectric types do not have good capacitance characteristics as a function of voltage and temperature.

Z5U and Y5V dielectric ceramics have capacitance that drops severely with applied voltage. A typical Z5U or Y5V capacitor can lose 60% of its rated capacitance with half of the rated voltage applied to it. The Z5U and Y5V also exhibit a severe temperature effect, losing more than 50% of nominal capacitance at high and low limits of the temperature range.

X7R and X5R dielectric ceramic capacitors are strongly recommended if ceramics are used, as they typically maintain a capacitance range within ±20% of nominal over full operating ratings of temperature and voltage. Of course, they are typically larger and more costly than Z5U/Y5U types for a given voltage and capacitance.

**TANTALUM:** Solid Tantalum capacitors are recommended for use on the output because their typical ESR is very close to the ideal value required for loop compensation. They also work well as input capacitors if selected to meet the ESR requirements previously listed.

Tantalums also have good temperature stability: a good quality Tantalum will typically show a capacitance value that varies less than 10-15% across the full temperature range of 125°C to -40°C. ESR will vary only about 2X going from the high to low temperature limits.

The increasing ESR at lower temperatures can cause oscillations when marginal quality capacitors are used (if the ESR of the capacitor is near the upper limit of the stability range at room temperature).

**ALUMINUM:** This capacitor type offers the most capacitance for the money. The disadvantages are that they are larger in physical size, not widely available in surface mount, and have poor AC performance (especially at higher frequencies) due to higher ESR and ESL.

#### **Application Hints** (Continued)

Compared by size, the ESR of an aluminum electrolytic is higher than either Tantalum or ceramic, and it also varies greatly with temperature. A typical aluminum electrolytic can exhibit an ESR increase of as much as 50X when going from  $25^{\circ}\text{C}$  down to  $-40^{\circ}\text{C}$ .

It should also be noted that many aluminum electrolytics only specify impedance at a frequency of 120 Hz, which indicates they have poor high frequency performance. Only aluminum electrolytics that have an impedance specified at a higher frequency (between 20 kHz and 100 kHz) should be used for the LP387X. Derating must be applied to the manufacturer's ESR specification, since it is typically only valid at room temperature.

Any applications using aluminum electrolytics should be thoroughly tested at the lowest ambient operating temperature where ESR is maximum.

#### **PCB LAYOUT**

Good PC layout practices must be used or instability can be induced because of ground loops and voltage drops. The input and output capacitors must be directly connected to the input, output, and ground pins of the LP387X using traces which do not have other currents flowing in them (Kelvin connect).

The best way to do this is to lay out  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  near the device with short traces to the  $V_{\text{IN}}$ ,  $V_{\text{OUT}}$ , and ground pins. The regulator ground pin should be connected to the external circuit ground so that the regulator and its capacitors have a "single point ground".

It should be noted that stability problems have been seen in applications where "vias" to an internal ground plane were used at the ground points of the IC and the input and output capacitors. This was caused by varying ground potentials at these nodes resulting from current flowing through the ground plane. Using a single point ground technique for the regulator and it's capacitors fixed the problem.

Since high current flows through the traces going into  $V_{\rm IN}$  and coming from  $V_{\rm OUT}$ , Kelvin connect the capacitor leads to these pins so there is no voltage drop in series with the input and output capacitors.

#### **RFI/EMI SUSCEPTIBILITY**

RFI (radio frequency interference) and EMI (electromagnetic interference) can degrade any integrated circuit's performance because of the small dimensions of the geometries inside the device. In applications where circuit sources are present which generate signals with significant high frequency energy content (> 1 MHz), care must be taken to ensure that this does not affect the IC regulator.

If RFI/EMI noise is present on the input side of the regulator (such as applications where the input source comes from the output of a switching regulator), good ceramic bypass capacitors must be used at the input pin of the IC.

If a load is connected to the IC output which switches at high speed (such as a clock), the high-frequency current pulses required by the load must be supplied by the capacitors on the IC output. Since the bandwidth of the regulator loop is less than 100 kHz, the control circuitry cannot respond to load changes above that frequency. The means the effective output impedance of the IC at frequencies above 100 kHz is determined only by the output capacitor(s).

In applications where the load is switching at high speed, the output of the IC may need RF isolation from the load. It is

recommended that some inductance be placed between the output capacitor and the load, and good RF bypass capacitors be placed directly across the load.

PCB layout is also critical in high noise environments, since RFI/EMI is easily radiated directly into PC traces. Noisy circuitry should be isolated from "clean" circuits where possible, and grounded through a separate path. At MHz frequencies, ground planes begin to look inductive and RFI/EMI can cause ground bounce across the ground plane.

In multi-layer PCB applications, care should be taken in layout so that noisy power and ground planes do not radiate directly into adjacent layers which carry analog power and ground.

#### **OUTPUT NOISE**

Noise is specified in two ways-

**Spot Noise** or **Output noise density** is the RMS sum of all noise sources, measured at the regulator output, at a specific frequency (measured with a 1Hz bandwidth). This type of noise is usually plotted on a curve as a function of frequency.

**Total output Noise** or **Broad-band noise** is the RMS sum of spot noise over a specified bandwidth, usually several decades of frequencies.

Attention should be paid to the units of measurement. Spot noise is measured in units  $\mu V/\sqrt{Hz}$  or  $nV/\sqrt{Hz}$  and total output noise is measured in  $\mu V(rms)$ .

The primary source of noise in low-dropout regulators is the internal reference. In CMOS regulators, noise has a low frequency component and a high frequency component, which depend strongly on the silicon area and quiescent current. Noise can be reduced in two ways: by increasing the transistor area or by increasing the current drawn by the internal reference. Increasing the area will decrease the chance of fitting the die into a smaller package. Increasing the current drawn by the internal reference increases the total supply current (ground pin current). Using an optimized trade-off of ground pin current and die size, LP3871/LP3874 achieves low noise performance and low quiescent current operation.

The total output noise specification for LP3871/LP3874 is presented in the Electrical Characteristics table. The Output noise density at different frequencies is represented by a curve under typical performance characteristics.

#### SHORT-CIRCUIT PROTECTION

The LP3874-ADJ is short circuit protected and in the event of a peak over-current condition, the short-circuit control loop will rapidly drive the output PMOS pass element off. Once the power pass element shuts down, the control loop will rapidly cycle the output on and off until the average power dissipation causes the thermal shutdown circuit to respond to servo the on/off cycling to a lower frequency. Please refer to the section on thermal information for power dissipation calculations.

#### SHUTDOWN OPERATION

A CMOS Logic level signal at the shutdown ( $\overline{SD}$ ) pin will turn-off the regulator. Pin  $\overline{SD}$  must be actively terminated through a 10k $\Omega$  pull-up resistor for a proper operation. If this pin is driven from a source that actively pulls high and low (such as a CMOS rail to rail comparator), the pull-up resistor is not required. This pin must be tied to Vin if not used.

## Application Hints (Continued)

#### DROPOUT VOLTAGE

The dropout voltage of a regulator is defined as the minimum input-to-output differential required to stay within 2% of the nominal output voltage. For CMOS LDOs, the dropout voltage is the product of the load current and the Rds(on) of the internal MOSFET.

#### **REVERSE CURRENT PATH**

The internal MOSFET in LP3874-ADJ has an inherent parasitic diode. During normal operation, the input voltage is higher than the output voltage and the parasitic diode is reverse biased. However, if the output is pulled above the input in an application, then current flows from the output to the input as the parasitic diode gets forward biased. The output can be pulled above the input as long as the current in the parasitic diode is limited to 200mA continuous and 1A peak.

#### POWER DISSIPATION/HEATSINKING

The LP3874-ADJ can deliver a continuous current of 0.8A over the full operating temperature range. A heatsink may be required depending on the maximum power dissipation and maximum ambient temperature of the application. Under all possible conditions, the junction temperature must be within the range specified under operating conditions. The total power dissipation of the device is given by:

$$P_D = (V_{IN} - V_{OUT})I_{OUT} + (V_{IN})I_{GND}$$

where  $I_{\text{GND}}$  is the operating ground current of the device (specified under Electrical Characteristics).

The maximum allowable temperature rise  $(T_{Rmax})$  depends on the maximum ambient temperature  $(T_{Amax})$  of the application, and the maximum allowable junction temperature  $(T_{Jmax})$ :

$$T_{Rmax} = T_{Jmax} - T_{Amax}$$

The maximum allowable value for junction to ambient Thermal Resistance,  $\theta_{\text{JA}},$  can be calculated using the formula:

$$\theta_{JA} = T_{Rmax} / P_{D}$$

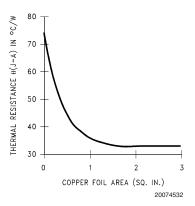

The LP3874-ADJ is available in TO-220 and TO-263 packages. The thermal resistance depends on amount of copper area or heat sink, and on air flow. If the maximum allowable value of  $\theta_{JA}$  calculated above is  $\geq$  60 °C/W for TO-220 package and  $\geq$  60 °C/W for TO-263 package no heatsink is needed since the package can dissipate enough heat to satisfy these requirements. If the value for allowable  $\theta_{JA}$  falls below these limits, a heat sink is required.

#### **HEATSINKING TO-220 PACKAGE**

The thermal resistance of a TO220 package can be reduced by attaching it to a heat sink or a copper plane on a PC board. If a copper plane is to be used, the values of  $\theta_{\text{JA}}$  will be same as shown in next section for TO263 package.

The heatsink to be used in the application should have a heatsink to ambient thermal resistance,

$$\theta_{HA} \le \theta_{JA} - \theta_{CH} - \theta_{JC}$$

.

In this equation,  $\theta_{CH}$  is the thermal resistance from the case to the surface of the heat sink and  $\theta_{JC}$  is the thermal resistance from the junction to the surface of the case.  $\theta_{JC}$  is about 3°C/W for a TO220 package. The value for  $\theta_{CH}$  depends on method of attachment, insulator, etc.  $\theta_{CH}$  varies between 1.5°C/W to 2.5°C/W. If the exact value is unknown, 2°C/W can be assumed.

#### **HEATSINKING TO-263 PACKAGE**

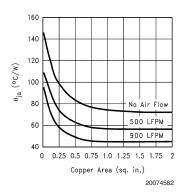

The TO-263 package uses the copper plane on the PCB as a heatsink. The tab of these packages are soldered to the copper plane for heat sinking. *Figure 1* shows a curve for the  $\theta_{JA}$  of TO-263 package for different copper area sizes, using a typical PCB with 1 ounce copper and no solder mask over the copper area for heat sinking.

FIGURE 1.  $\theta_{JA}$  vs Copper (1 Ounce) Area for TO-263 package

As shown in the figure, increasing the copper area beyond 1 square inch produces very little improvement. The minimum value for  $\theta_{JA}$  for the TO-263 package mounted to a PCB is  $32^{\circ}\text{C/W}$

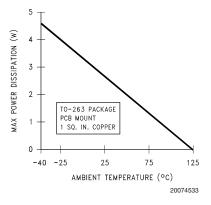

Figure 2 shows the maximum allowable power dissipation for TO-263 packages for different ambient temperatures, assuming  $\theta_{\rm JA}$  is 35°C/W and the maximum junction temperature is 125°C.

FIGURE 2. Maximum power dissipation vs ambient temperature for TO-263 package

#### **HEATSINKING SOT223-5 PACKAGE**

Figure 3 shows a curve for the  $\theta_{JA}$  of SOT-223 package for different copper area sizes, using a typical PCB with 1 ounce copper and no solder mask over the copper area for heat sinking.

# Application Hints (Continued)

FIGURE 3.  $\theta_{\text{JA}}$  vs Copper(1 Ounce) Area for SOT-223 package

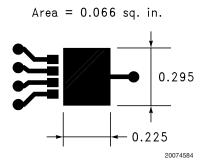

The following figures show different layout scenarios for SOT-223 package.

Area = 0.0078 sq. in.

FIGURE 4. SCENARIO A,  $\theta_{JA}$  = 148°C/W

FIGURE 5. SCENARIO B,  $\theta_{JA}$  = 125°C/W

# Physical Dimensions inches (millimeters) unless otherwise noted

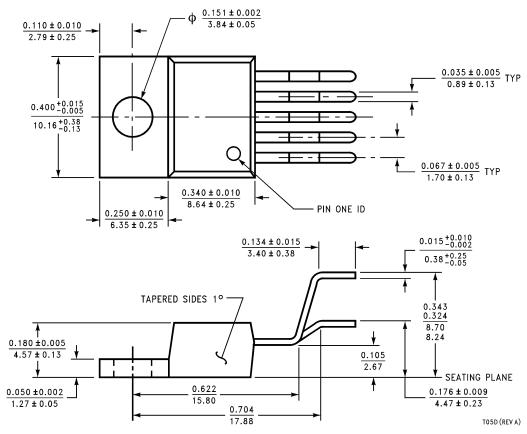

TO220 5-lead, Molded, Stagger Bend Package (TO220-5)

NS Package Number T05D

For Order Numbers, refer to the "Ordering Information" section of this document.

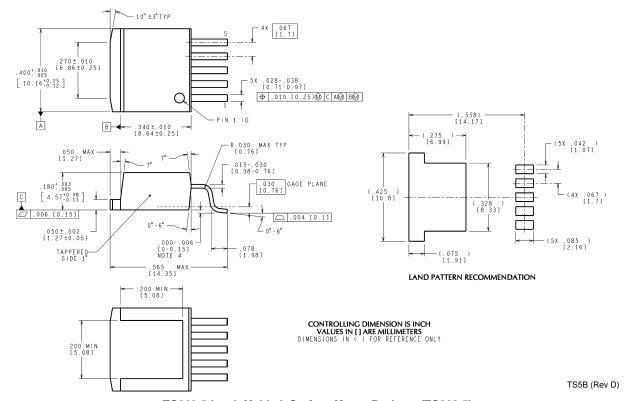

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

TO263 5-Lead, Molded, Surface Mount Package (TO263-5)

NS Package Number TS5B

For Order Numbers, refer to the "Ordering Information" section of this document.

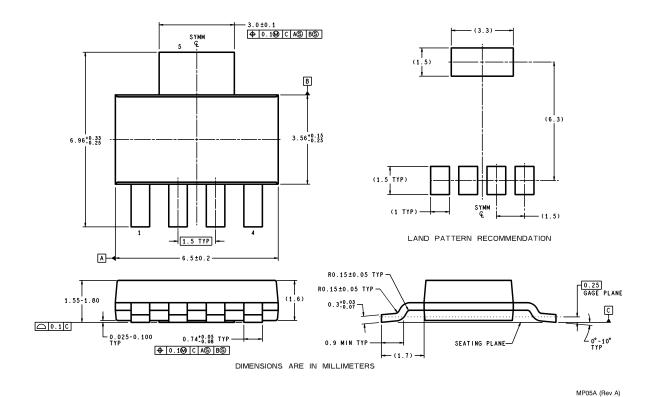

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

SOT223, 5-Lead, Molded, Surface Mount Package (SOT223-5)

NS Package Number MP05A

For Order Numbers, refer to the "Ordering Information" section of this document.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Empily ourope cusport ® pec see

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560