SiI9385, SiI9387, and SiI9389 Port Processor

Data Brief

Document # SiI-DB-1072-A02

September 2010

#### **Copyright Notice**

Copyright © 2009-2010 Silicon Image, Inc. All rights reserved. These materials contain proprietary and confidential information (including trade secrets, copyright, and other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/or services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

### **Trademark Acknowledgment**

Silicon Image<sup>TM</sup>, VastLane<sup>TM</sup>, SteelVine<sup>TM</sup>, PinnaClear<sup>TM</sup>, Simplay<sup>TM</sup>, Simplay HD<sup>TM</sup>, Satalink<sup>TM</sup>, InstaPort<sup>TM</sup>, and TMDS<sup>TM</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI<sup>®</sup>, the HDMI logo and High-Definition Multimedia Interface<sup>TM</sup> are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. x.v.Color<sup>TM</sup> is a trademark of Sony Corporation.

#### **Export Controlled Document**

This document contains information subject to the Export Administration Regulations (EAR) and has a classification of EAR99 or is controlled for Anti-Terrorism (AT) purposes. Transfer of this information by any means to an EAR Country Group E:1 or foreign national thereof (whether in the U.S. or abroad) may require an export license or other approval from the U.S. Department of Commerce. For more information, contact the Silicon Image Director of Global Trade Compliance.

#### **Further Information**

To request other materials, detailed hardware and software guides, and additional information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at <a href="www.siliconimage.com">www.siliconimage.com</a>. Information about obtaining licenses required for using HDMI and HDCP technologies is available from <a href="www.hdmi.org">www.hdmi.org</a> and <a href="www.digital-cp.com">www.digital-cp.com</a>.

© 2009-2010 Silicon Image, Inc. All rights reserved.

# **General Description**

The SiI9385, SiI9387, and SiI9389 Port Processor is the second generation HDMI® port processor with HDMI Ethernet and Audio-return Channel (HEAC) support on one input port. They provide a simple, low-cost method of retransmitting protected digital audio, video, Mobile HD signals, and Ethernet, giving manufacturers a low-cost method of adding an HEAC-capable port to the latest digital TVs. Backward compatibility allows HEAC systems to connect to any existing HDMI and DVI 1.0 source.

These parts support the Audio return Channel (ARC) described in the HDMI 1.4 Specification, which provides an S/PDIF link from an HDMI sink to an HDMI source in the opposite direction of the TMDS<sup>TM</sup> data flow.

The SiI9387/SiI9389 device supports the HDMI Ethernet Channel (HEC) described in the HDMI 1.4 Specification. The HEC feature adds a connection to the HDMI link that is capable of carrying the same data as a full duplex, 100 Mbps Ethernet connection. An HDMI with Ethernet cable used with the SiI9387/SiI9389 device eliminates the need for additional Ethernet cables, allowing for convenient integration of Digital Televisions (DTVs) into the end user's home network system.

The SiI9389 device supports Vendor Specific InfoFrame (VSIF) extraction, which allows the host system to receive information about the 3D video mode being passed-through.

### **Features**

- Audio Return Channel that allows an S/PDIF uplink from HDMI sink device to an HDMI source available in one receiver port

- InstaPort<sup>TM</sup> viewing technology that reduces port switching time to less than one second

- Adaptive equalizer provides long cable support, even at Deep Color resolutions

Standby power modes and built-in regulator meets Energy Star and other power saving requirements, lowers system cost, and optimizes board design

## **HDMI Inputs and Output**

- Five HDMI input ports and single output port

- HDMI, HDCP, and DVI compatibility

- TMDS cores run at 2.25 Gbps

- Supports video resolutions up to 1080p, 60 Hz, 12-bit or 720p/1080i, 120 Hz, 12-bit

- Supports all the mandatory and several optional 3D formats described in the HDMI 1.4 Specification

- Mobile HD support for 1080i @ 60 Hz on two ports

- Pre-programmed with HDCP keys

- HDMI Ethernet Channel support for one receive port (SiI9387/SiI9389 device only)

- Repeater function supports up to 127 devices (SiI9387/SiI9389 device only)

- Vendor Specific InfoFrame (VSIF) extraction to support 3D video (SiI9389 only)

## **Control Capability**

- Consumer Electronics Control (CEC) interface incorporates an HDMI-compliant CEC I/O and an integrated Silicon Image CEC Programming Interface (CPI); these simplify design and lower costs and software overhead

- Integrated EDID and DDC support for the HDMI ports using a 512-byte NVRAM shared between ports that loads into separate 256-byte SRAM for each of 5 HDMI ports and 128-byte SRAM for VGA EDID

- Individual control of Hot Plug Detect (HPD) for each of the ports

- Controllable by the local I<sup>2</sup>C bus

## **Packaging**

• 100-pin, 14 mm x 14 mm, 0.5 mm pitch TQFP package with enhanced ePad<sup>TM</sup>

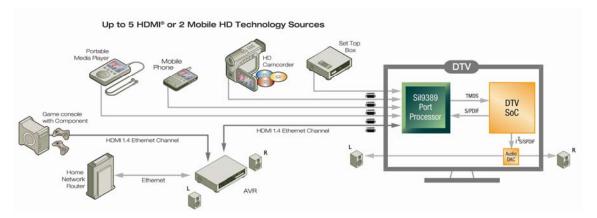

**Figure 1. Port Processor Application**

## Pin Diagram

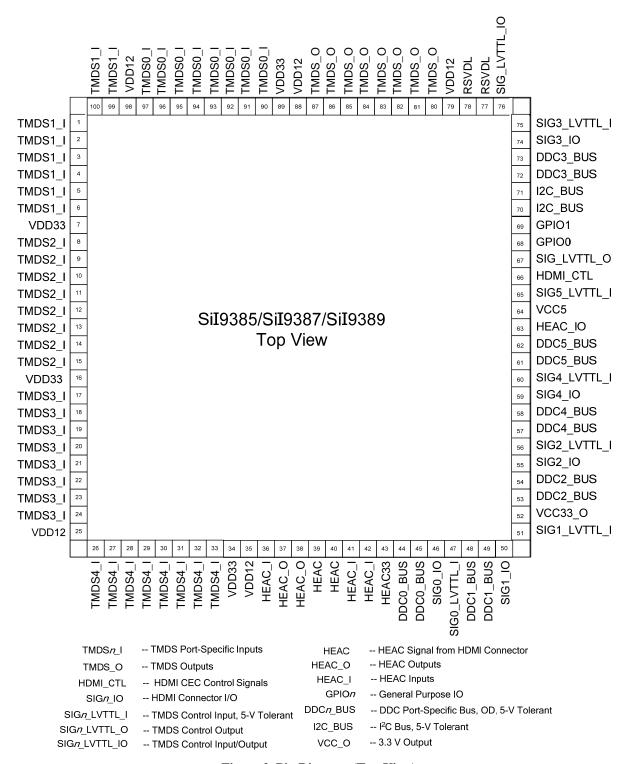

Figure 2 shows the pin assignments of the port processor. The package is a 14 mm x 14 mm 100-pin TQFP with an ePad, which *must* be connected to ground. Pin names are generalized by type for this document. The list below the diagram describes the purpose of each type.

Figure 2. Pin Diagram (Top View)

# **Package Information**

## ePad Requirements

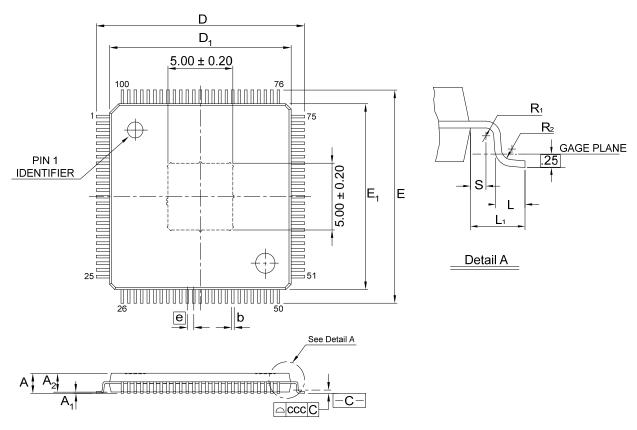

The SiI9385, SiI9387, and SiI9389 Port Processor chip is packaged in a 100-pin, 14 mm x 14mm TQFP package with an ExposedPad<sup>TM</sup> (ePad<sup>TM</sup>) that is used both for the electrical connectivity ground of the device and for improved thermal transfer characteristics. The ePad dimensions are 5 mm x 5 mm  $\pm \pm /-0.15$  mm. Soldering of the ePad to the ground plane of the PCB is **required** to meet package power dissipation requirements at full speed operation, and to correctly connect the chip circuitry to electrical ground.

**Note:** The ePad **must** be soldered to an electrically grounded plane on the PCB. A clearance of at least 0.25 mm should be designed on the PCB between the edge of the ePad and the inner edges of the lead pads to avoid the possibility of electrical shorts.

The thermal land area on the PCB may use thermal vias to improve heat removal from the package. These thermal vias also double as the ground connections of the chip and must attach internally in the PCB to the ground plane. An array of vias should be designed into the PCB beneath the package. For optimum thermal performance, the via diameter should be 12 mils to 13 mils (0.30 mm to 0.33 mm) and the via barrel should be plated with 1-ounce copper to plug the via. This design helps to avoid any solder wicking inside the via during the soldering process, which may result in voids in solder between the pad and the thermal land. If the copper plating does not plug the vias, the thermal vias can be tented with solder mask on the top surface of the PCB to avoid solder wicking inside the via during assembly. The solder mask diameter should be at least 4 mils (0.1 mm) larger than the via diameter.

Package stand-off when mounting the device also needs to be considered. For a nominal stand-off of approximately 0.1 mm the stencil thickness of 5 mils to 8 mils should provide a good solder joint between the ePad and the thermal land.

Figure 3 shows the package dimensions of the SiI9385/SiI9387/SiI9389 port processor.

## **Package Dimensions**

These drawings are not to scale.

Figure 3. Package Diagram

JEDEC Package Code MS-026

| Item  | Description    | Min       | Тур  | Max  |

|-------|----------------|-----------|------|------|

| A     | Thickness      |           |      | 1.20 |

| A1    | Stand-off      | 0.05      | _    | 0.15 |

| A2    | Body thickness | 0.95      | 1.00 | 1.05 |

| D     | Footprint      | 16.00 BSC |      |      |

| E     | Footprint      | 16.00 BSC |      |      |

| $D_1$ | Body size      | 14.00 BSC |      |      |

| $E_1$ | Body size      | 14.00 BSC |      |      |

| b     | Lead width     | 0.17      | 0.22 | 0.27 |

| Item  | Description          | Min      | Typ  | Max  |

|-------|----------------------|----------|------|------|

| C     | Lead thickness       | 0.09     |      | 0.20 |

| e     | Lead pitch           | 0.50 BSC |      |      |

| L     | Lead foot length     | 0.45     | 0.60 | 0.75 |

| $L_1$ | Total lead length    | 1.00 REF |      |      |

| $R_1$ | Lead radius, inside  | 0.08     |      |      |

| $R_2$ | Lead radius, outside | 0.08     |      | 0.20 |

| S     | Lead horizontal run  | 0.20     |      |      |

| ccc   | Lead coplanarity     | 0.08     |      |      |

## **Marking Specification**

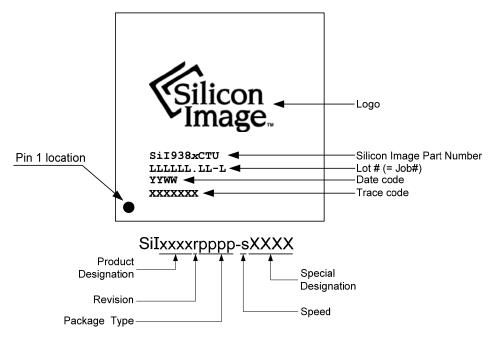

Figure 4 shows the markings of the SiI9385/SiI9387/SiI9389 package. This drawing is not to scale.

Figure 4. Marking Diagram

## **Ordering Information**

**Production Part Numbers:**

| Device                                                     | Part Number |  |

|------------------------------------------------------------|-------------|--|

| Standard port processor with ARC                           | SiI9385CTU  |  |

| Port processor with HEAC and repeater capability           | SiI9387CTU  |  |

| Port processor with HEAC, repeater capability, and 3D VSIF | SiI9389CTU  |  |

#### **Disclaimers**

These materials are provided on an "AS IS" basis. Silicon Image, Inc. and its affiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non-infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or results provided in, or that may be obtained from use of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Silicon Image, Inc. and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update or keep current the information contained in these materials, and expressly disclaims all direct, indirect, special, incidental, consequential, reliance and punitive damages, including WITHOUT LIMITATION any loss of profits arising out of your access to, use or interpretation of, or actions taken or not taken based on the content of these materials.

Silicon Image, Inc. and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

Notwithstanding the foregoing, these materials shall not, in the absence of authorization under U.S. and local law and regulations, as required, be used by or exported or re-exported to (i) any U.S. sanctioned or embargoed country, or to nationals or residents of such countries; or (ii) any person, entity, organization or other party identified on the U.S. Department of Commerce's Denied Persons or Entity List, the U.S. Department of Treasury's Specially Designated Nationals or Blocked Persons List, or the Department of State's Debarred Parties List, as published and revised from time to time; (iii) any party engaged in nuclear, chemical/biological weapons or missile proliferation activities; or (iv) any party for use in the design, development, or production of rocket systems or unmanned air vehicles.

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Silicon Image, Inc. and/or its affiliates are provided on as "AS IS" basis, except to the extent that Silicon Image, Inc. and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, SILICON IMAGE, INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY SILICON IMAGE, INC. AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW. DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

1060 E. Arques Avenue Sunnyvale, CA 94085 T 408.616.4000 F 408.830.9530 www.siliconimage.com