# 8-Bit Constant Current LED Driver with LED Error Detection and Run-Time Current Adjustment

### **Features**

- I Compatible with MBI5168 in electrical characteristics and package

- I Exploiting **Share-I-O™** technique to provide two operation modes:

- Normal Mode with the same functionality as MB5168

- Special Mode to detect individual LED errors, like MBI5169 and program output current gain, like MBI5170

- I 8 constant-current output channels

- I Constant output current invariant to load voltage change

- I Constant output current range: 5 -120 mA

- Excellent output current accuracy, between channels: < ±3% (max.), and between ICs: < ±6% (max.)</p>

- I Output current adjusted through an external resistor

- Fast response of output current, OE (min.): 200 ns @I<sub>out</sub>< 60mA

OE (min.): 400 ns @I<sub>out</sub>= 60~100mA

- I 25MHz clock frequency

- I Schmitt trigger input

- I 3.3~ 5V supply voltage

- 1 256-step run-time programmable output current gain suitable for white balance application

| Current /        | Conditions  |                                     |  |

|------------------|-------------|-------------------------------------|--|

| Between Channels | Between ICs | - Conditions                        |  |

| . 120/           | . 160/      | $I_{OUT} = 10 \sim 100 \text{ mA},$ |  |

| < ±3%            | < ±6%       | $V_{DS} = 0.8V, V_{DD} = 5.0V$      |  |

### **Product Description**

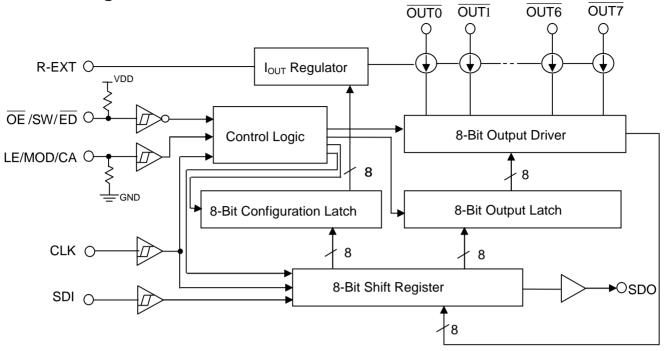

MBI5171 succeeds MBI5168 and also exploits **PrecisionDrive™** technology to enhance its output characteristics. Furthermore, MBI5171 uses the idea of **Share-I-O™** technology to make MBI5171 backward compatible with MBI5168 in both package and electrical characteristics and extend its functionality for LED load Error Detection and run-time LED current gain control in LED display systems, especially LED traffic sign applications.

MBI5171 contains an 8-bit Shift Register and an 8-bit Output Latch, which convert serial input data into parallel output format. At MBI5171 output stages, eight regulated current ports are designed to provide uniform and constant current sinks with small skew between ports for driving LED's within a wide range of forward voltage (Vf) variations. Users may adjust the output current from 5 mA to 120 mA with an external resistor R<sub>ext</sub>, which gives users flexibility in controlling the light intensity of LED's. MBI5171 guarantees to endure maximum 17V at the output ports. Besides, the high clock frequency up to 25 MHz also satisfies the system requirements of high volume data transmission.

MBI5171 extends its functionality to provide one Special Mode in which two functions are included, Error Detection and Current Gain Control, by means of the **Share-I-O**<sup>TM</sup> technique on pins LE and  $\overline{OE}$ , without any extra pins. Thus, MBI5171 could be a drop-in replacement of MBI5168. The printed circuit board originally designed for MBI5168 may be also applied to MBI5171. In MBI5171 there are two operation modes and three phases: Normal Mode phase, Mode Switching transition phase, and Special Mode phase. The signal on the multiple function pin  $\overline{OE}/SW/\overline{ED}$  would be monitored. Once an one-clock-wide short pulse appears on the pin  $\overline{OE}/SW/\overline{ED}$ , MBI5171 would enter the Mode Switching phase. At this moment, the voltage level on the pin LE/MOD/CA is used for determining the next mode to which MBI5171 is going to switch.

In the Normal Mode phase, MBI5171 has exactly the same functionality with MBI5168. The serial data could be transferred into MBI5171 via the pin SDI, shifted in the Shift Register, and go out via the pin SDO. The LE/MOD/CA can latch the serial data in the Shift Register to the Output Latch.  $\overline{OE}/SW/\overline{ED}$  would enable the output drivers to sink current.

In the Special Mode phase, the low-voltage-level signal  $\overline{OE}$  /SW / $\overline{ED}$  can enable output channels and detect the status of the output current to tell if the driving current level is enough or not. The detected error status would be loaded into the 8-bit Shift Register and be shifted out via the pin SDO along with the signal CLK. Then system controller could read the error status and know whether the LED's are properly lit or not.

On the other hand, in the Special Mode phase MBI5171 also allows users to adjust the output current level by setting a run-time programmable Configuration Code. The code is sent into MBI5171 via the pin SDI. The positive pulse of LE/MOD/CA would latch the code in the Shift Register into a built-in 8-bit Configuration Latch, instead of the Output Latch. The code would affect the voltage at the terminal R-EXT and control the output current regulator. The output current could be adjusted finely by a gain ranging (1/12) to (127/128) in 256 steps. Hence, the current skew between IC's can be compensated within less than 1% and this feature is suitable for white balancing in LED color display panels.

Users can get detailed ideas about how MBI5171 works in the section Operation Principle.

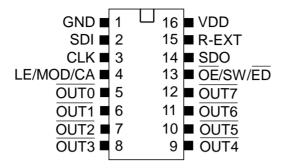

# Pin Assignment

# **Terminal Description**

| Pin No. | Pin Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | GND         | Ground terminal for control logic and current sinks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 2       | SDI         | Serial-data input to the Shift Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 3       | CLK         | Clock input terminal for data shift at the rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4       | LE/MOD/CA   | Output channel data strobe input terminal: in the Normal Mode phase, serial data in the Shift Register is transferred to the respective Output Latch when LE/MOD/CA is high; the data is latched inside the Output Latch when LE/MOD/CA goes low. If the data in the Output Latch is "1" (High), the respective output channel will be enabled after OE/SW/ED is pulled down to low.  Mode selection input terminal: in the Mode Switching phase, LE/MOD/CA couldn't strobe serial data but its level is used for determining the next mode to which MBI5171 is going to switch. When LE/MOD/CA is high, the next mode is the Special Mode; when low, the next mode is the Normal Mode.  Configuration data strobe input terminal: in the Special Mode phase, serial data is latched into the Configuration Latch, instead of the Output Latch in the Normal Mode. The serial data here is regarded as the Configuration Code, which affect the output current level of all channels.(See Operation Principle) |  |  |  |

| 5-12    | OUT0 ~ OUT7 | Constant current output terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 13      | OE/SW/ED    | Output enable terminal: no matter in what phase MBI5171 operates, the signal $\overline{OE}$ /SW / $\overline{ED}$ can always enable output drivers to sink current. When its level is (active) low, the output drivers are enabled; when high, all output drivers are turned OFF (blanked).  Mode switching trigger terminal: an one-clock-wide short pulse signal of $\overline{OE}$ /SW / $\overline{ED}$ could put MBI5171 into the Mode Switching phase.  Error detection enable terminal: in the Special Mode phase, the active low signal $\overline{OE}$ /SW / $\overline{ED}$ can make MBI5171 not just enable output drivers but detect LED load error status. The detected error status would be stored into the Shift Register. (See Operation Principle)                                                                                                                                                                                                                                          |  |  |  |

| 14      | SDO         | Serial-data output to the following SDI of the next driver IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 15      | R-EXT       | Input terminal used for connecting an external resistor in order to set up the current level of all output ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 16      | VDD         | Supply voltage terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

# MBI5171

In MBI5171, the relationship between the functions of pins 4 and 13 and the operation phases are listed below:

| Pin<br>No. | Pin Name  | Function                                                                 | Normal<br>Mode | Mode<br>Switching | Special<br>Mode |

|------------|-----------|--------------------------------------------------------------------------|----------------|-------------------|-----------------|

|            |           | LE: latching serial data into the Output Latch                           | Yes            | No                | No              |

| 4          | LE/MOD/CA | MOD: mode selection                                                      | No             | Yes               | No              |

|            |           | CA: latching serial data into the Configuration Latch                    | No             | No                | Yes             |

|            |           | OE: enabling the current output drivers                                  | Yes            | Yes               | Yes             |

| 13         | OE/SW/ED  | SW: entering the Mode Switching phase                                    | Yes            | Yes               | Yes             |

|            |           | ED: enabling error detection and storing results into the Shift Register | No             | No                | Yes             |

### **Block Diagram**

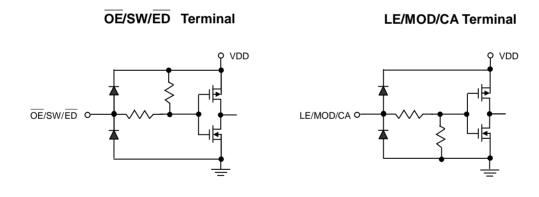

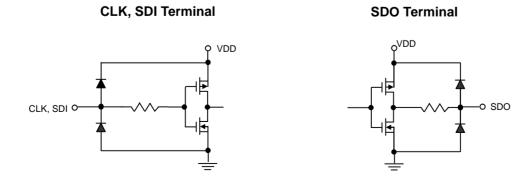

# **Equivalent Circuits of Inputs and Outputs**

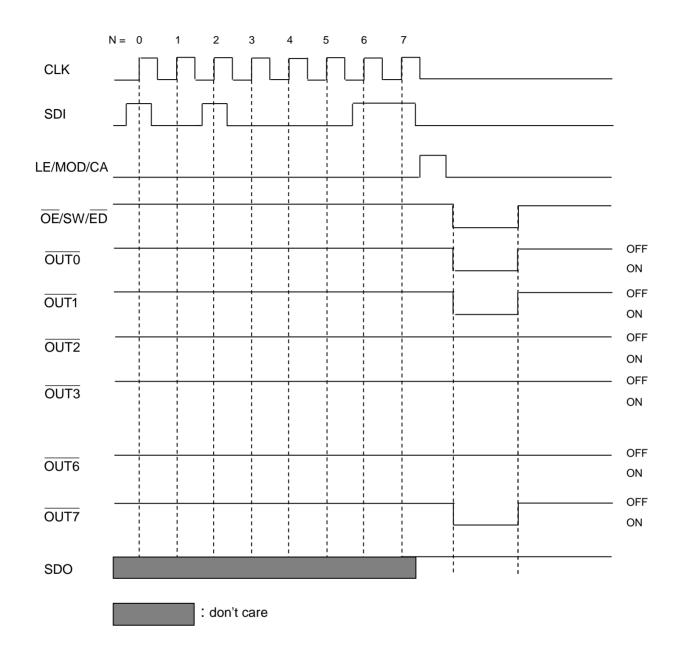

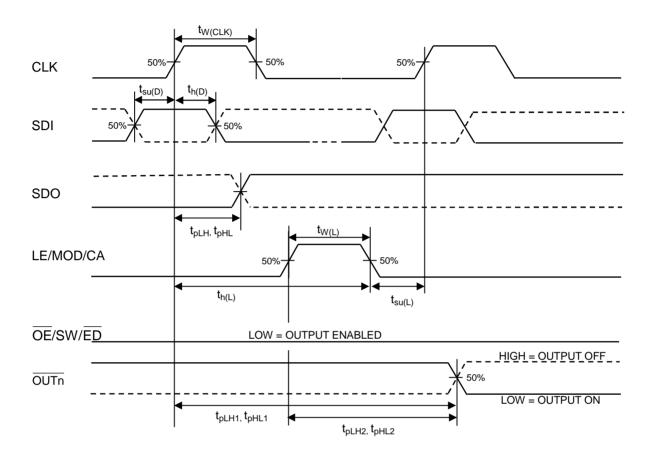

# **Timing Diagram**

### **Normal Mode**

# **Truth Table (In Normal Mode)**

| CLK     | LE/MOD/CA | OE/SW/ED | SDI              | OUT0 OUT5 OUT 7                           | SDO              |

|---------|-----------|----------|------------------|-------------------------------------------|------------------|

|         | Н         | L        | D <sub>n</sub>   | <u>D</u> n <u>D</u> n - 5 <u>D</u> n - 7  | D <sub>n-7</sub> |

| <u></u> | L         | L        | D <sub>n+1</sub> | No Change                                 | D <sub>n-6</sub> |

|         | Н         | L        | D <sub>n+2</sub> | <u>Dn + 2</u> <u>Dn - 3</u> <u>Dn - 5</u> | D <sub>n-5</sub> |

|         | Х         | L        | D <sub>n+3</sub> | <u>Dn+2</u> <u>Dn-3</u> <u>Dn-5</u>       | D <sub>n-5</sub> |

|         | Х         | Н        | D <sub>n+3</sub> | Off                                       | D <sub>n-5</sub> |

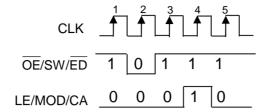

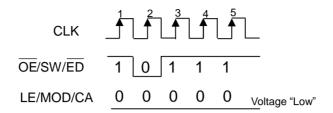

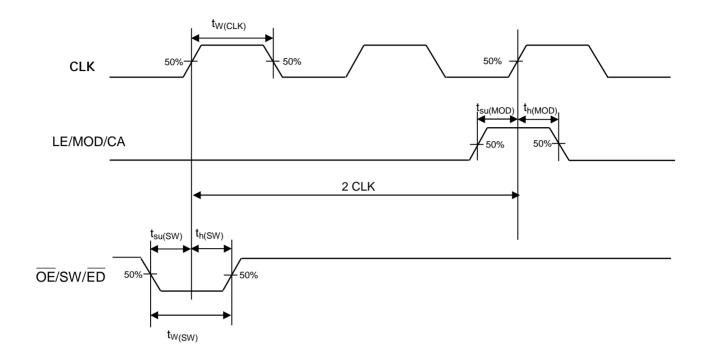

# Switching to Special Mode

The above shows an example of the signal sequence that can set the next operation mode of MBI5171 to be the Special Mode. The LE/MOD/CA active pulse here would not latch any serial data.

### Note:

After entering the Special Mode, MBI5171 can detect LED error and adjust current gain.

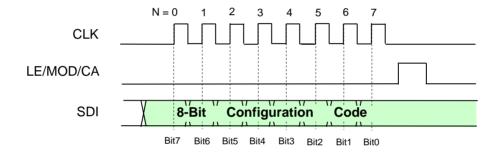

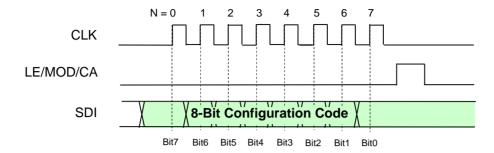

# Writing Configuration Code (In Special Mode)

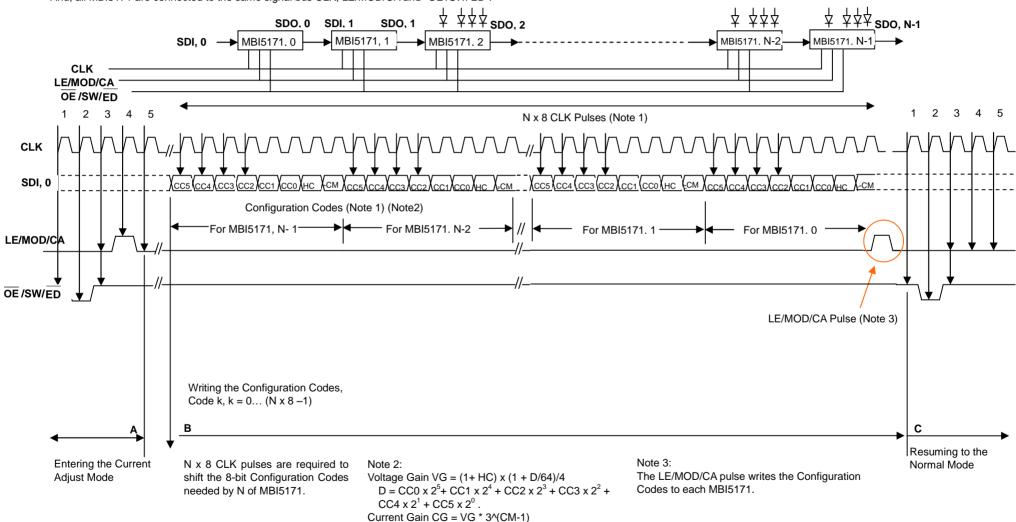

In the Special Mode, by sending the positive pulse of LE/MOD/CA, the content of the Shift Register with a Configuration Code will be written to the 8-bit Configuration Latch.

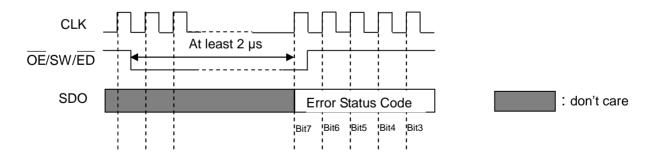

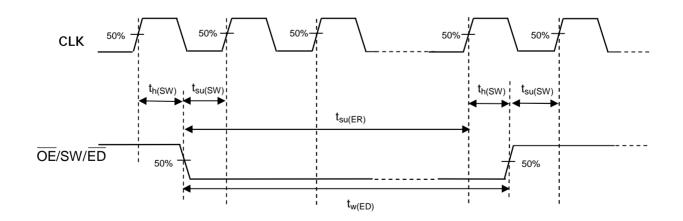

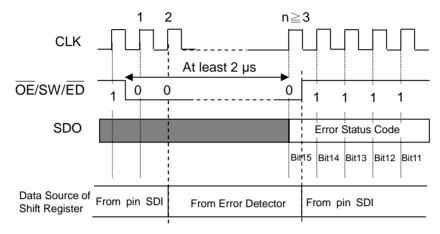

# Reading Error Status Code (In Special Mode)

When MBI5171 is working in the Special Mode, the above signal sequence example can let a system controller read the Error Status codes via the pin SDO.

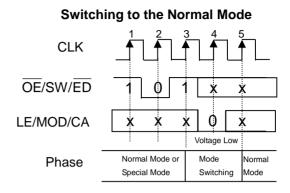

# Switching to Normal Mode

The above signal sequence example can make MBI5171 operate in the Normal Mode.

### Note:

If users want to know the detailed process for each of the above examples, please refer to the contents in **Operation Principle**.

# **Maximum Ratings**

| Characteri            | Symbol     | Rating           | Unit                         |      |

|-----------------------|------------|------------------|------------------------------|------|

| Supply Voltage        |            | $V_{DD}$         | 0 ~ 7.0                      | V    |

| Input Voltage         |            | V <sub>IN</sub>  | -0.4 ~ V <sub>DD</sub> + 0.4 | V    |

| Output Current        |            | I <sub>OUT</sub> | +120                         | mA   |

| Output Voltage        |            | V <sub>DS</sub>  | -0.5 ~ +20                   | V    |

| Clock Frequency       |            | F <sub>CLK</sub> | 25                           | MHz  |

| GND Terminal Current  |            | I <sub>GND</sub> | 1000                         | mA   |

|                       | CN – type  |                  | 2.03                         |      |

| Power Dissipation     | CD – type  | <u></u>          | 1.46                         | w    |

| (On PCB, Ta=25°C)     | CDW – type | $P_D$            | 2.03                         | VV   |

|                       | CP – type  |                  | 1.32                         |      |

|                       | CN – type  |                  | 61.65                        |      |

| Thermal Resistance    | CD – type  |                  | 85.82                        | 9000 |

| (On PCB, Ta=25°C)     | CDW – type | $R_{th(j-a)}$    | 61.63                        | °C/W |

|                       | CP – type  | 1                | 94.91                        |      |

| Operating Temperature |            | T <sub>opr</sub> | -40 ~ +85                    | °C   |

| Storage Temperature   |            | T <sub>stg</sub> | -55 ~ +150                   | °C   |

### **Recommended Operating Conditions**

| Characteristics                                               | Symbol               | Condition                                                                            | Min.        | Тур. | Max.                 | Unit |

|---------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|-------------|------|----------------------|------|

| Supply Voltage                                                | $V_{DD}$             | -                                                                                    | 4.5         | 5.0  | 5.5                  | V    |

| Output Voltage                                                | V <sub>DS</sub>      | OUT0 ~ OUT7                                                                          | -           | -    | 17.0                 | V    |

|                                                               | I <sub>OUT</sub>     | OUT0 ~ OUT7<br>CM*=1, V <sub>DD</sub> =5V                                            | 5           | -    | 120                  | mA   |

| Output Current                                                | I <sub>OUT</sub>     | $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ ,<br>CM*=0, V <sub>DD</sub> =5V | 5           | -    | 40                   | mA   |

|                                                               | I <sub>OH</sub>      | SDO                                                                                  | -           | -    | -1.0                 | mA   |

|                                                               | I <sub>OL</sub>      | SDO                                                                                  | -           | -    | 1.0                  | mA   |

| Input Voltage                                                 | $V_{IH}$             | CLK, OE/SW/ED<br>LE/MOD, and SDI                                                     | $0.7V_{DD}$ | -    | V <sub>DD</sub> +0.3 | V    |

| input voltage                                                 | $V_{IL}$             | CLK, OE/SW/ED ,<br>LE/MOD, and SDI                                                   | -0.3        | -    | 0.3V <sub>DD</sub>   | V    |

| CLK Pulse Width                                               | $t_{w(CLK)}$         |                                                                                      | 20          | -    | -                    | ns   |

| Setup Time for SDI                                            | t <sub>su(D)</sub>   |                                                                                      | 5           | -    | -                    | ns   |

| Hold Time for SDI                                             | t <sub>h(D)</sub>    | _                                                                                    | 10          | -    | -                    | ns   |

| LE/MOD/CA Pulse Width                                         | $t_{w(L)}$           |                                                                                      | 20          | -    | -                    | ns   |

| Setup Time for LE/MOD/CA                                      | t <sub>su(L)</sub>   | For data strobo                                                                      | 5           | -    | -                    | ns   |

| Hold Time for LE/MOD/CA                                       | t <sub>h(L)</sub>    | For data strobe                                                                      | 10          | -    | -                    | ns   |

| Setup Time for LE/MOD/CA                                      | t <sub>su(MOD)</sub> | In Mode Switching                                                                    | 5           | -    | -                    | ns   |

| Hold Time for LE/MOD/CA                                       | t <sub>h(MOD)</sub>  | in wode Switching                                                                    | 10          | -    | -                    | ns   |

|                                                               | $t_{w(SW)}$          | To trigger Mode<br>Switching                                                         | 20          | -    | -                    | ns   |

| OE/SW/ED Pulse Width                                          | $t_{w(OE)}$          | I <sub>out</sub> < 60mA                                                              | 200         | -    | -                    | ns   |

| OE/SW/ED Pulse Width                                          | $t_{\text{w(OE)}}$   | I <sub>out</sub> = 60~100mA                                                          | 400         | -    | -                    | ns   |

|                                                               | $t_{w(ED)}$          | When detecting<br>LED error status                                                   | 2010        | -    | -                    | ns   |

| Setup Time for<br>Correctly-Generated Error<br>Status Code ** | $t_{su(ER)}$         | When detecting<br>LED error status                                                   | 2000        | -    | -                    | ns   |

| Setup Time for OE/SW/ED                                       | t <sub>su(SW)</sub>  | To trigger Mode<br>Switching or when                                                 | 5           | -    | -                    | ns   |

| Hold Time for OE/SW/ED                                        | t <sub>h(SW)</sub>   | detecting LED error status                                                           | 10          | -    | -                    | ns   |

| Clock Frequency                                               | F <sub>CLK</sub>     | Cascade Operation (V <sub>DD</sub> = 5.0V)                                           | -           | -    | 25                   | MHz  |

<sup>\*</sup> CM is one bit in configuration code and called as "Current Multiplier." It would affect the ratio of  $I_{OUT}$  to  $I_{rext}$ . The detail information could be found in the section **Operation Principle**.

<sup>\*\*</sup> In the Error Detection mode, when  $\overline{OE/SW/ED}$  is pulled down to LOW for enabling output drivers and error detection, the output drivers must be enabled for at least 2us so that the error status code could be correctly generated. See **Operation Principle** and **Timing Waveform**.

# Electrical Characteristics(V<sub>DD</sub>= 5.0V)

| Characte                           | Characteristics Symbol Condition |                         | Condition                                                                                             | Min.               | Тур. | Max.        | Unit  |

|------------------------------------|----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------|--------------------|------|-------------|-------|

| Supply Voltag                      | Supply Voltage V <sub>DD</sub> - |                         | -                                                                                                     | 4.5                | 5.0  | 5.5         | V     |

| Output Voltag                      | e                                | V <sub>DS</sub>         | OUT0~ OUT7                                                                                            |                    | -    | 17.0        | V     |

|                                    |                                  | I <sub>OUT</sub>        | Test Circuit for Electrical Characteristics                                                           | 5                  | -    | 120         | mA    |

| Output Curren                      | nt                               | I <sub>OH</sub>         | SDO                                                                                                   | -                  | -    | -1.0        | mA    |

|                                    |                                  | I <sub>OL</sub>         | SDO                                                                                                   | -                  | -    | 1.0         | mA    |

|                                    | "H" level                        | V <sub>IH</sub>         | Ta = -40~85°C                                                                                         | 0.7V <sub>DD</sub> | -    | $V_{DD}$    | V     |

| Input Voltage                      | "L" level                        | V <sub>IL</sub>         | Ta = -40~85°C                                                                                         | GND                | -    | $0.3V_{DD}$ | V     |

| Output Leakag                      | e Current                        |                         | V <sub>DS</sub> =17.0V and channel off                                                                | -                  | -    | 0.5         | μA    |

| 0 (- ()/-                          | 000                              | V <sub>OL</sub>         | I <sub>OL</sub> =+1.0mA                                                                               | -                  | -    | 0.4         | V     |

| Output Voltage                     | SDO                              | V <sub>OH</sub>         | I <sub>OH</sub> =-1.0mA                                                                               | 4.6                | -    | -           | V     |

| Output Current                     | : 1                              | I <sub>OUT1</sub>       | $V_{DS} = 0.5V$ ; $R_{ext} = 744\Omega$ ; $CG^* = 0.992$                                              | -                  | 25.0 | -           | mA    |

| Current Skew (between chan         | nels)                            | dl <sub>OUT1</sub>      | $I_{OUT} = 25$ mA, $V_{DS} \ge 0.5$ V                                                                 | -                  | ±1   | ±3          | %     |

| Output Current                     | 2                                | I <sub>OUT2</sub>       | $V_{DS} = 0.6V$ ; $R_{ext} = 372\Omega$ ; $CG^* = 0.992$                                              |                    | 50.0 | -           | mA    |

| Current Skew<br>(between channels) |                                  | dl <sub>OUT2</sub>      | $I_{OUT} = 50$ mA, $V_{DS} \ge 0.6$ V                                                                 |                    | ±1   | ±3          | %     |

| Output Current 3                   |                                  | I <sub>OUT3</sub>       | $V_{DS} = 0.8V$ ; $R_{ext} = 186\Omega$ ; $CG^* = 0.992$                                              | -                  | 100  | -           | mA    |

| Current Skew<br>(between channels) |                                  | dl <sub>OUT3</sub>      | $I_{OUT} = 100 \text{mA}, V_{DS} \ge 0.8 \text{V}$                                                    |                    | ±1   | ±3          | %     |

| Output Current<br>Output Voltage   | Regulation                       | %/dV <sub>DS</sub>      | V <sub>DS</sub> within 1.0V and 3.0V                                                                  |                    | ±0.1 | -           | % / V |

| Output Current<br>Supply Voltage   |                                  | %/dV <sub>DD</sub>      | V <sub>DD</sub> within 4.5V and 5.5V                                                                  |                    | ±1   | -           | % / V |

| Pull-up Resista                    |                                  |                         | OE/SW/ED                                                                                              | 250                | 500  | 800         | ΚΩ    |

| Pull-down Res                      | istance                          | R <sub>IN</sub> (down)  | LE/MOD/CA                                                                                             | 250                | 500  | 800         | ΚΩ    |

|                                    |                                  | I <sub>out, Th1</sub>   | $R_{\text{ext}}$ =744 $\Omega$ , $CG^* = 0.992$ , $I_{\text{out, target}} = 25\text{mA}$              | -                  | -    | 24.9        | mA    |

| Threshold Curi<br>Error Detection  |                                  | I <sub>out, Th2</sub>   | $R_{\text{ext}}$ =372 $\Omega$ , $CG^* = 0.992$ , $I_{\text{out, target}} = 50\text{mA}$              | -                  | -    | 40          | mA    |

|                                    | •                                | I <sub>out, Th3</sub>   | $R_{ext}$ =186 $\Omega$ , $CG^* = 0.992$ , $I_{out, target} = 100 mA$                                 | -                  | -    | 70          | mA    |

|                                    |                                  | I <sub>DD</sub> (off) 0 | R <sub>ext</sub> =Open, OUT0 ~ OUT7 =Off; CG= 0.992                                                   | -                  | 3.3  | -           |       |

|                                    | "OFF"                            | I <sub>DD</sub> (off) 1 | $R_{\text{ext}}$ =744 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ =Off; CG= 0.992 | -                  | 5.9  | -           |       |

| Supply<br>Current                  | "OFF"                            | I <sub>DD</sub> (off) 2 | $R_{\text{ext}}$ =372 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ =Off; CG= 0.992 | -                  | 8.5  | -           |       |

|                                    |                                  | I <sub>DD</sub> (off) 3 | $R_{\text{ext}}$ =186 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ =Off; CG= 0.992 | -                  | 13.7 | -           | mA    |

|                                    |                                  | I <sub>DD</sub> (on) 1  | $R_{ext}$ =744 $\Omega$ , $\overline{OUT0} \sim \overline{OUT7}$ =On; CG= 0.992                       | -                  | 5.9  | -           |       |

|                                    | "ON"                             | I <sub>DD</sub> (on) 2  | $R_{\text{ext}}$ =372 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ =On; CG= 0.992  | -                  | 8.5  | -           |       |

|                                    |                                  | I <sub>DD</sub> (on) 3  | $R_{\text{ext}}$ =186 $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT7}}$ =On; CG= 0.992  | -                  | 13.7 | -           |       |

### 8-Bit Constant Current LED Driver with LED Error Detection and Run-Time Current Adjustment

### **MBI5171**

- \* In the above table, CG is the programmable current gain. The detail description could be found in the section **Operation Principle**.

- \*\* To effectively detect the load open-circuit error at the output ports, MBI5171 has a built-in current detection circuit. The current detection circuit will detect the effective current  $I_{out, effective}$  and compare it with the threshold current  $I_{out, Th}$ . If  $I_{out, effective}$  is less than the threshold current  $I_{out, Th}$ , an error flag (LOW) will be asserted and stored into the built-in Shift Register. Each combination of external resistor  $R_{ext}$  and CG would determine a target output current  $I_{out, target}$ , which has a corresponding threshold current  $I_{out, Th}$ . To bias LED operation point properly and detect LED errors, there is a minimum effective output current requirement for each  $R_{ext}$ , such as  $I_{out, Th1}$ ,  $I_{out, Th2}$ , and  $I_{out, Th3}$ .

# Electrical Characteristics(V<sub>DD</sub>= 3.3V)

| Characte                         | eristics  | Symbol                  | Coi                                                                              | ndition                                            | Min.        | Тур. | Max.        | Unit  |

|----------------------------------|-----------|-------------------------|----------------------------------------------------------------------------------|----------------------------------------------------|-------------|------|-------------|-------|

| Supply Voltag                    | е         | $V_{DD}$                |                                                                                  | -                                                  | 3.0         | 3.3  | 3.6         | V     |

| Output Voltage                   | е         | V <sub>DS</sub>         | OUT0 ~ OUT7                                                                      |                                                    | -           | -    | 17.0        | V     |

|                                  |           | I <sub>OUT</sub>        | Test Circuit for Elec                                                            | trical Characteristics                             | 5           | -    | 120         | mA    |

| Output Curren                    | t         | I <sub>OH</sub>         | SDO                                                                              |                                                    | -           | -    | -1.0        | mA    |

|                                  |           | I <sub>OL</sub>         | SDO                                                                              |                                                    | -           | -    | 1.0         | mA    |

| land Valtage                     | "H" level | V <sub>IH</sub>         | Ta = -40~85°C                                                                    |                                                    | $0.7V_{DD}$ | -    | $V_{DD}$    | V     |

| Input Voltage                    | "L" level | V <sub>IL</sub>         | Ta = -40~85°C                                                                    |                                                    | GND         | -    | $0.3V_{DD}$ | V     |

| Output Leakag                    | e Current |                         | V <sub>DS</sub> =17.0V and char                                                  | nnel off                                           | -           | -    | 0.5         | μA    |

| 0 (. ()/                         | 200       | V <sub>OL</sub>         | I <sub>OL</sub> =+1.0mA                                                          |                                                    | -           | -    | 0.4         | V     |

| Output Voltage                   | SDO       | V <sub>OH</sub>         | I <sub>OH</sub> =-1.0mA                                                          |                                                    | 2.9         | -    | -           | V     |

| Output Current                   | 1         | I <sub>OUT1</sub>       | $V_{DS} = 0.5V; R_{ext} = 74$                                                    | 44Ω; CG= 0.992                                     | -           | 25.0 | -           | mA    |

| Current Skew (between channels)  |           | dl <sub>OUT1</sub>      | $I_{OUT} = 25mA$<br>$V_{DS} \ge 0.5V$                                            | -                                                  | -           | ±1   | ±3          | %     |

| Output Current                   | 2         | I <sub>OUT2</sub>       | $V_{DS} = 0.6V; R_{ext} = 3^{\circ}$                                             | 72Ω; CG= 0.992                                     | -           | 50.0 | -           | mA    |

| Current Skew<br>(between chan    | nels)     | dl <sub>OUT2</sub>      | $I_{OUT} = 50 \text{mA}$<br>$V_{DS} \ge 0.6 \text{V}$                            | $I_{OUT} = 50 \text{mA}$ $V_{DS} \ge 0.6 \text{V}$ |             | ±1   | ±3          | %     |

| Output Current<br>Output Voltage |           | %/dV <sub>DS</sub>      | V <sub>DS</sub> within 1.0V and                                                  | 3.0V                                               | -           | ±0.1 | -           | % / V |

| Output Current<br>Supply Voltage |           | %/dV <sub>DD</sub>      | V <sub>DD</sub> within 3.2V and                                                  | 3.6V                                               | -           | ±1   | -           | % / V |

| Pull-up Resista                  | ince      | R <sub>IN</sub> (up)    | OE/SW/ED                                                                         |                                                    | 250         | 500  | 800         | ΚΩ    |

| Pull-down Res                    | stance    | R <sub>IN</sub> (down)  | LE/MOD/CA                                                                        |                                                    | 250         | 500  | 800         | ΚΩ    |

| Threshold Curr                   |           | I <sub>out, Th1</sub>   | R <sub>ext</sub> =744 Ω, CG= 0.9                                                 | 992, I <sub>out, target</sub> = 25mA               | -           | -    | 24.9        | mA    |

| Error Detection                  |           | I <sub>out, Th2</sub>   | R <sub>ext</sub> =372 Ω, CG= 0.9                                                 | 992, I <sub>out, target</sub> = 50mA               | -           | -    | 40          | mA    |

|                                  |           | I <sub>DD</sub> (off) 0 | R <sub>ext</sub> =Open, OUT0 ~                                                   | OUT7 =Off, CG= 0.992                               | -           | 0.87 | -           |       |

|                                  | "OFF"     | I <sub>DD</sub> (off) 1 | $R_{ext}=744 \Omega$ , $\overline{OUT0} \sim \overline{OUT7} = Off$ , $CG=0.992$ |                                                    | -           | 3.7  | -           |       |

| Supply<br>Current                |           | I <sub>DD</sub> (off) 2 | R <sub>ext</sub> =372 Ω,                                                         | OUT7 =Off, CG= 0.992                               | -           | 6.37 | -           | mA    |

|                                  | "ON"      | I <sub>DD</sub> (on) 1  | R <sub>ext</sub> =744 Ω,                                                         | OUT7 =On, CG= 0.992                                | -           | 3.4  | -           |       |

|                                  | ON        | I <sub>DD</sub> (on) 2  | R <sub>ext</sub> =372 Ω, OUT0 ~                                                  | OUT7 =On, CG= 0.992                                | -           | 6.1  | -           |       |

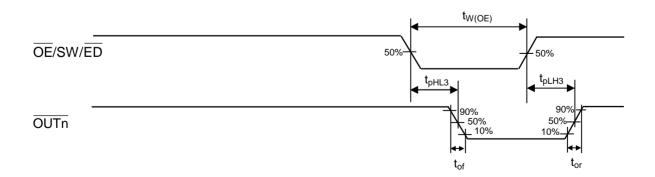

# **Switching Characteristics (V<sub>DD</sub>= 5.0V)**

| Cha                                 | aracteristics                        | Symbol              | Condition                                                                                                              | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                     | CLK - OUTn                           | t <sub>pLH1</sub>   |                                                                                                                        | -    | 100  | 150  | ns   |

|                                     | LE/MOD/CA - OUTn                     | t <sub>pLH2</sub>   |                                                                                                                        | -    | 100  | 150  | ns   |

| Time ("L" to "H")                   | OE/SW/ED - OUTn                      | t <sub>pLH3</sub>   |                                                                                                                        | -    | 100  | 150  | ns   |

|                                     | CLK - SDO                            | t <sub>pLH</sub>    |                                                                                                                        | 20   | 25   | 30   | ns   |

|                                     | CLK - OUTn                           | t <sub>pHL1</sub>   | Test Circuit for                                                                                                       | -    | 100  | 150  | ns   |

|                                     | LE/MOD/CA - OUTn                     | t <sub>pHL2</sub>   | Switching Characteristics                                                                                              | -    | 100  | 150  | ns   |

| Time ("H" to "L")                   | OE/SW/ED - OUTn                      | t <sub>pHL3</sub>   | V <sub>DD</sub> =5.0 V                                                                                                 | -    | 100  | 150  | ns   |

|                                     | CLK - SDO                            | t <sub>pHL</sub>    | $V_{DD}$ =5.0 V $V_{DS}$ =0.8 V $V_{IH}$ = $V_{DD}$ $V_{IL}$ = $V_{DD}$ $V_{IL}$ = $V_{DD}$ $V_{DD}$ $V_{DD}$ $V_{DD}$ | 20   | 25   | 30   | ns   |

|                                     | CLK                                  | t <sub>w(CLK)</sub> |                                                                                                                        | 20   | -    | -    | ns   |

| Pulse Width                         | LE/MOD/CA                            | t <sub>w(L)</sub>   |                                                                                                                        | 20   | -    | -    | ns   |

|                                     | OE/SW/ED (@ I <sub>out</sub> < 60mA) | $t_{w(OE)}$         | $V_L=4.0 \text{ V}$<br>$R_1=64 \Omega$                                                                                 | 200  | -    | -    | ns   |

| Hold Time for LE/M                  | IOD/CA                               | t <sub>h(L)</sub>   | C <sub>L</sub> =10 pF                                                                                                  | 10   | -    | -    | ns   |

| Setup Time for LE/                  | MOD/CA                               | t <sub>su(L)</sub>  | CG= 0.992                                                                                                              | 5    | -    | -    | ns   |

| Maximum CLK Rise                    | e Time                               | t <sub>r</sub> *    |                                                                                                                        | -    | -    | 500  | ns   |

| Maximum CLK Fall Time               |                                      | t <sub>f</sub> *    |                                                                                                                        | -    | -    | 500  | ns   |

| Output Rise Time of Vout (turn off) |                                      | t <sub>or</sub>     |                                                                                                                        | -    | 120  | 150  | ns   |

| Output Fall Time of Vout (turn on)  |                                      | t <sub>of</sub>     |                                                                                                                        | -    | 200  | 250  | ns   |

| Clock Frequency                     |                                      | F <sub>CLK</sub>    | Cascade<br>Operation                                                                                                   | -    | -    | 25.0 | MHz  |

<sup>\*</sup> If MBI5171 are connected in cascade and  $t_r$  or  $t_f$  is large, it may be critical to achieve the timing required for data transfer between two cascaded LED drivers MBI5171.

# Switching Characteristics (V<sub>DD</sub>= 3.3V)

| Cha                                 | aracteristics                        | Symbol              | Condition                                                  | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------|---------------------|------------------------------------------------------------|------|------|------|------|

|                                     | CLK - OUTn                           | t <sub>pLH1</sub>   |                                                            | -    | 100  | 150  | ns   |

| Propagation Delay                   | LE/MOD/CA - OUTn                     | t <sub>pLH2</sub>   |                                                            | -    | 100  | 150  | ns   |

| Time ("L" to "H")                   | OE/SW/ED - OUTn                      | t <sub>pLH3</sub>   |                                                            | -    | 100  | 150  | ns   |

|                                     | CLK - SDO                            | t <sub>pLH</sub>    |                                                            | 45   | 55   | 65   | ns   |

|                                     | CLK - OUTn                           | t <sub>pHL1</sub>   | Test Circuit for                                           | -    | 130  | 200  | ns   |

| Propagation Delay                   | LE/MOD/CA - OUTn                     | t <sub>pHL2</sub>   | Switching Characteristics                                  | -    | 130  | 200  | ns   |

| Time ("H" to "L")                   | OE/SW/ED - OUTn                      | t <sub>pHL3</sub>   | V <sub>DD</sub> =3.3 V                                     | -    | 130  | 200  | ns   |

|                                     | CLK - SDO                            | t <sub>pHL</sub>    | $V_{DD}=3.3 V$ $V_{DS}=0.8 V$ $V_{IH}=V_{DD}$ $V_{IL}=GND$ | 45   | 55   | 65   | ns   |

|                                     | CLK                                  | t <sub>w(CLK)</sub> |                                                            | 20   | -    | -    | ns   |

| Pulse Width                         | LE/MOD/CA                            | t <sub>w(L)</sub>   | R <sub>ext</sub> =372 Ω                                    | 20   | -    | -    | ns   |

|                                     | OE/SW/ED (@ I <sub>out</sub> < 60mA) | t <sub>w(OE)</sub>  | $V_L=4.0 V$ $R_L=64 \Omega$                                | 200  | -    | -    | ns   |

| Hold Time for LE/M                  | OD/CA                                | t <sub>h(L)</sub>   | C <sub>L</sub> =10 pF                                      | 10   | -    | -    | ns   |

| Setup Time for LE/I                 | MOD/CA                               | t <sub>su(L)</sub>  | CG= 0.992                                                  | 5    | -    | -    | ns   |

| Maximum CLK Rise                    | Maximum CLK Rise Time                |                     |                                                            | -    | -    | 500  | ns   |

| Maximum CLK Fall Time               |                                      | t <sub>f</sub>      |                                                            | -    | -    | 500  | ns   |

| Output Rise Time of Vout (turn off) |                                      | t <sub>or</sub>     |                                                            | -    | 120  | 150  | ns   |

| Output Fall Time of Vout (turn on)  |                                      | t <sub>of</sub>     |                                                            | -    | 200  | 400  | ns   |

| Clock Frequency                     |                                      | F <sub>CLK</sub>    | Cascade<br>Operation                                       | -    | -    | 12.0 | MHz  |

### **Test Circuit for Electrical Test Circuit for Switching Characteristics Characteristics** Іоит ОПО $\overline{\text{OUT0}}$ OE/SW OE/SW Function CLK LE/MOD/CA OUT7 LE/MOD/CA Generator OUT7 SDI SDO SDO R-EXT GND R-EXT GND $V_{IH}, V_{IL}$ Logic Input VIH = VDD CL Iref VIL = GND ··· tr = tf = 10 ns

# **Timing Waveform**

### **Normal Mode**

# Switching to Special Mode

# Reading Error Status Code

### **Operation Principle**

### **Constant Current**

In LED display applications, MBI5171 provides nearly no current variations from channel to channel and from IC to IC. This can be achieved by:

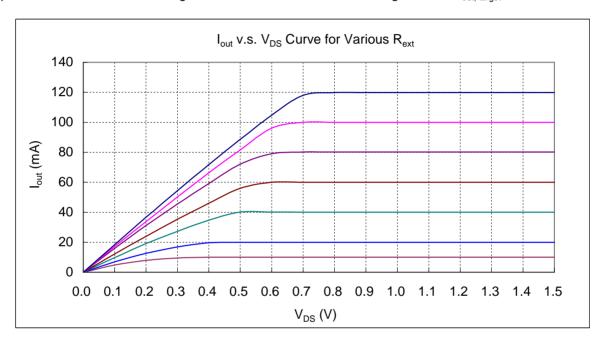

- 1) While  $I_{OUT} \le 100$ mA, the maximum current skew between channels is less than ±3% and that between ICs is less than ±6%.

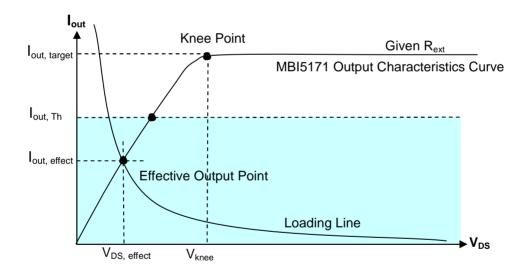

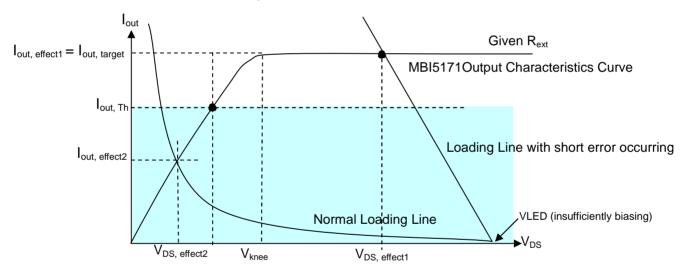

- 2) In addition, the characteristics curve of output stage in the saturation region is flat as the figure shown below. Thus, the output current can be kept constant regardless of the variations of LED forward voltages (Vf). The output current in the saturation region is so flat that we define it as target current I<sub>out, target</sub>.

### **Adjusting Output Current**

MBI5171 scales up the reference current  $I_{ref}$  set by the external resistor  $R_{ext}$  to sink a current  $I_{out}$  at each output port. Users can follow the below formulas to calculate the target output current  $I_{out, target}$  in the saturation region:

$$V_{R-EXT} = 1.25 Volt \times VG$$

$$I_{ref} = V_{R-EXT} / R_{ext}$$

if another end of the external resistor Rext is connected to ground.

$$I_{\text{out. target}} = I_{\text{ref}} \times 15 \times 3^{(CM-1)}$$

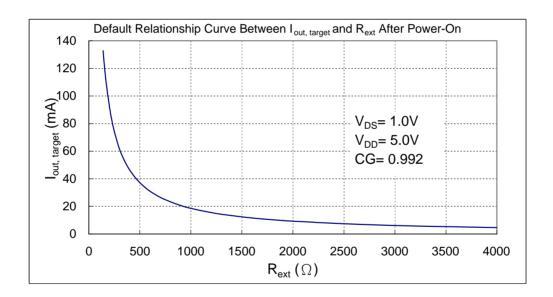

where  $R_{ext}$  is the resistance of the external resistor connected to the R-EXT terminal, and  $V_{R-EXT}$  is the voltage of the R-EXT terminal and controlled by the programmable voltage gain VG, which is defined by the Configuration Code. The Current Multiplier CM would determine that the ratio  $I_{out, target}/I_{ref}$  is 15 or 5. After power-on, the default value of VG is 127/128 = 0.992 and the default value of CM is 1, so that the ratio  $I_{out, target}/I_{ref}$  is 15. Based on the default VG and CM,

$$V_{R-EXT} = 1.25 \text{Volt x } 127/128 = 1.24 \text{Volt}$$

$$I_{out, target} = (1.24 Volt / R_{ext}) x 15$$

Hence, the default magnitude of current is around 50mA at  $372\Omega$  and 25mA at  $744\Omega$ . The default relationship after power-on between  $I_{out, target}$  and  $R_{ext}$  is shown in the following figure.

### **Operation Phases**

MBI5171 exploits the **Share-I-O™** technique to extend the functionality of pins in MBI5168 in order to provide LED load error detection and run-time programmable LED driving current in the Special Mode phase as well as the original function of MBI5168 in the Normal Mode phase. In order to switch between the two modes, MBI5171 monitors the signal  $\overline{OE}/SW/\overline{ED}$ . Once an one-clock-wide pulse of  $\overline{OE}/SW/\overline{ED}$  appears, MBI5171 would enter the two-clock-period transition phase---the Mode Switching phase. After power-on, the default operation mode is the Normal Mode.

### **Operation Mode Switching**

# Switching to the Special Mode CLK OE/SW/ED 1 0 1 x x LE/MOD/CA Normal Mode or Special Mode Normal Mode or Special Mode Switching Mode

As shown in the above figures, once a one-clock-wide short pulse "101" of  $\overline{OE}/SW/\overline{ED}$  appears, MBI5171 would enter the Mode Switching phase. At the 4<sup>th</sup> rising edge of CLK, if LE/MOD/CA is sampled as "Voltage High", MBI5171 would switch to the Special Mode; otherwise, it would switch to the Normal Mode. Worthwhile noticing, the signal LE/MOD/CA between the 3<sup>rd</sup> and the 5<sup>th</sup> rising edges of CLK can not latch any data. Its level is just used for determining which mode to switch. However, the short pulse of  $\overline{OE}/SW/\overline{ED}$  can still enable the output ports. During the mode switching, the serial data can still be transferred through the pin SDI and shifted out from the pin SDO.

### Note:

- 1. The signal sequence for the mode switching could be frequently used for making sure under which mode MBI5171 is working.

- 2. The aforementioned "1" and "0" are sampled at the rising edge of CLK. The "X" means its level would not affect the result of mode switching mechanism.

### Normal Mode Phase

MBI5171 in the Normal Mode phase has similar functionality to MBI5168. The serial data could be transferred into MBI5171 via the pin SDI, shifted in the Shift Register, and go out via the pin SDO. The LE/MOD/CA can latch the serial data in the Shift Register to the Output Latch.  $\overline{OE}/SW/\overline{ED}$  would enable the output drivers to sink current. The only difference is mentioned in the last paragraph about monitoring short pulse  $\overline{OE}/SW/\overline{ED}$ . The short pulse would trigger MBI5171 to switch the operation mode. However, as long as the signal LE/MOD/CA is not Voltage High in the Mode Switching phase, MBI5171 would still remain in the Normal Mode as if no mode switching occurs.

### Special Mode Phase

In the Special Mode, as long as  $\overline{\text{OE}/\text{SW}/\text{ED}}$  is not at the Voltage Low, the serial data can still be shifted to the Shift Register via the pin SDI and shifted out via the SDO pin, as in the Normal Mode. But there are two differences between the Special Mode and the Normal Mode.

### Reading Error Status Code (in Special Mode)

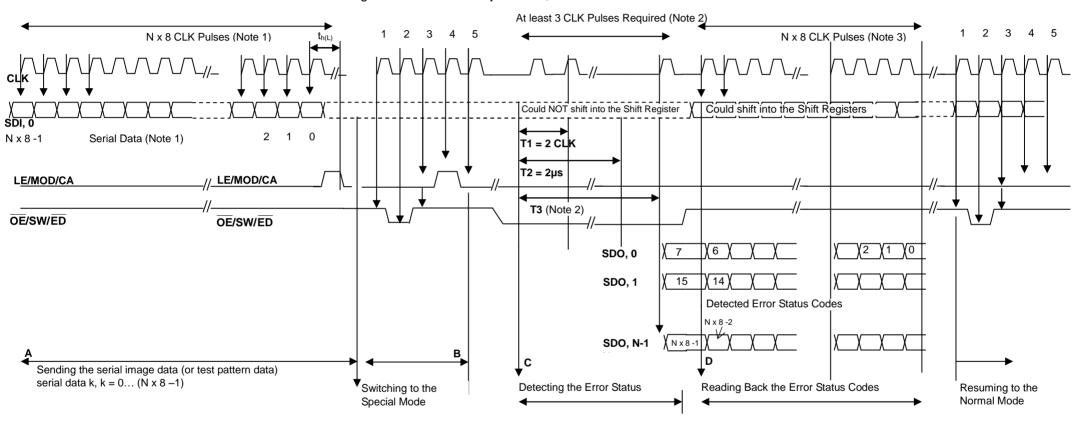

The first difference is that when the state of  $\overline{\text{OE}/\text{SW/ED}}$  is pulled down to Voltage Low, MBI5171 in the Special Mode would execute error detection and load error status codes into the Shift Register, as well as enabling output ports to sink current. The above figure shows the timing sequence for error detection. The shown "0" and "1" are sampled at the rising edge of each CLK. At least three "0" must be sampled at the Voltage Low signal  $\overline{\text{OE}/\text{SW/ED}}$ . Just after the 2<sup>nd</sup> "0" is sampled, the data input source of the Shift Register would come from 8-bit parallel error status codes out of the circuit Error Detector, instead of serial data via the pin SDI. Normally, the error status codes will be correctly generated at least 2µs after the falling edge of  $\overline{\text{OE}/\text{SW/ED}}$ . The occurrence of the 3<sup>rd</sup> or later "0" results in the event that MBI5171 saves the detected error status codes into the Shift Register. Thus, when  $\overline{\text{OE}/\text{SW/ED}}$  is at the Voltage Low state, the serial data cannot be shifted into MBI5171 via the pin SDI. But when the state of  $\overline{\text{OE}/\text{SW/ED}}$  is pulled up to Voltage High from Voltage Low, the data input source of the Shift Register would again come from the pin SDI. At the same time, the output ports are disabled and the error detection is completed. Then, the error status codes saved in the Shift Register could be shifted out via the pin SDO bit by bit along with CLK, as well as the new serial data can be shifted into MBI5171 via the pin SDI.

The limitation is that in the Special Mode, it couldn't be allowed to **simultaneously** transfer serial data and detect LED load error status.

### **Writing Configuration Code (in Special Mode)**

The second difference is that the active high signal LE/MOD/CA latches the serial data in the Shift Register to the Configuration Latch, instead of the Output Latch. The latched serial data is regarded as the Configuration Code. The code would be memorized until power off or the Configuration Latch is re-written. As shown above, the timing for writing the Configuration Code is the same as that in the Normal Mode for latching output channel data. As aforementioned descriptions, both of Configuration Code and Error Status Code are transferred in common 8-bit Shift Register. Users must pay attention to the sequence of error detection and current adjustment to avoid the Configuration Code being overwritten by Error Status Code.

### **Open-Circuit Detection Principle**

The principle of MBI5171 LED Open-Circuit Detection is based on the comparison between the effective current level  $I_{out, effect}$  of each output port and the threshold current  $I_{out, Th}$  corresponding to  $I_{out, target}$ . The cross point between the **Loading Line** and **MBI5171 Output Characteristics Curve** is called as effective output point ( $V_{DS, effect}$ ,

I<sub>out, effect</sub>). If LED fails, due to open circuit, the **Loading Line** and the effective output point would change. Then, MBI5171 would catch the error status. But if the port is disabled, the output current would be absolutely 0mA and MBI5171 could not distinguish the change of the **Loading Line**. Thus, to detect the status of LED correctly, the output ports must be enabled. The relationship between the detected Error Status code and the position of the effective output point is shown in the following table.

| State of Output<br>Port | Condition of Effective Output<br>Point                             | Detected Open-Circuit<br>Error Status Code | Meaning      |

|-------------------------|--------------------------------------------------------------------|--------------------------------------------|--------------|

| OFF                     | $I_{ m out,\; effect} \; = \; 0 { m mA} \; << \; I_{ m out,\; Th}$ | "0"                                        | -            |

| ON                      | $I_{ m out,\ effect}\ <\ I_{ m out,\ Th}$                          | "0"                                        | Open Circuit |

| ON                      | $I_{ m out,  effect} \; \geqq I_{ m out,  Th}$                     | "1"                                        | Normal       |

Note: As  $I_{out, target} \ge 25 mA$ , the threshold current  $I_{out, Th} = I_{out, target} \times 0.6 + 10 mA$

As  $I_{\text{out, target}}~<~25\text{mA}$ , the threshold current  $I_{\text{out, Th}}=~I_{\text{out, target}}$

Because the target current  $I_{out, target}$  in the saturation region set by the external resistor  $R_{ext}$  and CG is a little bigger than the corresponding threshold current  $I_{out, Th}$  for error detection, system design engineers had better place the effective output point of normal LED load in the saturation region after the knee point, for instance, if they want to detect the LED open error. Then while LED is open, the effective output point would move to the origin, where  $I_{out} = 0$ mA. So, MBI5171 can distinguish and detect it and report an error status codes "0".

In fact, if LED's are normal, the enabled ports would report error status codes "1" and the disabled would report "0". The error status codes are the same as the content in the Output Latch.

### **Short-Circuit Detection Principle**

When LED is damaged, a short-circuit error may occur. To effectively detect the short-circuit error, LEDs need insufficient biasing. The principle of MBI5171 LED Short Circuit Detection is based on the fact that the LED loading status is judged by comparing the effective current value( $I_{out, effect}$ ) of each output port with the threshold current( $I_{out, Th}$ ). When normal LED is insufficiently biased, its effective output point would be located at the segment  $I_{out, effect} < I_{out, Th}$  of MBI5171 Output Characteristics Curve, compared with LED with a short error falling within the segment  $I_{out, effect} > I_{out, Th}$ . The relationship between the Error Status code and the effective output point is shown below:

| State of Output Port | Condition of Effective Output Point              | Detected Short-Circuit Error Status Code | Meaning       |

|----------------------|--------------------------------------------------|------------------------------------------|---------------|

| OFF                  | $I_{\text{out, effect}} = 0$                     | "0"                                      | -             |

| ON                   | l <sub>out, effect</sub> < l <sub>out, Th</sub>  | "0"                                      | Normal        |

| ON                   | $I_{	ext{out, effect}}  \geq  I_{	ext{out, Th}}$ | "1"                                      | Short Circuit |

### 8-Bit Configuration Code and Current Gain CG

|                  | Bit Definition of 8-Bit Configuration Code |       |       |       |       |       |       |       |

|------------------|--------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

|                  | Bit 0                                      | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 |

| Meaning          | СМ                                         | HC    | CC0   | CC1   | CC2   | CC3   | CC4   | CC5   |

| Default<br>Value | 1                                          | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

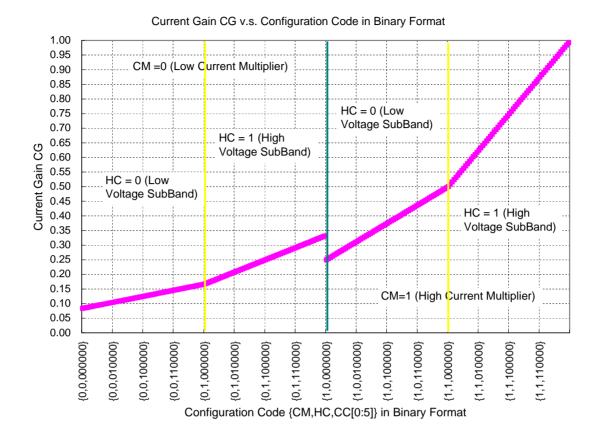

Bit definition of the Configuration Code in the Configuration Latch is shown above. Bit 7 is first sent into MBI5171 via the pin SDI. Bit 1 ~ 7, {HC, CC[0:5]}, would determine the voltage gain (VG), that affects the voltage at R-EXT terminal and indirectly the reference current  $I_{ref}$  flowing through the external resistor at terminal R-EXT. Bit 0 is the Current Multiplier (CM) bit, that determines the ratio  $I_{out, target}/I_{ref}$ . Each combination of VG and CM would give a Current Gain (CG).

I VG: the relationship between {HC,CC[0:5]} and the Voltage Gain VG can be formulated as below:

$$VG = (1 + HC) \times (1 + D/64) / 4$$

D = CC0 x

$$2^5$$

+ CC1 x  $2^4$  + CC2 x  $2^3$  + CC3 x  $2^2$  + CC4 x  $2^1$  + CC5 x  $2^0$

where HC is 1 or 0, and D is the binary value of CC[0:5]. So, the VG could be regarded as a floating-point number with one bit exponent HC and 6-bit mantissa CC[0:5]. {HC,CC[0:5]} divides the programmable voltage gain VG into 128 steps and two sub-bands:

Low voltage sub-band (HC=0): VG = 1/4 ~ 127/256, linearly divided into 64 steps;

High voltage sub-band (HC=1):  $VG = 1/2 \sim 127/128$ , linearly divided into 64 steps, too.

I CM: as well as determining the ratio I<sub>out, target</sub>/I<sub>ref</sub>, the CM bit would limit the output current range.

High Current Multiplier (CM=1):  $I_{out, target}/I_{ref} = 15$  and suitable for output current range  $I_{out} = 10 \sim 120 mA$ .

Low Current Multiplier (CM=0):  $I_{out. target}/I_{ref} = 5$  and suitable for output current range  $I_{out} = 5 \sim 40$ mA.

I CG: the total Current Gain is defined as the following.

$$V_{R-FXT} = 1.25 Volt * VG$$

$$I_{ref} = V_{R-EXT} / R_{ext}$$

if another end of the external resistor  $R_{ext}$  is connected to ground.

$$I_{out, target} = I_{ref} * 15 * 3^{(CM-1)} = 1.25 Volt / R_{ext} * VG * 15 * 3^{(CM-1)} = (1.25 Volt / R_{ext} * 15) * CG$$

We define  $CG = VG * 3^(CM-1)$ . Hence  $CG = (1/12) \sim (127/128)$  and it is divided into 256 steps, totally. If CG = 127/128 = 0.992, the  $I_{out. target}$ - $R_{ext}$  relationship is similar to that in MBI5168.

For example,

a) When the Configuration Code  $\{CM, HC, CC[0:5]\} = \{1,1,111111\},\$

$$VG = 127/128 = 0.992$$

; and  $CG = VG * 3^0 = VG = 0.992$

b) When the Configuration Code is {1,1,000000},

$$VG = (1+0)*(1+0/64)/4 = 1/2 = 0.5$$

; and  $CG = 0.5$

c) When the Configuration Code is {0,0,000000},

$$VG = (1+0)*(1+0/64)/4 = 1/4$$

; and  $CG = (1/4)*3^-1 = 1/12$

After power on, the default value of the Configuration Code {CM, HC, CC[0:5]} is {1,1,111111}. Thus, VG = CG = 0.992. The relationship between the Configuration Code and the Current Gain CG is shown in the following.

# **Timing Chart for Current Adjustment**

N of MBI5171 are connected in cascade, i.e., SDO, k --> SDI, k+1. And, all MBI5171 are connected to the same signal bus CLK, LE/MOD/CA and  $\overline{OE}$  /SW/  $\overline{ED}$  .

### **Timing Chart for Detecting LED Error**

The connection of each MBI5171 is referred to "Timing Chart for Current Adjustment", shown on P26.

### Note 1:

N x 8 CLK pulses are required to shift the serial image data N x 8 bits needed by N of MBI5171.

### Note 2

T1 = 2 CLK pluses are required to change input of Shift Register. And, when Short-Circuit Detection is executed, LEDs should be insufficiently biased during this period.

$T2 = 2 \mu s$  is required to obtain the stable error status result.

T3 = the third CLK pulses is required before OE/SW/ED goes Voltage High. The rising edge of CLK writes the error status codes back to the MBI5171 built-in Shift Register.

### Note 3:

The rising edge of CLK after the rising edge of  $\overline{\text{OE}/\text{SW/ED}}$  would shift the new serial image data and error codes. An LED error will be represented by a "0", to overwrite the original image data "1". Image Data k, k = 0... (N x 8 -1), = all "1" is suggested.

N x 8 CLK pulses shift all N x 8 error results (Error Status Code) via Node SDO, N-1.

# **Application Information**

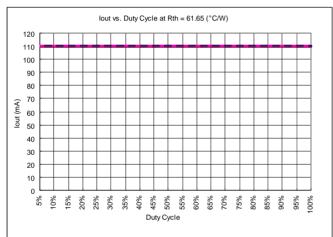

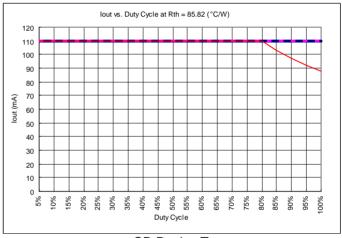

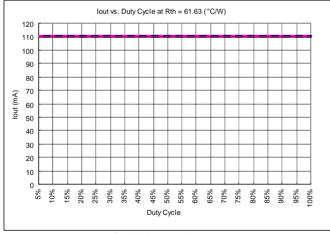

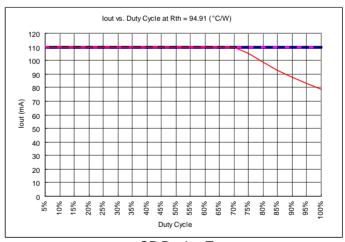

### Package Power Dissipation (P<sub>D</sub>)

The maximum allowable package power dissipation is determined as  $P_D(max) = (Tj - Ta) / R_{th(j-a)}$ . When 8 output channels are turned on simultaneously, the actual package power dissipation is

$$P_D(act) = (I_{DD} \times V_{DD}) + (I_{OUT} \times Duty \times V_{DS} \times 8)$$

Therefore, to keep  $P_D(act) \le P_D(max)$ , the allowable maximum output current as a function of duty cycle is

$$I_{OUT} = \{ [ (Tj - Ta) / R_{th(j-a)}] - (I_{DD} x V_{DD}) \} / V_{DS} / Duty / 8 \}$$

where Tj = 150°C.

**CN Device Type**

CD Device Type

**CDW Device Type**

**CP Device Type**

| <b>Condition</b> : V <sub>DS</sub> = 1.0V, V <sub>DD</sub> = 5.0V, 8 output channels active, Ta is listed in the legend below. |                            |                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|--|--|--|

| Device Type                                                                                                                    | $R_{th(j-a)}(^{\circ}C/W)$ | Note             |  |  |  |

| CN                                                                                                                             | 61.65                      | <b>——— 25</b> °C |  |  |  |

| CD                                                                                                                             | 85.82                      |                  |  |  |  |

| CDW                                                                                                                            | 61.63                      |                  |  |  |  |

| СР                                                                                                                             | 94.91                      |                  |  |  |  |

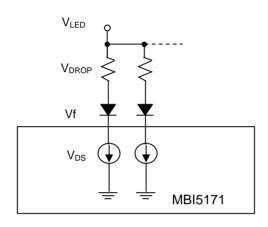

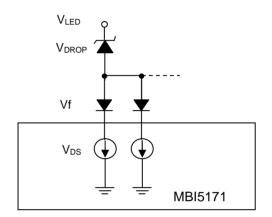

### Load Supply Voltage (V<sub>LED</sub>)

Considering the package power dissipating limits, users had better operate MBI5171 within  $V_{DS} = 0.4V \sim 1.0V$ . If  $V_{LED}$  is higher, for instance, than 5V,  $V_{DS}$  may be so high that  $P_{D(act)} > P_{D(max)}$ , where  $V_{DS} = V_{LED} - Vf$ . In this case, it is recommended to use as low supply voltage as possible or to arrange a voltage reducer,  $V_{DROP}$ . The voltage reducer lets  $V_{DS} = (V_{LED} - Vf) - V_{DROP}$ . Resistors or Zener diodes can be used as the reducers in the applications as shown in the following figures.

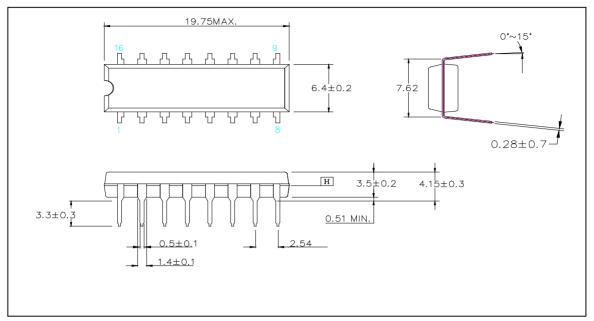

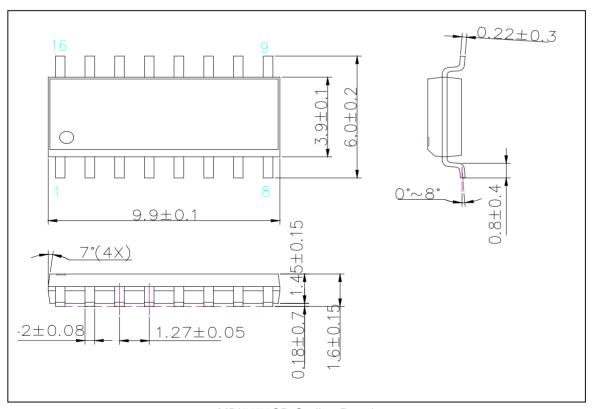

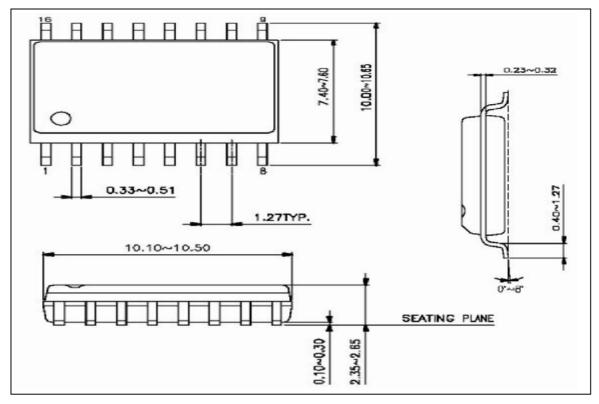

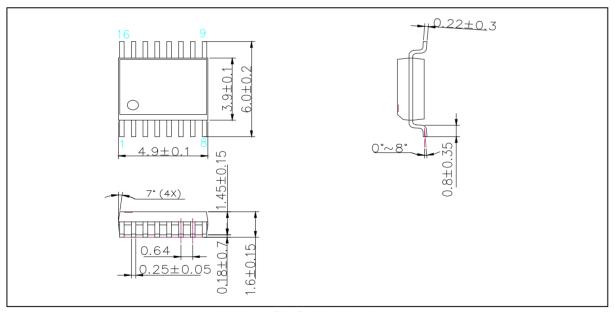

# **Outline Drawings**

MBI5171CN Outline Drawing

MBI5171CD Outline Drawing

MBI5171CDW Outline Drawing

MBI5171CP Outline Drawing

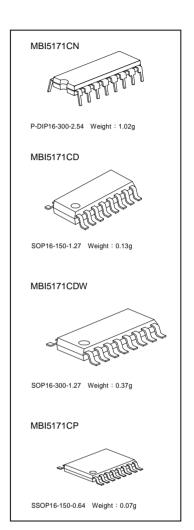

### **MBI5171 Package Information**

| Device Type | Package Type     | Weight(g) |  |  |  |  |

|-------------|------------------|-----------|--|--|--|--|

| CN          | P-DIP16-300-2.54 | 1.02      |  |  |  |  |

| CD          | SOP16-150-1.27   | 0.13      |  |  |  |  |

| CDW         | SOP16-300-1.27   | 0.37      |  |  |  |  |

| CP          | SSOP16-150-0.64  | 0.07      |  |  |  |  |

Note: The unit for the outline drawings is mm.