## LCD Driver

# LCD Driver for 160 Display Units BL55077(A)

### General Description

The BL55077(A) is a general LCD driver IC for 160 units LCD panel. It features a wide operating supply voltage range, incorporates simple communication interface with microcomputer and is suitable for multiple application.

#### **Features**

- ◆ Single-chip LCD controller/driver

- ◆ Selecable backplane drive configuration: static, 1/2, 1/3 or 1/4 backplane multiplexing.

- ◆ Selectable display bias configuration : static, 1/2 or 1/3 bias

- ◆ Operation voltage: 2~5.5V

- ◆ Serial data interface

- ◆ 160(40 SEG x 4 COM) Display Units

- ◆ Low power dissipation design: Power saving mode: Idd=14uA @ 5V and Idd=9uA @ 3.3V; Sleeping mode: Idd≈1.5uA

- ◆ Maybe cascaded up to 16pcs for large LCD application

- Versatile blinking modes

- ◆ VLCD for adjusting LCD operating voltage

- ◆ TTL/CMOS compatible

- ◆ Excellent EMC immunity

- ◆ Compatible with general microcomputer

- ◆ LQFP-64 package

### **Application**

Power Meter, Gas Meter...

Toy, Clock

Industrial instrument

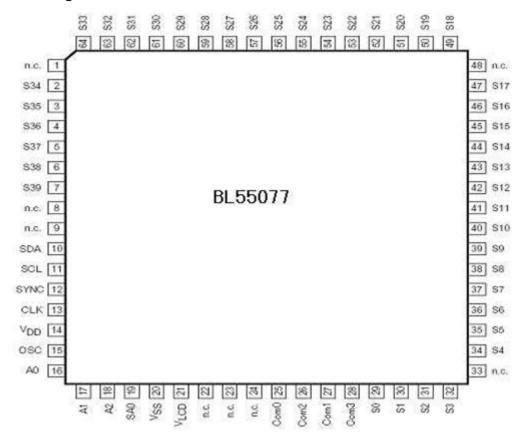

## Pin Assignment

## Pin Description

| Pin No.                     | SYMBOL                 | DESCRIPTION                     |

|-----------------------------|------------------------|---------------------------------|

| 10                          | SDA                    | Serial data input/output        |

| 11                          | SCL                    | Serial clock input              |

| 12                          | SYNC                   | Cascade synchronization clock   |

| 13                          | CLK                    | External clock input            |

| 14                          | Vdd                    | Supply voltage                  |

| 15                          | OSC                    | Oscillator input                |

| 16-18                       | A0、A1、A2               | Subaddress inputs               |

| 19                          | SA0                    | Slave address input;bit0        |

| 20                          | Vss                    | ground                          |

| 21                          | Vlcd                   | LCD supply voltage              |

| 25-28                       | Com0, Com2, Com1, Com3 | Common terminal driving output  |

| 29-32, 34-37, 49-64, 2-7    | S0S39                  | Segment terminal driving output |

| 1, 8, 9, 22, 23, 24, 33, 48 | NC                     | Unused                          |

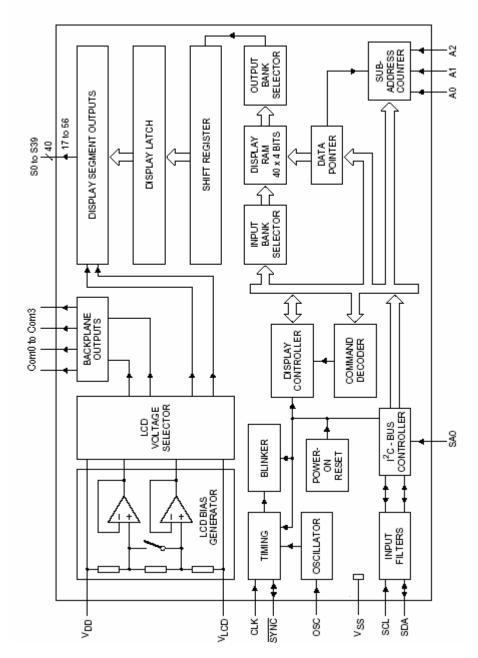

## **Block Diagram**

## **Function Description**

### **Function Circuit**

The BL550077(A) has all function circuits that can directly drive any static or multiplexed LCD containing up to four commons and up to 40 segments. The function circuits include:Power-on reset, LCD bias generator, LCD voltage selector, Oscillator, display RAM, Display latch, Shift register, Common/segment outputs, input/output bank selector, Blinker, Data pointer, Subaddress counter, etc.

## **Display Function Decription**

The display RAM is a static 40x 4-bit RAM which stores LCD data. A logic 1 in the RAM bit-map indicates the on state of the corresponding LCD segment; similarly, a logic 0 indicates the off state. There is a one-to-one correspondence between the RAM addresses and the segment outputs, and between the individual bits of a RAM word and the common outputs.

| Display RAM address and SEGMENT(S0~S39) output |   |   |   |   |   |   |   |   |   |    |    |    |    |

|------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|

| COM                                            |   | 0 | 1 | 2 | 3 | 0 | 0 | 0 | 0 | 36 | 37 | 38 | 39 |

| (Com0~                                         | 0 |   |   |   |   |   |   |   |   |    |    |    |    |

|                                                | 1 |   |   |   |   |   |   |   |   |    |    |    |    |

| Com3)                                          | 2 |   |   |   |   |   |   |   |   |    |    |    |    |

| outpu<br>t                                     | 3 |   |   |   |   |   |   |   |   |    |    |    |    |

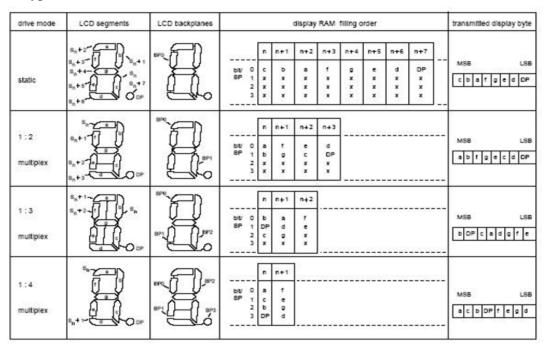

When display data is transmitted to the BL55077(A), the display bytes received are stored in the display RAM in accordance with the selected LCD drive mode. To illustrate the filling order, an example of a 7-segment numeric display showing all drive modes is given in Fig.3; the RAM filling organization depicted applies equally to other LCD types.

x = data bit unchanged.

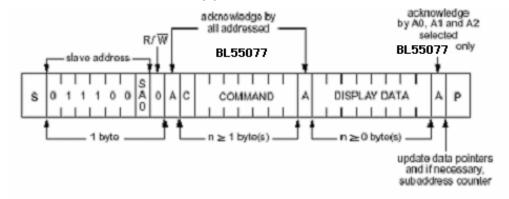

# <sup>2</sup>C-bus protocol

Two I2C-bus slave addresses (0111000 and 0111001) are reserved for the BL55077(A). The least significant bit of the slave address that a BL55077(A) will

respond to is defined by the level tied at its input SA0. Therefore, two types of BL55077(A) can be distinguished on the same I2C-bus which allows:

- 1) Up to 16 BL55077(A) on the same I2C-bus for very large LCD applications.

- 2) The use of two types of LCD multiplex on the same I2C-bus.

The I2C-bus protocol is shown in Fig.4. The sequence is initiated with a START condition (S) from the I2C-bus master which is followed by one of the two BL55077(A) slave addresses available. All BL55077(A)s with the corresponding SA0 level acknowledge in parallel with the slave address but all BL55077(A)s with the alternative SA0 level ignore the whole I2C-bus transfer. After acknowledgement, one or more command bytes (m) follow which define the status of the addressed BL55077(A)s. The last command byte is tagged with a cleared most significant bit, the continuation bit C. The command bytes are also acknowledged by all addressed BL55077(A)s on the bus. After the last command byte, a series of display data bytes(n) may follow. These display bytes are stored in the display RAM at the address specified by the data pointer and the subaddress counter. Both data pointer and subaddress counter are automatically updated and the data is directed to the intended BL55077(A) device. The acknowledgement after each byte is made only by the (A0, A1 and A2) addressed BL55077(A). After the last display byte, the I2C-bus master issues a STOP condition (P).

#### Command Decoder

The command decoder identifies command bytes that arrive on the  $I^2C$ -bus. All available commands carry a continuation bit C in their most significant bit position. The five commands available to the BL55077(A) are defined.

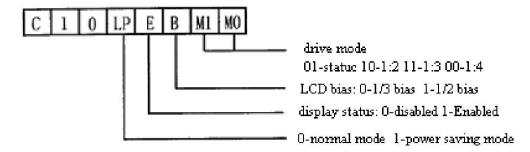

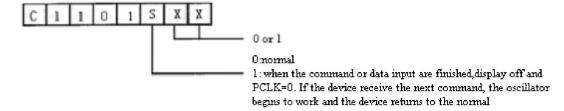

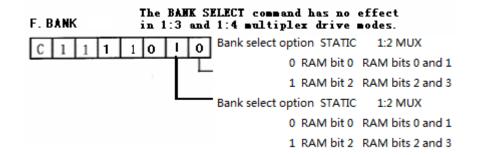

#### A. Mode set

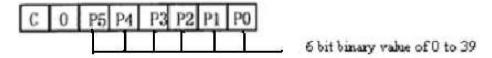

## B. Load data pointer

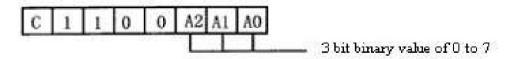

#### C. Device select

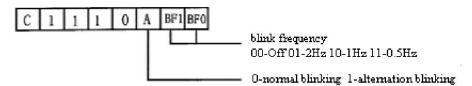

#### D . Blink control

### E. Sleep control

## Absolute Maximum Rating

| Parameter                 | Symbol       | Rating                    | Unit         |

|---------------------------|--------------|---------------------------|--------------|

| Supply voltage            | Vdd          | -0.5 <b>~</b> +6.0        | V            |

| LCD operating voltage     | Vlcd         | 0 <b>∼</b> Vdd            | V            |

| Input voltage             | Vi           | Vss-0.5~Vdd+0.5           | V            |

| Output voltage            | Vo           | Vlcd-0.5 <b>~</b> Vdd+0.5 | V            |

| Vdd,Vss,Vlcd current      | Idd,Iss,Ilcd | -50 <b>~</b> +50          | mA           |

| Maximum power consumption | Ptot         | 400                       | mW           |

| Operating temperature     | Topr         | -40 <b>~</b> +75          | $^{\circ}$   |

| Storage temperature       | Tstg         | -65 <b>~</b> +150         | $^{\circ}$ C |

## DC Characteristic(Ta=25 C)

| Symbol      | Parameter          | <b>Test Condition</b>             | Min    | Тур | Max    | Unit |

|-------------|--------------------|-----------------------------------|--------|-----|--------|------|

|             | IC Operating       |                                   |        |     |        |      |

| Vdd         | voltage            |                                   | 2.5    | ı   | 5.5    | V    |

|             | LCD operating      |                                   |        |     |        |      |

| Vlcd        | voltage            |                                   | 0      | -   | Vdd-2  | V    |

|             |                    | Vdd=5V,VLCD=0V,Normal             |        |     |        |      |

| Idd1        | Supply current     | mode,internal oscillator          | -      | 25  | 50     | uA   |

|             |                    | Vdd=5V,VLCD=0V,power              |        |     |        |      |

| Idd2        | Supply current     | saving mode,internal oscillator   | -      | 14  | 30     | uA   |

|             |                    | Vdd=3.3V,VLCD=0V,Normalm          |        |     |        |      |

| Idd3        | Supply current     | ode,internal oscillator           | -      | 16  | 30     | uA   |

|             |                    | Vdd=3.3V,VLCD=0V,power            |        |     |        |      |

| Idd4        | Supply current     | saving mode,internal oscillator   | -      | 9   | 15     | uA   |

| I           |                    |                                   |        |     |        |      |

| SL          | Sleep current      | Vdd=5V,VLCD=0V                    | -      | 1.5 |        | uA   |

| ViL         | Low voltage input  | SDA,SCL                           | Vss    | -   | 0.3Vdd | V    |

|             | High voltage       |                                   |        |     |        |      |

| ViH         | input              | SDA,SCL                           | 0.7Vdd | -   | Vdd    | V    |

| Rph         | Pull high resister | SYNC                              | 30     | 50  | 100    | kΩ   |

|             | DC voltage         |                                   |        |     |        |      |

| $V_{\rm C}$ | component          | C <sub>COM</sub> =32nF, COM0~COM3 | -40    |     | 40     | mV   |

|             | DC voltage         |                                   |        |     |        |      |

| $V_{S}$     | component          | C <sub>S</sub> =4.7nF, SEG0~SEG39 | -40    |     | 40     | mV   |

NOTE: the voltage of DC voltage component test: VDD=3.3 V, VLCD=0V

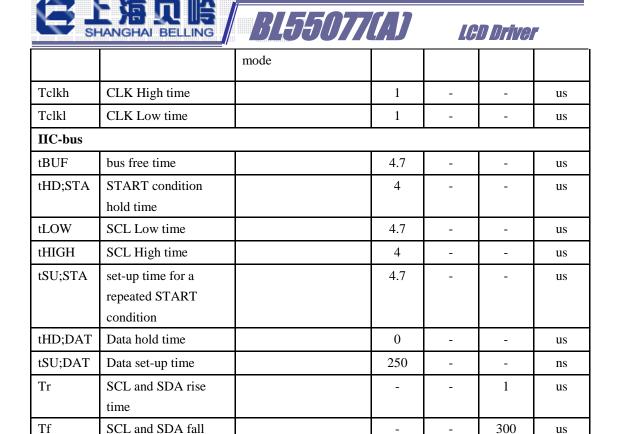

### AC Characteristics

| Symbol | Parameter Conditions M |                     | MIN. | TYP. | MAX. | UNIT. |

|--------|------------------------|---------------------|------|------|------|-------|

| Fclk   | Oscillator frequency   | Vdd=5V,normal mode  | 125  | 180  | 300  | KHz   |

| Fclklp | Oscillator frequency   | Vdd=3.3V,power-save | 21   | 31   | 48   | KHz   |

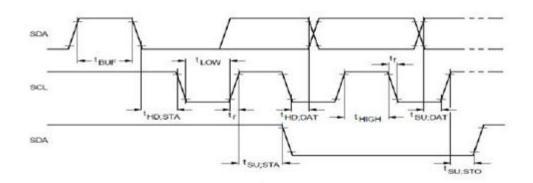

# I<sup>2</sup>C-bus timing waveforms

condition

time

Set-up time for STOP

tSU;STO

4.7

us

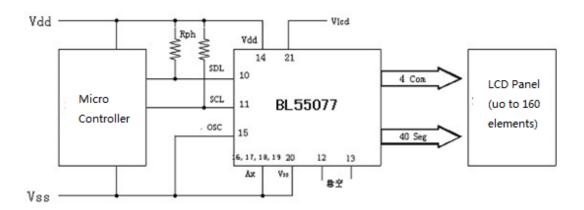

## **Typical Application**

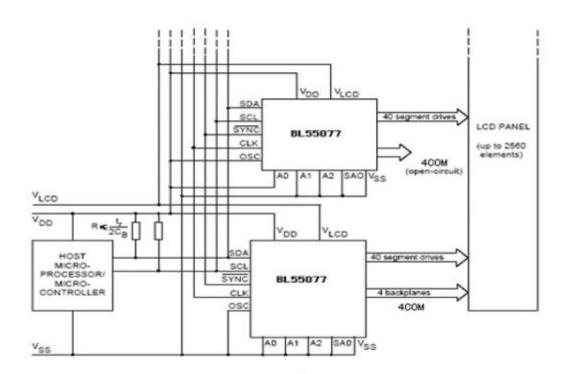

## Typical cascaded Application

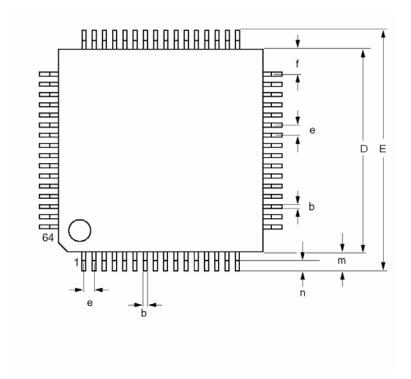

## Package Outlines

LQFP64

| Unit | D         | Е          | е   | b             | f            | m   | n         |

|------|-----------|------------|-----|---------------|--------------|-----|-----------|

| mm   | 10.0(0.1) | 12.0(0.15) | 0.5 | 0. 22 (0. 05) | 1. 25 (0. 2) | 1.0 | 0.6(0.15) |