# Precision, Dual-Channel, JFET Input, Rail-to-Rail Instrumentation Amplifier

Data Sheet AD8224

#### **FEATURES**

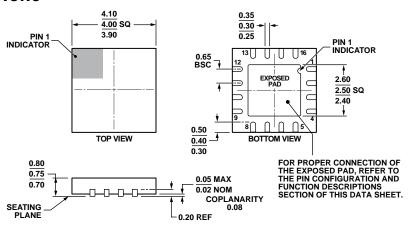

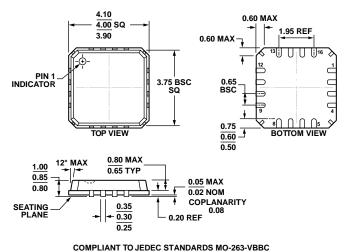

Two channels in a small 4 mm × 4 mm LFCSP

Custom LFCSP package with hidden paddle

Permits routing and vias underneath package

Allows full bias current performance

Low input currents

10 pA maximum input bias current (B grade)

0.6 pA maximum input offset current (B grade)

High CMRR

100 dB CMRR (minimum), G = 10 (B grade) 90 dB CMRR (minimum) to 10 kHz, G = 10 (B grade)

**Excellent ac specifications and low power**

1.5 MHz bandwidth (G = 1)

14 nV/√Hz input noise (1 kHz)

Slew rate: 2 V/µs

$750\,\mu\text{A}$  quiescent current per amplifier

Versatility

Rail-to-rail output

Input voltage range to below negative supply rail

4 kV ESD protection

4.5 V to 36 V single supply

±2.25 V to ±18 V dual supply

Gain set with single resistor (G = 1 to 1000)

#### **APPLICATIONS**

Medical instrumentation

Precision data acquisition

Transducer interfaces

Differential drives for high resolution input ADCs

Remote sensors

#### **GENERAL DESCRIPTION**

The AD8224 is the first single-supply, JFET input instrumentation amplifier available in the space-saving 16-lead, 4 mm  $\times$  4 mm LFCSP. It requires the same board area as a typical single instrumentation amplifier yet doubles the channel density and offers a lower cost per channel without compromising performance.

Designed to meet the needs of high performance, portable instrumentation, the AD8224 has a minimum common-mode rejection ratio (CMRR) of 86 dB at dc and a minimum CMRR of 80 dB at 10 kHz for G=1. Maximum input bias current is 10 pA and typically remains below 300 pA over the entire industrial temperature range. Despite the JFET inputs, the AD8224 typically has a noise corner of only 10 Hz.

With the proliferation of mixed-signal processing, the number of power supplies required in each system has grown. Designed

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

**Document Feedback**

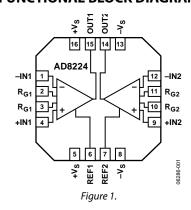

#### **FUNCTIONAL BLOCK DIAGRAM**

Table 1. In Amps and Difference Amplifiers by Category

| High<br>Perform     | Low                 | High<br>Voltage | Mil<br>Grade | Low<br>Power       | Digital<br>Gain     |

|---------------------|---------------------|-----------------|--------------|--------------------|---------------------|

| AD8220 <sup>1</sup> | AD8553 <sup>1</sup> | AD628           | AD620        | AD627 <sup>1</sup> | AD8231 <sup>1</sup> |

| AD8221              | AD623 <sup>1</sup>  | AD629           | AD621        |                    | AD8250              |

| AD8222              |                     |                 | AD524        |                    | AD8251              |

|                     |                     |                 | AD526        |                    | AD8555 <sup>1</sup> |

|                     |                     |                 | AD624        |                    | AD8556 <sup>1</sup> |

|                     |                     |                 |              |                    | AD8557 <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> Rail-to-rail output.

to alleviate this problem, the AD8224 can operate on a  $\pm 18~V$  dual supply, as well as on a single +5 V supply. The device's rail-to-rail output stage maximizes dynamic range on the low voltage supplies common in portable applications. Its ability to run on a single 5 V supply eliminates the need for higher voltage, dual supplies. The AD8224 draws 750  $\mu$ A of quiescent current per amplifier, making it ideal for battery powered devices.

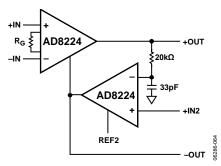

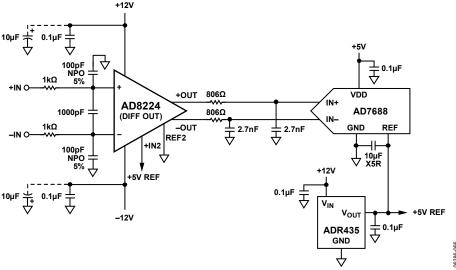

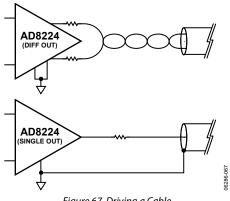

In addition, the AD8224 can be configured as a single-channel, differential output, instrumentation amplifier. Differential outputs provide high noise immunity, which can be useful when the output signal must travel through a noisy environment, such as with remote sensors. The configuration can also be used to drive differential input ADCs. For a single-channel version, use the AD8220.

**Data Sheet**

## **AD8224**

# **TABLE OF CONTENTS**

| Features                                                | Layout                                                 | 22  |

|---------------------------------------------------------|--------------------------------------------------------|-----|

| Applications1                                           | Solder Wash                                            | 23  |

| Functional Block Diagram1                               | Input Bias Current Return Path                         | 23  |

| General Description                                     | Input Protection                                       | 23  |

| Revision History                                        | RF Interference                                        | 24  |

| Specifications                                          | Common-Mode Input Voltage Range                        | 24  |

| Absolute Maximum Ratings9                               | Applications Information                               | 25  |

| Thermal Resistance9                                     | Driving an ADC                                         | 25  |

| ESD Caution9                                            | Differential Output                                    | 25  |

| Pin Configurations and Function Descriptions            | Driving a Differential Input ADC                       | 26  |

| Typical Performance Characteristics                     | Driving Cabling                                        | 26  |

| Theory of Operation                                     | Outline Dimensions                                     | 27  |

| Gain Selection                                          | Ordering Guide                                         | 28  |

| Reference Terminal                                      |                                                        |     |

| REVISION HISTORY                                        |                                                        |     |

| 4/16—Rev. C to Rev. D                                   | Added Hidden Paddle Package Section and Exposed Pado   | lle |

| Changed CP-16-13 to CP-16-26Throughout                  | Package Section and Figure 58                          | 21  |

| Changes to Figure 3                                     | Updated Outline Dimensions                             | 26  |

| Added Figure 4 and Table 12; Renumbered Sequentially 11 | Changes to Ordering Guide                              | 27  |

| Updated Outline Dimensions                              |                                                        |     |

| Changes to Ordering Guide                               | 4/07—Rev. 0 to Rev. A                                  |     |

| change to cracing carac                                 | Changes to Features, General Description, and Figure 1 | 1   |

| 12/13—Rev. B to Rev. C                                  | Changes to Table 2                                     | 3   |

| Changes to Input Current Parameter and Power Supply     | Changes to Table 3 and Table 4                         | 5   |

| Parameter, Table 2                                      | Changes to Table 5                                     |     |

| Changes to Table 3 and Table 4                          | Changes to Table 6 and Table 7                         |     |

| Changes to Input Current Parameter and Power Supply     | Changes to Figure 2                                    |     |

| Parameter, Table 5                                      | Changes to Figure 3                                    | 10  |

| Changes to Table 99                                     | Inserted Figure 4, Figure 5, and Figure 6; Renumbered  |     |

| Changes to Figure 53                                    | Sequentially                                           |     |

| Change to Theory of Operation Section                   | Changes to Figure 7                                    |     |

| Change to Exposed Paddle Package Section                | Changes to Figure 20 and Figure 21                     |     |

| Change to Input Protection Section                      | Changes to Figure 28                                   |     |

| Updated Outline Dimensions (Dimensions Not Changed,     | Changes to Theory of Operation and Figure 55           |     |

| Minimums and Maximums Added)                            | Changes to Ordering Guide                              | 26  |

| 5/10—Rev. A to Rev. B                                   | 1/07—Revision 0: Initial Version                       |     |

| Changes to Features Section                             |                                                        |     |

| Added Table 10                                          |                                                        |     |

| Changes to Figure 3 and Table 1110                      |                                                        |     |

## **SPECIFICATIONS**

$V_S$ + = +15 V,  $V_S$ - = -15 V,  $V_{REF}$  = 0 V,  $T_A$  = 25°C, G = 1,  $R_L$  = 2  $k\Omega^1$ , unless otherwise noted. Table 2 displays the specifications for an individual instrumentation amplifier configured for a single-ended output or dual instrumentation amplifiers configured for differential outputs as shown in Figure 64.

Table 2. Individual Amplifier in Single-Ended Configuration or Dual Amplifiers in Differential Output Configuration<sup>2</sup>,  $V_S = \pm 15 \text{ V}$

|                                       | Test Conditions/                               |        | A Grad | e      |        | B Grad | e      |            |

|---------------------------------------|------------------------------------------------|--------|--------|--------|--------|--------|--------|------------|

| Parameter                             | Comments                                       | Min    | Тур    | Max    | Min    | Тур    | Max    | Unit       |

| COMMON-MODE REJECTION RATIO (CMRR)    |                                                |        |        |        |        |        |        |            |

| CMRR DC to 60 Hz with                 | $V_{CM} = \pm 10 \text{ V}$                    |        |        |        |        |        |        |            |

| 1 kΩ Source Imbalance                 |                                                |        |        |        |        |        |        |            |

| G = 1                                 |                                                | 78     |        |        | 86     |        |        | dB         |

| G = 10                                |                                                | 94     |        |        | 100    |        |        | dB         |

| G = 100                               |                                                | 94     |        |        | 100    |        |        | dB         |

| G = 1000                              |                                                | 94     |        |        | 100    |        |        | dB         |

| CMRR at 10 kHz                        | $V_{CM} = \pm 10 \text{ V}$                    |        |        |        |        |        |        |            |

| G = 1                                 |                                                | 74     |        |        | 80     |        |        | dB         |

| G = 10                                |                                                | 84     |        |        | 90     |        |        | dB         |

| G = 100                               |                                                | 84     |        |        | 90     |        |        | dB         |

| G = 1000                              |                                                | 84     |        |        | 90     |        |        | dB         |

| NOISE                                 | RTI noise = $\sqrt{(e_{ni}^2 + (e_{no}/G)^2)}$ |        |        |        |        |        |        |            |

| Voltage Noise, 1 kHz                  | V(C <sub>ni</sub> · (C <sub>no</sub> , C) )    |        |        |        |        |        |        |            |

| Input Voltage Noise, e <sub>ni</sub>  | $V_{IN}+$ , $V_{IN}-=0$ V                      |        | 14     |        |        | 14     | 17     | nV/√Hz     |

| Output Voltage Noise, e <sub>no</sub> | $V_{IN}+, V_{IN}-=0 V$                         |        | 90     |        |        | 90     | 100    | nV/√Hz     |

| RTI, 0.1 Hz to 10 Hz                  | V <sub>IN</sub> 1, V <sub>IN</sub> – O V       |        | 50     |        |        | 50     | 100    | 1117, 1112 |

| G = 1                                 |                                                |        | 5      |        |        | 5      |        | μV p-p     |

|                                       |                                                |        |        |        |        |        |        |            |

| G = 1000                              | 6 4111                                         |        | 0.8    |        |        | 0.8    |        | μV p-p     |

| Current Noise                         | f = 1 kHz                                      |        | 1      |        |        | 1      |        | fA/√Hz     |

| VOLTAGE OFFSET                        | $RTI V_{OS} = (V_{OSI}) + (V_{OSO}/G)$         |        |        |        |        |        |        |            |

| Input Offset, V <sub>OSI</sub>        |                                                |        |        | 300    |        |        | 175    | μV         |

| Average TC                            | $T = -40^{\circ}C \text{ to } +85^{\circ}C$    |        |        | 10     |        |        | 5      | μV/°C      |

| Output Offset, V <sub>OSO</sub>       |                                                |        |        | 1200   |        |        | 800    | μV         |

| Average TC                            | $T = -40^{\circ}C \text{ to } +85^{\circ}C$    |        |        | 10     |        |        | 5      | μV/°C      |

| Offset RTI vs. Supply (PSR)           | $V_{s} = \pm 5 \text{ V to } \pm 15 \text{ V}$ |        |        |        |        |        |        |            |

| G = 1                                 |                                                | 86     |        |        | 86     |        |        | dB         |

| G = 10                                |                                                | 96     |        |        | 100    |        |        | dB         |

| G = 100                               |                                                | 96     |        |        | 100    |        |        | dB         |

| G = 1000                              |                                                | 96     |        |        | 100    |        |        | dB         |

| INPUT CURRENT                         |                                                |        |        |        |        |        |        |            |

| Input Bias Current                    |                                                |        |        | 25     |        |        | 10     | рА         |

| Over Temperature <sup>3</sup>         | $T = -40^{\circ}C \text{ to } +85^{\circ}C$    |        | 300    |        |        | 300    |        | pA         |

| Input Offset Current                  |                                                |        |        | 2      |        |        | 0.6    | pA         |

| Over Temperature <sup>3</sup>         | $T = -40^{\circ}C \text{ to } +85^{\circ}C$    |        | 5      |        |        | 5      |        | pA         |

| REFERENCE INPUT                       |                                                | 1      |        |        |        |        |        | 1          |

| $R_{IN}$                              |                                                |        | 40     |        |        | 40     |        | kΩ         |

| I <sub>IN</sub>                       | $V_{IN} + , V_{IN} - = 0 V$                    |        |        | 70     |        |        | 70     | μΑ         |

| ™<br>Voltage Range                    | 11.4 . 11.4                                    | $-V_s$ |        | $+V_s$ | $-V_s$ |        | $+V_s$ | V          |

| Gain to Output                        |                                                | 3      | 1 ±    | 3      | 3      | 1 ±    | 3      | V/V        |

| •                                     |                                                |        | 0.0001 |        |        | 0.0001 |        |            |

|                                        | Test Conditions/                                                  | A Grade            |                     |              | B Grade            |                     |              |        |

|----------------------------------------|-------------------------------------------------------------------|--------------------|---------------------|--------------|--------------------|---------------------|--------------|--------|

| Parameter                              | Comments                                                          | Min                | Тур                 | Max          | Min                | Тур                 | Max          | Unit   |

| GAIN                                   | $G = 1 + (49.4 \text{ k}\Omega/\text{R}_G)$                       |                    |                     |              |                    |                     |              |        |

| Gain Range                             |                                                                   | 1                  |                     | 1000         | 1                  |                     | 1000         | V/V    |

| Gain Error                             | $V_{OUT} = \pm 10 \text{ V}$                                      |                    |                     |              |                    |                     |              |        |

| G = 1                                  |                                                                   |                    |                     | 0.06         |                    |                     | 0.04         | %      |

| G = 10                                 |                                                                   |                    |                     | 0.3          |                    |                     | 0.2          | %      |

| G = 100                                |                                                                   |                    |                     | 0.3          |                    |                     | 0.2          | %      |

| G = 1000                               |                                                                   |                    |                     | 0.3          |                    |                     | 0.2          | %      |

| Gain Nonlinearity                      | $V_{OUT} = -10 \text{ V to } +10 \text{ V}$                       |                    |                     |              |                    |                     |              |        |

| G = 1                                  | $R_L = 10 \text{ k}\Omega$                                        |                    | 8                   | 15           |                    | 8                   | 15           | ppm    |

| G = 10                                 | $R_L = 10 \text{ k}\Omega$                                        |                    | 5                   | 10           |                    | 5                   | 10           | ppm    |

| G = 100                                | $R_L = 10 \text{ k}\Omega$                                        |                    | 15                  | 25           |                    | 15                  | 25           | ppm    |

| G = 1000                               | $R_L = 10 \text{ k}\Omega$                                        |                    | 100                 | 150          |                    | 100                 | 150          | ppm    |

| G = 1                                  | $R_L = 2 k\Omega$                                                 |                    | 15                  | 20           |                    | 15                  | 20           | ppm    |

| G = 10                                 | $R_L = 2 k\Omega$                                                 |                    | 12                  | 20           |                    | 12                  | 20           | ppm    |

| G = 100                                | $R_L = 2 k\Omega$                                                 |                    | 35                  | 50           |                    | 35                  | 50           | ppm    |

| G=1000                                 | $R_L = 2 k\Omega$                                                 |                    | 180                 | 250          |                    | 180                 | 250          | ppm    |

| Gain vs. Temperature                   |                                                                   |                    |                     |              |                    |                     |              |        |

| G = 1                                  |                                                                   |                    | 3                   | 10           |                    | 2                   | 5            | ppm/°C |

| G > 10                                 |                                                                   |                    |                     | -50          |                    |                     | -50          | ppm/°C |

| INPUT                                  |                                                                   |                    |                     |              |                    |                     |              |        |

| Impedance (Pin to Ground) <sup>4</sup> |                                                                   |                    | 10 <sup>4</sup>   5 |              |                    | 10 <sup>4</sup>   5 |              | GΩ  pF |

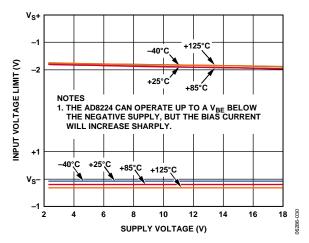

| Input Operating Voltage Range⁵         | $V_s = \pm 2.25 \text{ V to } \pm 18 \text{ V}$ for dual supplies | $-V_{s} - 0.1$     |                     | $+V_s-2$     | $-V_{s}-0.1$       |                     | $+V_s-2$     | V      |

| Over Temperature                       | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                       | $-V_{s} - 0.1$     |                     | $+V_{s}-2.1$ | $-V_{s} - 0.1$     |                     | $+V_{s}-2.1$ | V      |

| OUTPUT                                 |                                                                   |                    |                     |              |                    |                     |              |        |

| Output Swing                           | $R_L = 2 k\Omega$                                                 | -14.25             |                     | +14.25       | -14.25             |                     | +14.25       | ٧      |

| Over Temperature                       | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                       | -14.3              |                     | +14.1        | -14.3              |                     | +14.1        | V      |

| Output Swing                           | $R_L = 10 \text{ k}\Omega$                                        | -14.7              |                     | +14.7        | -14.7              |                     | +14.7        | ٧      |

| Over Temperature                       | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                       | -14.6              |                     | +14.6        | -14.6              |                     | +14.6        | ٧      |

| Short-Circuit Current                  |                                                                   |                    | 15                  |              |                    | 15                  |              | mA     |

| POWER SUPPLY                           |                                                                   |                    |                     |              |                    |                     |              |        |

| Operating Range                        |                                                                   | ±2.25 <sup>6</sup> |                     | ±18          | ±2.25 <sup>6</sup> |                     | ±18          | ٧      |

| Quiescent Current (Per Amplifier)      |                                                                   |                    | 750                 | 800          |                    | 750                 | 800          | μΑ     |

| Over Temperature                       | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                       |                    | 850                 | 900          |                    | 850                 | 900          | μΑ     |

| TEMPERATURE RANGE                      |                                                                   |                    |                     |              |                    |                     |              |        |

| For Specified Performance              |                                                                   | -40                |                     | +85          | -40                |                     | +85          | °C     |

| Operational <sup>7</sup>               |                                                                   | -40                |                     | +125         | -40                |                     | +125         | °C     |

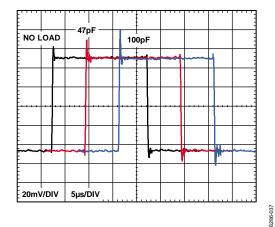

$<sup>^1</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 kΩ.  $^2$  Refers to the differential configuration shown in Figure 64.

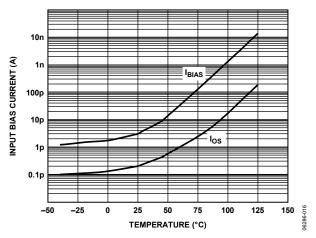

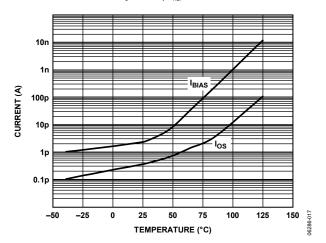

<sup>&</sup>lt;sup>3</sup> Refer to Figure 15 and Figure 16 for the relationship between input current and temperature.

<sup>4</sup> Differential and common-mode input impedance can be calculated from the pin impedance:  $Z_{DIFF} = 2(Z_{PIN})$ ;  $Z_{CM} = Z_{PIN}/2$ .

<sup>5</sup> The AD8224 can operate up to a diode drop below the negative supply; however, the bias current increases sharply. The input voltage range reflects the maximum allowable voltage where the input bias current is within the specification.

<sup>&</sup>lt;sup>6</sup> At this supply voltage, ensure that the input common-mode voltage is within the input voltage range specification.

<sup>&</sup>lt;sup>7</sup> The AD8224 is characterized from -40°C to +125°C. See the Typical Performance Characteristics section for expected operation in this temperature range.

$V_s$ + = +15 V,  $V_s$ - = -15 V,  $V_{REF}$  = 0 V,  $T_A$  = 25°C, G = 1,  $R_L$  = 2  $k\Omega^1$ , unless otherwise noted. Table 3 displays the specifications for the dynamic performance of each individual instrumentation amplifier.

Table 3. Dynamic Performance of Each Individual Amplifier—Single-Ended Output Configuration,  $V_s = \pm 15 \text{ V}$

|                              | Test Conditions/                     |     | A Grade | 2   |     | B Grade |     |      |

|------------------------------|--------------------------------------|-----|---------|-----|-----|---------|-----|------|

| Parameter                    | Comments                             | Min | Тур     | Max | Min | Тур     | Max | Unit |

| DYNAMIC RESPONSE             |                                      |     |         |     |     |         |     |      |

| Small Signal Bandwidth –3 dB |                                      |     |         |     |     |         |     |      |

| G = 1                        |                                      |     | 1500    |     |     | 1500    |     | kHz  |

| G = 10                       |                                      |     | 800     |     |     | 800     |     | kHz  |

| G = 100                      |                                      |     | 120     |     |     | 120     |     | kHz  |

| G =1000                      |                                      |     | 14      |     |     | 14      |     | kHz  |

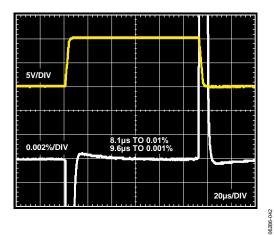

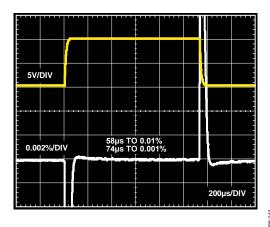

| Settling Time 0.01%          | $\Delta V_0 = \pm 10 \text{ V step}$ |     |         |     |     |         |     |      |

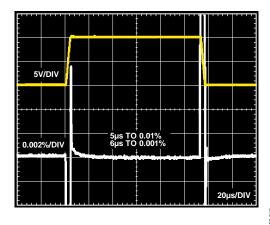

| G = 1                        |                                      |     | 5       |     |     | 5       |     | μs   |

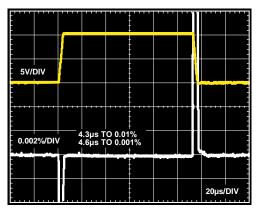

| G = 10                       |                                      |     | 4.3     |     |     | 4.3     |     | μs   |

| G = 100                      |                                      |     | 8.1     |     |     | 8.1     |     | μs   |

| G =1000                      |                                      |     | 58      |     |     | 58      |     | μs   |

| Settling Time 0.001%         | $\Delta V_0 = \pm 10 \text{ V step}$ |     |         |     |     |         |     |      |

| G = 1                        |                                      |     | 6       |     |     | 6       |     | μs   |

| G = 10                       |                                      |     | 4.6     |     |     | 4.6     |     | μs   |

| G = 100                      |                                      |     | 9.6     |     |     | 9.6     |     | μs   |

| G =1000                      |                                      |     | 74      |     |     | 74      |     | μs   |

| Slew Rate                    |                                      |     |         |     |     |         |     |      |

| G = 1 to 100                 |                                      | 2   |         |     | 2   |         |     | V/µs |

$<sup>^{1}</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 kΩ.

$V_S$ + = +15 V,  $V_S$ - = -15 V,  $V_{REF}$  = 0 V,  $T_A$  = 25°C, G = 1,  $R_L$  = 2  $k\Omega^1$ , unless otherwise noted. Table 4 displays the specifications for the dynamic performance of both amplifiers when used in the differential output configuration shown in Figure 64.

Table 4. Dynamic Performance of Both Amplifiers—Differential Output Configuration<sup>2</sup>,  $V_s = \pm 15 \text{ V}$

|                              | Test Conditions/                     |     | A Grade | e   | B Grade |      |     |      |

|------------------------------|--------------------------------------|-----|---------|-----|---------|------|-----|------|

| Parameter                    | Comments                             | Min | Тур     | Max | Min     | Тур  | Max | Unit |

| DYNAMIC RESPONSE             |                                      |     |         |     |         |      |     |      |

| Small Signal Bandwidth –3 dB |                                      |     |         |     |         |      |     |      |

| G = 1                        |                                      |     | 1500    |     |         | 1500 |     | kHz  |

| G = 10                       |                                      |     | 800     |     |         | 800  |     | kHz  |

| G = 100                      |                                      |     | 120     |     |         | 120  |     | kHz  |

| G=1000                       |                                      |     | 14      |     |         | 14   |     | kHz  |

| Settling Time 0.01%          | $\Delta V_0 = \pm 10 \text{ V step}$ |     |         |     |         |      |     |      |

| G = 1                        | ·                                    |     | 5       |     |         | 5    |     | μs   |

| G = 10                       |                                      |     | 4.3     |     |         | 4.3  |     | μs   |

| G = 100                      |                                      |     | 8.1     |     |         | 8.1  |     | μs   |

| G =1000                      |                                      |     | 58      |     |         | 58   |     | μs   |

| Settling Time 0.001%         | $\Delta V_0 = \pm 10 \text{ V step}$ |     |         |     |         |      |     |      |

| G = 1                        | ·                                    |     | 6       |     |         | 6    |     | μs   |

| G = 10                       |                                      |     | 4.6     |     |         | 4.6  |     | μs   |

| G = 100                      |                                      |     | 9.6     |     |         | 9.6  |     | μs   |

| G =1000                      |                                      |     | 74      |     |         | 74   |     | μs   |

| Slew Rate                    |                                      |     |         |     |         |      |     |      |

| G = 1 to 100                 |                                      | 2   |         |     | 2       |      |     | V/µs |

$<sup>^1</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 kΩ.

<sup>2</sup> Refers to the differential configuration shown in Figure 64.

$V_S$  + = 5 V,  $V_S$  - = 0 V,  $V_{REF}$  = 2.5 V,  $T_A$  = 25°C, G = 1,  $R_L$  = 2 k $\Omega^1$ , unless otherwise noted. Table 5 displays the specifications for an individual instrumentation amplifier configured for a single-ended output or dual instrumentation amplifiers configured for differential outputs as shown in Figure 64.

Table 5. Individual Amplifier in Single-Ended Configuration or Dual Amplifiers in Differential Output Configuration $^2$ ,  $V_s = +5 \text{ V}$

|                                       | Test Conditions/                                                   | A Grade |                |                 | B Gra    |        |                 |        |

|---------------------------------------|--------------------------------------------------------------------|---------|----------------|-----------------|----------|--------|-----------------|--------|

| Parameter                             | Comments                                                           | Min     | Тур            | Max             | Min      | Тур    | Max             | Unit   |

| COMMON-MODE REJECTION RATIO (CMRR)    |                                                                    |         |                |                 |          |        |                 |        |

| CMRR DC to 60 Hz with                 | $V_{CM} = 0 \text{ to } 2.5 \text{ V}$                             |         |                |                 |          |        |                 |        |

| 1 k $\Omega$ Source Imbalance         |                                                                    |         |                |                 |          |        |                 |        |

| G = 1                                 |                                                                    | 78      |                |                 | 86       |        |                 | dB     |

| G = 10                                |                                                                    | 94      |                |                 | 100      |        |                 | dB     |

| G = 100                               |                                                                    | 94      |                |                 | 100      |        |                 | dB     |

| G = 1000                              |                                                                    | 94      |                |                 | 100      |        |                 | dB     |

| CMRR at 10 kHz                        |                                                                    |         |                |                 |          |        |                 |        |

| G = 1                                 |                                                                    | 74      |                |                 | 80       |        |                 | dB     |

| G = 10                                |                                                                    | 84      |                |                 | 90       |        |                 | dB     |

| G = 100                               |                                                                    | 84      |                |                 | 90       |        |                 | dB     |

| G = 1000                              |                                                                    | 84      |                |                 | 90       |        |                 | dB     |

| NOISE                                 | RTI noise = $\sqrt{(e_{ni}^2 + (e_{no}/G)^2)}$                     |         |                |                 |          |        |                 |        |

| Voltage Noise, 1 kHz                  | $V_{s} = \pm 2.5 \text{ V}$                                        |         |                |                 |          |        |                 |        |

| Input Voltage Noise, e <sub>ni</sub>  | $V_{IN}^{+} + V_{IN}^{-} = 0 \text{ V}, V_{RFF}^{-} = 0 \text{ V}$ |         | 14             |                 |          | 14     | 17              | nV/√Hz |

| Output Voltage Noise, e <sub>no</sub> | $V_{IN}^{+} + V_{IN}^{-} = 0 \text{ V}, V_{RFF}^{-} = 0 \text{ V}$ |         | 90             |                 |          | 90     | 100             | nV/√Hz |

| RTI, 0.1 Hz to 10 Hz                  | IIV IIV III                                                        |         |                |                 |          |        |                 |        |

| G = 1                                 |                                                                    |         | 5              |                 |          | 5      |                 | μV p-p |

| G = 1000                              |                                                                    |         | 8.0            |                 |          | 0.8    |                 | μV p-p |

| Current Noise                         | f = 1 kHz                                                          |         | 1              |                 |          | 1      |                 | fA/√Hz |

| VOLTAGE OFFSET                        | $RTIV_{OS} = (V_{OSI}) + (V_{OSO}/G)$                              |         |                |                 |          |        |                 |        |

| Input Offset, V <sub>OSI</sub>        | 03 1 031 1 030 1                                                   |         |                | 300             |          |        | 250             | μV     |

| Average TC                            | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                        |         |                | 10              |          |        | 5               | μV/°C  |

| Output Offset, V <sub>OSO</sub>       |                                                                    |         |                | 1200            |          |        | 800             | μV     |

| Average TC                            | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                        |         |                | 10              |          |        | 5               | μV/°C  |

| Offset RTI vs. Supply (PSR)           |                                                                    |         |                |                 |          |        |                 | '      |

| G = 1                                 |                                                                    | 86      |                |                 | 86       |        |                 | dB     |

| G = 10                                |                                                                    | 96      |                |                 | 100      |        |                 | dB     |

| G = 100                               |                                                                    | 96      |                |                 | 100      |        |                 | dB     |

| G = 1000                              |                                                                    | 96      |                |                 | 100      |        |                 | dB     |

| INPUT CURRENT                         |                                                                    |         |                |                 |          |        |                 |        |

| Input Bias Current                    |                                                                    |         |                | 25              |          |        | 10              | рА     |

| Over Temperature <sup>3</sup>         | $T = -40^{\circ}C \text{ to } +85^{\circ}C$                        |         | 300            |                 |          | 300    |                 | pA     |

| Input Offset Current                  |                                                                    |         |                | 2               |          |        | 0.6             | pА     |

| Over Temperature <sup>3</sup>         | $T = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                  |         | 5              |                 |          | 5      |                 | Aq     |

| REFERENCE INPUT                       |                                                                    |         |                |                 | <u> </u> |        |                 | F .    |

| R <sub>IN</sub>                       |                                                                    |         | 40             |                 |          | 40     |                 | kΩ     |

| I <sub>IN</sub>                       | $V_{IN}+,V_{IN}-=0$ V                                              |         | · <del>·</del> | 70              |          |        | 70              | μΑ     |

| Voltage Range                         | - 1111 - 7 - 1111                                                  | $-V_s$  |                | +V <sub>s</sub> | $-V_s$   |        | +V <sub>s</sub> | V      |

| Gain to Output                        |                                                                    | .,      | 1 ±            | 5               | -,5      | 1 ±    | 5               | V/V    |

|                                       |                                                                    |         | 0.0001         |                 |          | 0.0001 |                 | ', '   |

|                                   | Test Conditions/                                      | A Grade |        |              | B Grade |        |              |        |

|-----------------------------------|-------------------------------------------------------|---------|--------|--------------|---------|--------|--------------|--------|

| Parameter                         | Comments                                              | Min     | Тур    | Max          | Min     | Тур    | Max          | Unit   |

| GAIN                              | $G = 1 + (49.4 \text{ k}\Omega/\text{R}_G)$           |         |        |              |         |        |              |        |

| Gain Range                        |                                                       | 1       |        | 1000         | 1       |        | 1000         | V/V    |

| Gain Error                        |                                                       |         |        |              |         |        |              |        |

| G = 1                             | $V_{OUT} = 0.3 \text{ V to } 2.9 \text{ V}$           |         |        | 0.06         |         |        | 0.04         | %      |

| G = 10                            | $V_{OUT} = 0.3 \text{ V to } 3.8 \text{ V}$           |         |        | 0.3          |         |        | 0.2          | %      |

| G = 100                           | $V_{OUT} = 0.3 \text{ V to } 3.8 \text{ V}$           |         |        | 0.3          |         |        | 0.2          | %      |

| G = 1000                          | $V_{OUT} = 0.3 \text{ V to } 3.8 \text{ V}$           |         |        | 0.3          |         |        | 0.2          | %      |

| Nonlinearity                      | $V_{OUT} = 0.3 \text{ V to } 2.9 \text{ V for G} = 1$ |         |        |              |         |        |              |        |

|                                   | $V_{OUT} = 0.3 \text{ V to } 3.8 \text{ V for G} > 1$ |         |        |              |         |        |              |        |

| G = 1                             | $R_L = 10 \text{ k}\Omega$                            |         | 35     | 50           |         | 35     | 50           | ppm    |

| G = 10                            | $R_L = 10 \text{ k}\Omega$                            |         | 35     | 50           |         | 35     | 50           | ppm    |

| G = 100                           | $R_L = 10 \text{ k}\Omega$                            |         | 50     | 75           |         | 50     | 75           | ppm    |

| G = 1000                          | $R_L = 10 \text{ k}\Omega$                            |         | 90     | 115          |         | 90     | 115          | ppm    |

| G = 1                             | $R_L = 2 k\Omega$                                     |         | 35     | 50           |         | 35     | 50           | ppm    |

| G = 10                            | $R_L = 2 k\Omega$                                     |         | 35     | 50           |         | 35     | 50           | ppm    |

| G = 100                           | $R_L = 2 k\Omega$                                     |         | 50     | 75           |         | 50     | 75           | ppm    |

| G = 1000                          | $R_L = 2 k\Omega$                                     |         | 175    | 200          |         | 175    | 200          | ppm    |

| Gain vs. Temperature              |                                                       |         |        |              |         |        |              |        |

| G = 1                             |                                                       |         | 3      | 10           |         | 2      | 5            | ppm/°C |

| G > 10                            |                                                       |         |        | -50          |         |        | -50          | ppm/°C |

| INPUT                             |                                                       |         |        |              |         |        |              |        |

| Impedance (Pin to Ground)⁴        |                                                       |         | 104  6 |              |         | 104  6 |              | GΩ  pF |

| Input Voltage Range⁵              |                                                       | -0.1    |        | $+V_s-2$     | -0.1    |        | $+V_s-2$     | V      |

| Over Temperature                  | $T = -40^{\circ}C \text{ to } +85^{\circ}C$           | -0.1    |        | $+V_{s}-2.1$ | -0.1    |        | $+V_{s}-2.1$ | V      |

| OUTPUT                            |                                                       |         |        |              |         |        |              |        |

| Output Swing                      | $R_L = 2 k\Omega$                                     | 0.25    |        | 4.75         | 0.25    |        | 4.75         | V      |

| Over Temperature                  | $T = -40^{\circ}C \text{ to } +85^{\circ}C$           | 0.3     |        | 4.70         | 0.3     |        | 4.70         | V      |

| Output Swing                      | $R_L = 10 \text{ k}\Omega$                            | 0.15    |        | 4.85         | 0.15    |        | 4.85         | V      |

| Over Temperature                  | $T = -40^{\circ}C \text{ to } +85^{\circ}C$           | 0.2     |        | 4.80         | 0.2     |        | 4.80         | V      |

| Short-Circuit Current             |                                                       |         | 15     |              |         | 15     |              | mA     |

| POWER SUPPLY                      |                                                       |         |        |              |         |        |              |        |

| Operating Range                   |                                                       | 4.5     |        | 36           | 4.5     |        | 36           | ٧      |

| Quiescent Current (Per Amplifier) |                                                       |         | 750    | 800          |         | 750    | 800          | μΑ     |

| Over Temperature                  | $T = -40^{\circ}C \text{ to } +85^{\circ}C$           |         | 850    | 900          |         | 850    | 900          | μΑ     |

| TEMPERATURE RANGE                 |                                                       |         |        |              |         |        |              |        |

| For Specified Performance         |                                                       | -40     |        | +85          | -40     |        | +85          | °C     |

| Operational <sup>6</sup>          |                                                       | -40     |        | +125         | -40     |        | +125         | °C     |

$<sup>^{1}</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 k $\Omega$ .

<sup>&</sup>lt;sup>2</sup> Refers to the differential configuration shown in Figure 64.

<sup>&</sup>lt;sup>3</sup> Refer to Figure 15 and Figure 16 for the relationship between input current and temperature.

<sup>&</sup>lt;sup>4</sup> Differential and common-mode impedance can be calculated from the pin impedance:  $Z_{DIFF} = 2(Z_{PIN})$ ;  $Z_{CM} = Z_{PIN}/2$ . <sup>5</sup> The AD8224 can operate up to a diode drop below the negative supply, but the bias current increases sharply. The input voltage range reflects the maximum

allowable voltage where the input bias current is within the specification.

The AD8224 is characterized from -40°C to +125°C. See the Typical Performance Characteristics section for expected operation in that temperature range.

$V_S + = 5 \text{ V}, V_{S^-} = 0 \text{ V}, V_{REF} = 2.5 \text{ V}, T_A = 25 ^{\circ}\text{C}, G = 1, R_L = 2 \text{ k}\Omega^1, \text{ unless otherwise noted. Table 6 displays the specifications for the } S_{S^-} = 10 \text{ N}, S_{S^-} =$ dynamic performance of each individual instrumentation amplifier.

Table 6. Dynamic Performance of Each Individual Amplifier—Single-Ended Output Configuration, V<sub>S</sub> = +5 V

|                              | Test Conditions/                | A Grade |      | B Grade |     |      |     |      |

|------------------------------|---------------------------------|---------|------|---------|-----|------|-----|------|

| Parameter                    | Comments                        | Min     | Тур  | Max     | Min | Тур  | Max | Unit |

| DYNAMIC RESPONSE             |                                 |         |      |         |     |      |     |      |

| Small Signal Bandwidth –3 dB |                                 |         |      |         |     |      |     |      |

| G = 1                        |                                 |         | 1500 |         |     | 1500 |     | kHz  |

| G = 10                       |                                 |         | 800  |         |     | 800  |     | kHz  |

| G = 100                      |                                 |         | 120  |         |     | 120  |     | kHz  |

| G=1000                       |                                 |         | 14   |         |     | 14   |     | kHz  |

| Settling Time 0.01%          |                                 |         |      |         |     |      |     |      |

| G = 1                        | $\Delta V_0 = 3 \text{ V step}$ |         | 2.5  |         |     | 2.5  |     | μs   |

| G = 10                       | $\Delta V_0 = 4 V \text{ step}$ |         | 2.5  |         |     | 2.5  |     | μs   |

| G = 100                      | $\Delta V_0 = 4 V \text{ step}$ |         | 7.5  |         |     | 7.5  |     | μs   |

| G=1000                       | $\Delta V_0 = 4 V \text{ step}$ |         | 60   |         |     | 60   |     | μs   |

| Settling Time 0.001%         |                                 |         |      |         |     |      |     |      |

| G = 1                        | $\Delta V_0 = 3 V \text{ step}$ |         | 3.5  |         |     | 3.5  |     | μs   |

| G = 10                       | $\Delta V_0 = 4 V \text{ step}$ |         | 3.5  |         |     | 3.5  |     | μs   |

| G = 100                      | $\Delta V_0 = 4 V \text{ step}$ |         | 8.5  |         |     | 8.5  |     | μs   |

| G =1000                      | $\Delta V_0 = 4 V step$         |         | 75   |         |     | 75   |     | μs   |

| Slew Rate                    |                                 |         |      |         |     |      |     |      |

| G = 1 to 100                 |                                 | 2       |      |         | 2   |      |     | V/µs |

$<sup>^{1}</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 kΩ.

$V_S + = 5 \text{ V}, V_{S^-} = 0 \text{ V}, V_{REF} = 2.5 \text{ V}, T_A = 25 ^{\circ}\text{C}, G = 1, R_L = 2 \text{ k}\Omega^1$  unless otherwise noted. Table 7 displays the specifications for the dynamic performance of both amplifiers when used in the differential output configuration shown in Figure 64.

Table 7. Dynamic Performance of Both Amplifiers—Differential Output Configuration<sup>2</sup>, VS = +5 V

|                              |                                   | A Grade |      |     | B Grade |      |     |      |

|------------------------------|-----------------------------------|---------|------|-----|---------|------|-----|------|

| Parameter                    | Test Conditions/Comments          | Min     | Тур  | Max | Min     | Тур  | Max | Unit |

| DYNAMIC RESPONSE             |                                   |         |      |     |         |      |     |      |

| Small Signal Bandwidth –3 dB |                                   |         |      |     |         |      |     |      |

| G = 1                        |                                   |         | 1500 |     |         | 1500 |     | kHz  |

| G = 10                       |                                   |         | 800  |     |         | 800  |     | kHz  |

| G = 100                      |                                   |         | 120  |     |         | 120  |     | kHz  |

| G=1000                       |                                   |         | 14   |     |         | 14   |     | kHz  |

| Settling Time 0.01%          |                                   |         |      |     |         |      |     |      |

| G = 1                        | $\Delta V_0 = 3 V \text{ step}$   |         | 2.5  |     |         | 2.5  |     | μs   |

| G = 10                       | $\Delta V_0 = 4 V \text{ step}$   |         | 2.5  |     |         | 2.5  |     | μs   |

| G = 100                      | $\Delta V_0 = 4 V \text{ step}$   |         | 7.5  |     |         | 7.5  |     | μs   |

| G =1000                      | $\Delta V_0 = 4 V \text{ step}$   |         | 60   |     |         | 60   |     | μs   |

| Settling Time 0.001%         |                                   |         |      |     |         |      |     |      |

| G = 1                        | $\Delta V_0 = 3 V \text{ step}$   |         | 3.5  |     |         | 3.5  |     | μs   |

| G = 10                       | $\Delta V_0 = 4 V \text{ step}$   |         | 3.5  |     |         | 3.5  |     | μs   |

| G = 100                      | $\Delta V_{O} = 4 V \text{ step}$ |         | 8.5  |     |         | 8.5  |     | μs   |

| G=1000                       | $\Delta V_{O} = 4 V \text{ step}$ |         | 75   |     |         | 75   |     | μs   |

| Slew Rate                    |                                   |         |      |     |         |      |     |      |

| G = 1 to 100                 |                                   | 2       |      |     | 2       |      |     | V/µs |

$<sup>^{1}</sup>$  When the output sinks more than 4 mA, use a 47 pF capacitor in parallel with the load to prevent ringing. Otherwise, use a larger load, such as 10 kΩ.  $^{2}$  Refers to the differential configuration shown in Figure 64.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 8.

|  | Parameter                                | Rating                  |  |  |  |  |

|--|------------------------------------------|-------------------------|--|--|--|--|

|  | Supply Voltage                           | ±18 V                   |  |  |  |  |

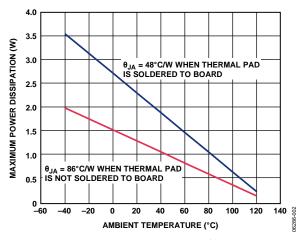

|  | Power Dissipation                        | See Figure 2            |  |  |  |  |

|  | Output Short-Circuit Current             | Indefinite <sup>1</sup> |  |  |  |  |

|  | Input Voltage (Common Mode)              | $\pm V_{S}$             |  |  |  |  |

|  | Differential Input Voltage               | $\pm V_{S}$             |  |  |  |  |

|  | Storage Temperature Range                | −65°C to +130°C         |  |  |  |  |

|  | Operating Temperature Range <sup>2</sup> | −40°C to +125°C         |  |  |  |  |

|  | Lead Temperature (Soldering, 10 sec)     | 300°C                   |  |  |  |  |

|  | Junction Temperature                     | 130°C                   |  |  |  |  |

|  | Package Glass Transition Temperature     | 130°C                   |  |  |  |  |

|  | ESD (Human Body Model)                   | 4 kV                    |  |  |  |  |

|  | ESD (Charge Device Model)                | 1 kV                    |  |  |  |  |

|  | ESD (Machine Model)                      | 0.4 kV                  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> Assumes the load is referenced to midsupply.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Table 9.

| Exposed Pad Package                         | $\theta_{JA}$ | Unit |

|---------------------------------------------|---------------|------|

| CP-16-26: LFCSP, EPAD Soldered to Board     | 48            | °C/W |

| CP-16-26: LFCSP, EPAD Not Soldered to Board | 86            | °C/W |

Table 10.

| Hidden Paddle Package | $\theta_{JA}$ | Unit |

|-----------------------|---------------|------|

| CP-16-19: LFCSP       | 86            | °C/W |

The  $\theta_{JA}$  values in Table 9 and Table 10 assume a 4-layer JEDEC standard board. If the thermal pad is soldered to the board, it is also assumed it is connected to a plane.  $\theta_{JC}$  at the exposed pad is 4.4°C/W.

#### **Maximum Power Dissipation**

The maximum safe power dissipation for the AD8224 is limited by the associated rise in junction temperature ( $T_J$ ) on the die. At approximately 130°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a temperature of 130°C for an extended period can result in a loss of functionality. Figure 2 shows the maximum safe power dissipation in the package vs. the ambient temperature for the LFCSP on a 4-layer JEDEC standard board.

Figure 2. Maximum Power Dissipation vs. Ambient Temperature

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  Temperature for specified performance is  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . For performance to 125°C, see the Typical Performance Characteristics section.

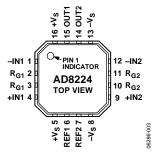

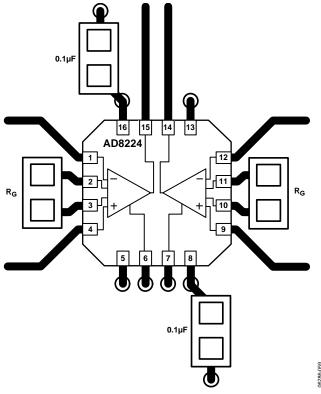

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. 16-Lead LFCSP Pin Configuration with Hidden Paddle

**Table 11. Pin Function Descriptions**

| Pin Number | Mnemonic        | Description                                         |

|------------|-----------------|-----------------------------------------------------|

| 1          | -IN1            | Negative Input Instrumentation Amplifier (In-Amp) 1 |

| 2          | R <sub>G1</sub> | Gain Resistor In-Amp 1                              |

| 3          | R <sub>G1</sub> | Gain Resistor In-Amp 1                              |

| 4          | +IN1            | Positive Input In-Amp 1                             |

| 5          | +V <sub>s</sub> | Positive Supply                                     |

| 6          | REF1            | Reference Adjust In-Amp 1                           |

| 7          | REF2            | Reference Adjust In-Amp 2                           |

| 8          | $-V_s$          | Negative Supply                                     |

| 9          | +IN2            | Positive Input In-Amp 2                             |

| 10         | R <sub>G2</sub> | Gain Resistor In-Amp 2                              |

| 11         | R <sub>G2</sub> | Gain Resistor In-Amp 2                              |

| 12         | -IN2            | Negative Input In-Amp 2                             |

| 13         | $-V_s$          | Negative Supply                                     |

| 14         | OUT2            | Output In-Amp 2                                     |

| 15         | OUT1            | Output In-Amp 1                                     |

| 16         | +V <sub>s</sub> | Positive Supply                                     |

NOTES

1. THE EXPOSED THERMAL PAD IS CONNECTED INTERNALLY

TO +V<sub>S</sub>. THE PAD CAN EITHER BE LEFT UNCONNECTED OR

CONNECTED TO THE POSITIVE SUPPLY RAIL.

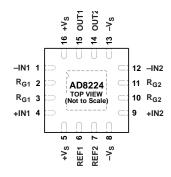

Figure 4. 16-Lead LFCSP Pin Configuration with Exposed Pad

**Table 12. Pin Function Descriptions**

| Pin Number | Mnemonic        | Description                                                                                                                                               |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | -IN1            | Negative Input In-Amp 1.                                                                                                                                  |

| 2          | R <sub>G1</sub> | Gain Resistor In-Amp 1.                                                                                                                                   |

| 3          | R <sub>G1</sub> | Gain Resistor In-Amp 1.                                                                                                                                   |

| 4          | +IN1            | Positive Input In-Amp 1.                                                                                                                                  |

| 5          | +V <sub>s</sub> | Positive Supply.                                                                                                                                          |

| 6          | REF1            | Reference Adjust In-Amp 1.                                                                                                                                |

| 7          | REF2            | Reference Adjust In-Amp 2.                                                                                                                                |

| 8          | $-V_s$          | Negative Supply.                                                                                                                                          |

| 9          | +IN2            | Positive Input In-Amp 2.                                                                                                                                  |

| 10         | R <sub>G2</sub> | Gain Resistor In-Amp 2.                                                                                                                                   |

| 11         | R <sub>G2</sub> | Gain Resistor In-Amp 2.                                                                                                                                   |

| 12         | -IN2            | Negative Input In-Amp 2.                                                                                                                                  |

| 13         | $-V_s$          | Negative Supply.                                                                                                                                          |

| 14         | OUT2            | Output In-Amp 2.                                                                                                                                          |

| 15         | OUT1            | Output In-Amp 1.                                                                                                                                          |

| 16         | +V <sub>s</sub> | Positive Supply.                                                                                                                                          |

|            | EPAD            | Exposed Pad. The exposed thermal pad is connected internally to $+V_s$ . The pad can either be left unconnected or connected to the positive supply rail. |

## TYPICAL PERFORMANCE CHARACTERISTICS

25°C,  $V_S = \pm 15$  V,  $R_L = 10$  k $\Omega$ , unless otherwise noted.

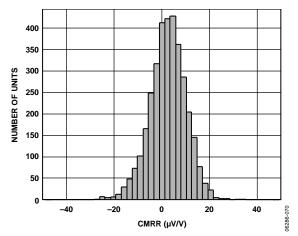

Figure 5. Typical Distribution of CMRR (G = 1)

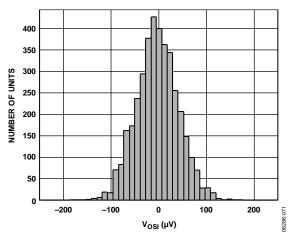

Figure 6. Typical Distribution of Input Offset Voltage

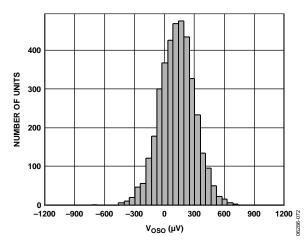

Figure 7. Typical Distribution of Output Offset Voltage

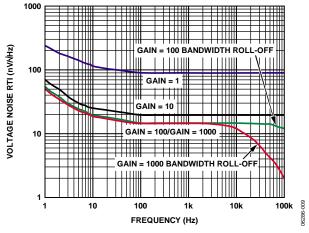

Figure 8. Voltage Spectral Density vs. Frequency

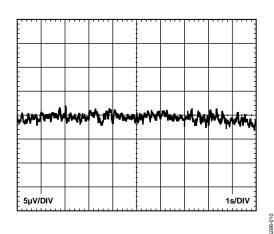

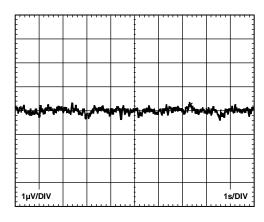

Figure 9. 0.1 Hz to 10 Hz RTI Voltage Noise (G = 1)

Figure 10. 0.1 Hz to 10 Hz RTI Voltage Noise (G = 1000)

06286-011

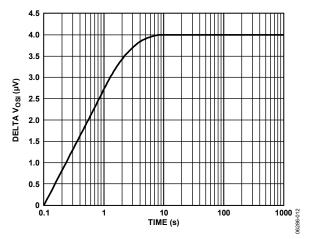

Figure 11. Change in Input Offset Voltage vs. Warmup Time

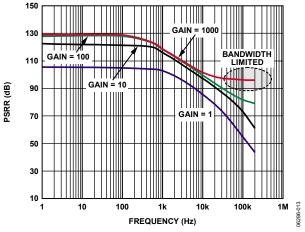

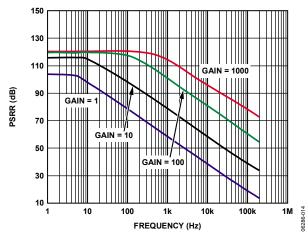

Figure 12. Positive PSRR vs. Frequency, RTI

Figure 13. Negative PSRR vs. Frequency, RTI

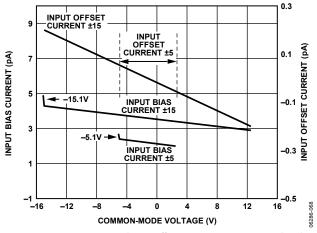

Figure 14. Input Bias Current and Input Offset Current vs. Common-Mode Voltage

Figure 15. Input Bias Current and Offset Current vs. Temperature,  $V_S = \pm 15 \ V, V_{REF} = 0 \ V$

Figure 16. Input Bias Current and Offset Current vs. Temperature,  $V_S = 5 \ V$ ,  $V_{REF} = 2.5 \ V$

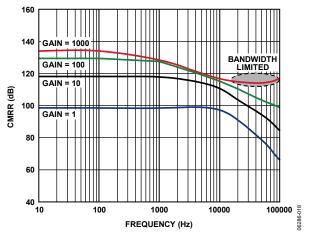

Figure 17. CMRR vs. Frequency

Figure 18. CMRR vs. Frequency, 1 k $\Omega$  Source Imbalance

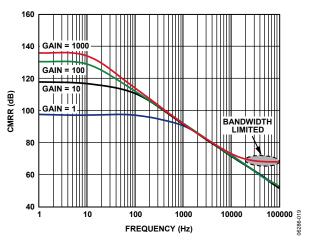

Figure 19. Change in CMRR vs. Temperature, G = 1

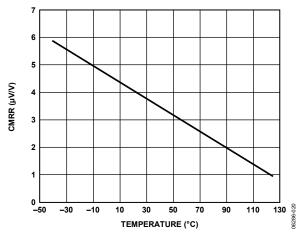

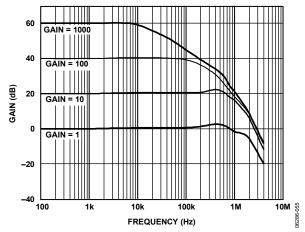

Figure 20. Gain vs. Frequency

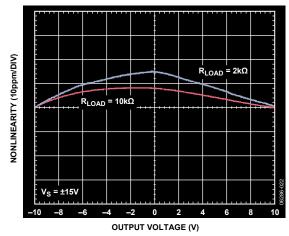

Figure 21. Gain Nonlinearity, G = 1

Figure 22. Gain Nonlinearity, G = 10

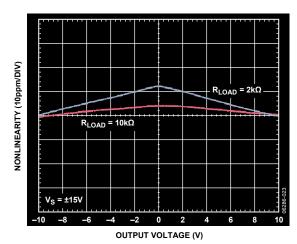

Figure 23. Gain Nonlinearity, G = 100

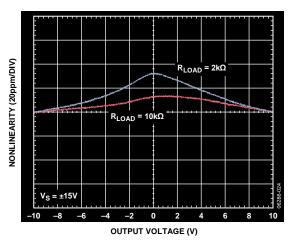

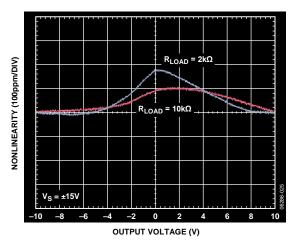

Figure 24. Gain Nonlinearity, G = 1000

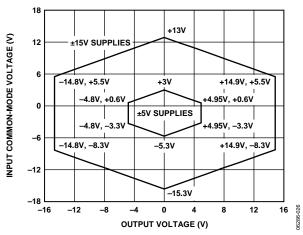

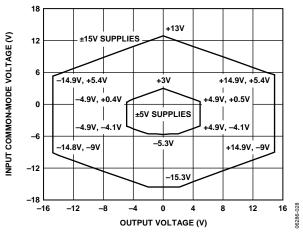

Figure 25. Input Common-Mode Voltage Range vs. Output Voltage, G=1,  $V_{\it REF}=0$  V

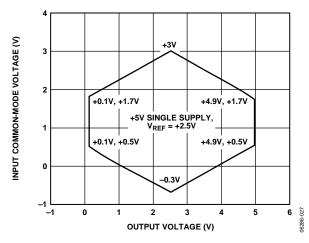

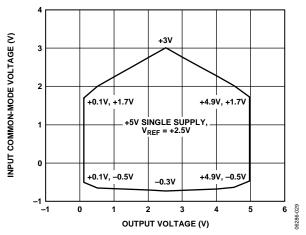

Figure 26. Input Common-Mode Voltage Range vs. Output Voltage, G = 1,  $V_S = 5$  V,  $V_{REF} = 2.5$  V

Figure 27. Input Common-Mode Voltage Range vs. Output Voltage, G = 100,  $V_{RFF} = 0$  V

Figure 28. Input Common-Mode Voltage Range vs. Output Voltage, G = 100,  $V_S = 5$  V,  $V_{REF} = 2.5$  V

Figure 29. Input Voltage Limit vs. Supply Voltage, G = 1,  $V_{REF} = 0$  V

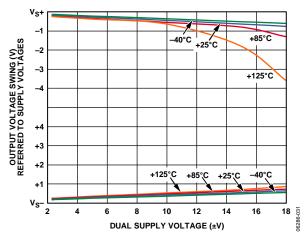

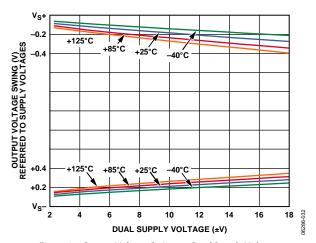

Figure 30. Output Voltage Swing vs. Dual Supply Voltage,  $R_{LOAD}=2~k\Omega,~G=10,V_{REF}=0~V$

Figure 31. Output Voltage Swing vs. Dual Supply Voltage,  $R_{LOAD} = 10 \text{ k}\Omega$ , G = 10,  $V_{REF} = 0 \text{ V}$

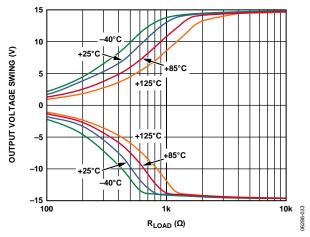

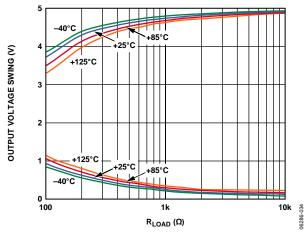

Figure 32. Output Voltage Swing vs. Load Resistance,  $V_S = \pm 15 \text{ V}$ ,  $V_{REF} = 0 \text{ V}$

Figure 33. Output Voltage Swing vs. Load Resistance,  $V_S = 5 V$ ,  $V_{REF} = 2.5 V$

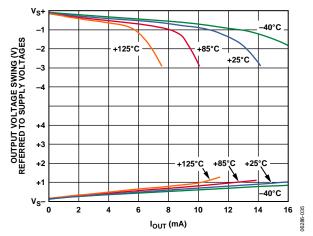

Figure 34. Output Voltage Swing vs. Output Current,  $V_S = \pm 15 \text{ V}$ ,  $V_{REF} = 0 \text{ V}$

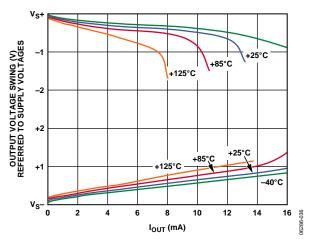

Figure 35. Output Voltage Swing vs. Output Current,  $V_S = 5 V$ ,  $V_{REF} = 2.5 V$

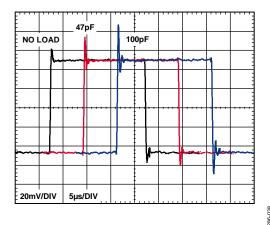

Figure 36. Small Signal Pulse Response for Various Capacitive Loads,  $V_S = \pm 15 \text{ V}, V_{REF} = 0 \text{ V}$

Figure 37. Small Signal Pulse Response for Various Capacitive Loads,  $V_S = 5 \ V, \ V_{REF} = 2.5 \ V$

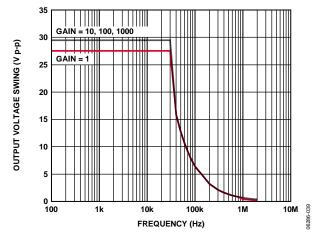

Figure 38. Output Voltage Swing vs. Large Signal Frequency Response

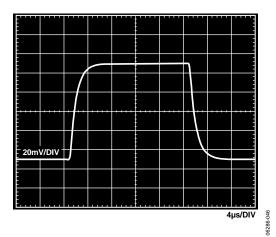

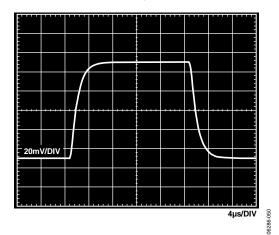

Figure 39. Large Signal Pulse Response and Settle Time, G = 1,  $R_{LOAD}=10~k\Omega,~V_S=\pm15~V,~V_{REF}=0~V$

Figure 40. Large Signal Pulse Response and Settle Time, G=10,  $R_{LOAD}=10~k\Omega,~V_S=\pm15~V,~V_{REF}=0~V$

5286-041

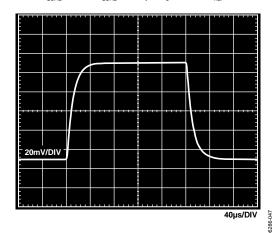

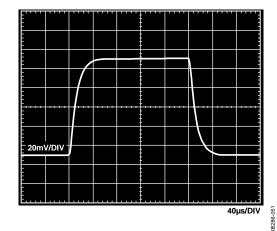

Figure 41. Large Signal Pulse Response and Settle Time, G=100,  $R_{\rm LOAD}=10$  k $\Omega$ ,  $V_{\rm S}=\pm15$  V,  $V_{\rm REF}=0$  V

Figure 42. Large Signal Pulse Response and Settle Time, G = 1000,  $R_{LOAD}=10~k\Omega,~V_S=\pm15~V,~V_{REF}=0~V$

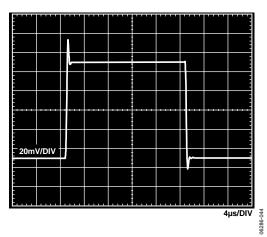

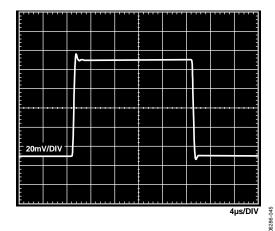

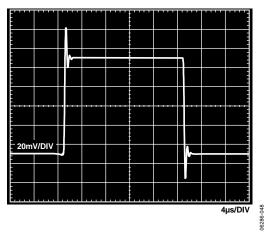

Figure 43. Small Signal Pulse Response,  $G=1, R_{LOAD}=2~k\Omega, C_{LOAD}=100~pF, V_S=\pm15~V, V_{REF}=0~V$

Figure 44. Small Signal Pulse Response, G=10,  $R_{LOAD}=2$  k $\Omega$ ,  $C_{LOAD}=100$  pF,  $V_S=\pm15$  V,  $V_{REF}=0$  V

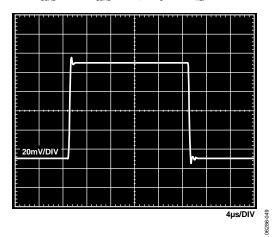

Figure 45. Small Signal Pulse Response, G=100,  $R_{LOAD}=2$  k $\Omega$ ,  $C_{LOAD}=100$  pF,  $V_S=\pm15$  V,  $V_{REF}=0$  V

Figure 46. Small Signal Pulse Response,  $G=1000, R_{LOAD}=2~k\Omega, C_{LOAD}=100~pF, V_S=\pm15~V, V_{REF}=0~V$

Figure 47. Small Signal Pulse Response, G=1,  $R_{LOAD}=2$  k $\Omega$ ,  $C_{LOAD}=100$  pF,  $V_S=5$  V,  $V_{REF}=2.5$  V

Figure 48. Small Signal Pulse Response, G = 10,  $R_{LOAD} = 2 k\Omega$ ,  $C_{LOAD} = 100 pF$ ,  $V_S = 5 V$ ,  $V_{REF} = 2.5 V$

Figure 49. Small Signal Pulse Response,  $G=100, R_{LOAD}=2\,k\Omega, C_{LOAD}=100\,p\text{F}, V_{\text{S}}=5\,\text{V}, V_{\text{REF}}=2.5\,\text{V}$

Figure 50. Small Signal Pulse Response, G = 1000,  $R_{LOAD}$  = 2 k $\Omega$ ,  $C_{LOAD}$  = 100 pF,  $V_{S}$  = 5 V,  $V_{REF}$  = 2.5 V

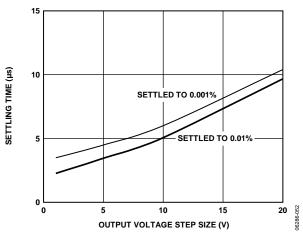

Figure 51. Settling Time vs. Output Voltage Step Size,  $(G = 1) \pm 15 \text{ V}$ ,  $V_{REF} = 0 \text{ V}$

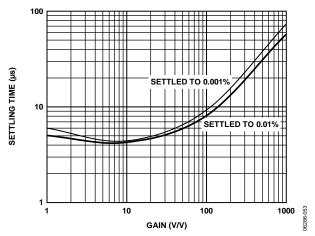

Figure 52. Settling Time vs. Gain for a 10 V Step,  $V_S = \pm 15 \text{ V}$ ,  $V_{REF} = 0 \text{ V}$

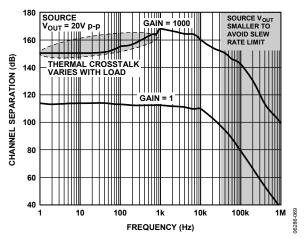

Figure 53. Channel Separation vs. Frequency,  $R_{LOAD} = 2 \, k\Omega$ , Source Channel at G = 1

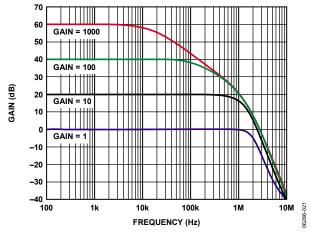

Figure 54. Differential Output Configuration: Gain vs. Frequency

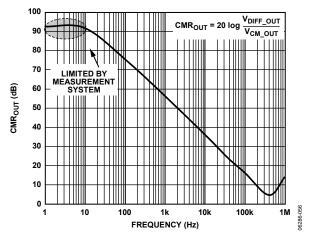

Figure 55. Differential Output Configuration: Common-Mode Output (CMR<sub>OUT</sub>) vs. Frequency

### THEORY OF OPERATION

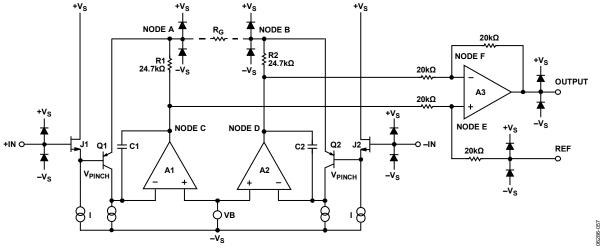

Figure 56. Simplified Schematic

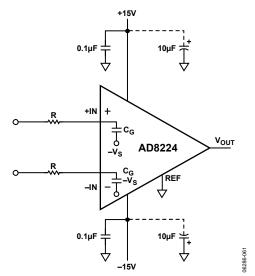

The AD8224 is a JFET input, monolithic instrumentation amplifier based on the classic three op amp topology (see Figure 56). Input Transistor J1 and Input Transistor J2 are biased at a fixed current so that any input signal forces the output voltages of A1 and A2 to change accordingly. The input signal creates a current through  $R_{\rm G}$  that flows in R1 and R2 such that the outputs of A1 and A2 provide the correct, gained signal. Topologically, J1, A1, and R1 and J2, A2, and R2 can be viewed as precision current feedback amplifiers. The common-mode voltage and amplified differential signal from A1 and A2 are applied to a difference amplifier that rejects the common-mode voltage but amplifies the differential signal. The difference amplifier employs 20  $k\Omega$  laser trimmed resistors that result in an in-amp with a gain error of less than 0.04%. New trim techniques were developed to ensure that the CMRR exceeds 86 dB (G=1).

Using JFET transistors, the AD8224 offers an extremely high input impedance, extremely low bias currents of 10 pA maximum, low offset current of 0.6 pA maximum, and no input bias current noise. In addition, input offset is less than 175  $\mu V$  and drift is less than 5  $\mu V/^{\circ}C$ . Ease of use and robustness were considered. A common problem for instrumentation amplifiers is that at high gains, when the input is overdriven, an excessive milliampere input bias current can result, and the output can undergo phase reversal.

Overdriving the input at high gains refers to when the input signal is within the supply voltages but the amplifier cannot output the gained signal. For example, at a gain of 100, driving the amplifier with 10 V on  $\pm 15$  V constitutes overdriving the inputs because the amplifier cannot output 100 V.

The AD8224 has none of these problems; its input bias current is limited to less than 10  $\mu$ A, and the output does not phase reverse under overdrive fault conditions.

The AD8224 has extremely low load induced nonlinearity. All amplifiers that comprise the AD8224 have rail-to-rail output capability for enhanced dynamic range. The input of the AD8224 can amplify signals with wide common-mode voltages even slightly lower than the negative supply rail. The AD8224 operates over a wide supply voltage range. It can operate from either a single  $+4.5~\rm V$  to  $+36~\rm V$  supply or a dual  $\pm 2.25~\rm V$  to  $\pm 18~\rm V$ . The transfer function of the AD8224 is

$$G = 1 + \frac{49.4 \text{ k}\Omega}{R_C}$$

Users can easily and accurately set the gain using a single, standard resistor. Because the input amplifiers employ a current feedback architecture, the AD8224 gain bandwidth product increases with gain, resulting in a system that does not experience as much bandwidth loss as voltage feedback architectures at higher gains.

#### **GAIN SELECTION**

Placing a resistor across the R<sub>G</sub> terminals sets the gain of the AD8224. This is calculated by referring to Table 13 or by using the following gain equation

$$R_G = \frac{49.4 \text{ k}\Omega}{G - 1}$$

| 1% Standard Table Value of R <sub>G</sub> (Ω) | Calculated Gain |

|-----------------------------------------------|-----------------|

| 49.9 k                                        | 1.990           |

| 12.4 k                                        | 4.984           |

| 5.49 k                                        | 9.998           |

| 2.61 k                                        | 19.93           |

| 1.00 k                                        | 50.40           |

| 499                                           | 100.0           |

| 249                                           | 199.4           |

| 100                                           | 495.0           |

| 49.9                                          | 991.0           |

The AD8224 defaults to G=1 when no gain resistor is used. The tolerance and gain drift of the  $R_G$  resistor should be added to the AD8224 specifications to determine the total gain accuracy of the system. When the gain resistor is not used, gain error and gain drift are kept to a minimum.

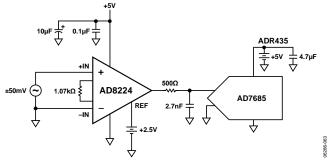

#### REFERENCE TERMINAL

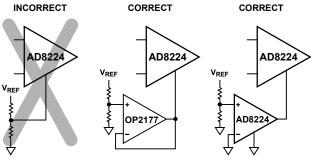

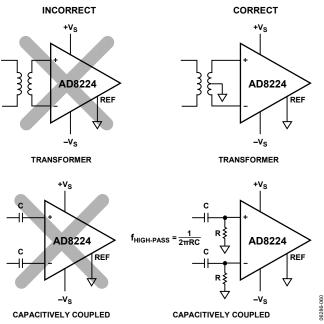

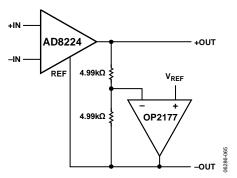

The output voltage of the AD8224 is developed with respect to the potential on the reference terminal. This is useful when the output signal needs to be offset to a precise midsupply level. For example, a voltage source can be tied to the REF1 pin or the REF2 pin to level-shift the output so that the AD8224 can drive a single-supply ADC. Pin REFx is protected with ESD diodes and should not exceed either  $+V_S$  or  $-V_S$  by more than 0.5 V.

For best performance, source impedance to the REF terminal should be kept below 1  $\Omega.$  As shown in Figure 56, the reference terminal, REF, is at one end of a 20  $k\Omega$  resistor. Additional impedance at the REF terminal adds to this 20  $k\Omega$  resistor and results in amplification of the signal connected to the positive input. The amplification from the additional  $R_{\text{REF}}$  can be computed by

$$\frac{2\left(20 \text{ k}\Omega + R_{REF}\right)}{40 \text{ k}\Omega + R_{REF}}$$

Only the positive signal path is amplified; the negative path is unaffected. This uneven amplification degrades the CMRR of the amplifier.

Figure 57. Driving the Reference Pin

#### **LAYOUT**

The AD8224 is a high precision device. To ensure optimum performance at the PCB level, care must be taken in the design of the board layout. The AD8224 pinout is arranged in a logical manner to aid in this task.

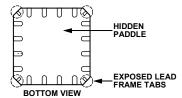

#### **Package Considerations**