### DESCRIPTION

The FX7388 is a high speed power MOSFET and IGBT driver with three independent high and low side referenced output channels for 3-phase gate driver. Built-in deadtime protection and Shoot-through protection that prevent half-bridge breakdown. The UVLO circuits prevent malfunction when VCC and VBS are lower than the specified threshold voltage. 600V high-voltage process and common-mode noise canceling technique provide stable operation of high-side drivers under high-dv/dt noise circumstances.

### **APPLICATION**

- 3-phase Motor Inverter Driver

- Air Condition

- Washing Machines

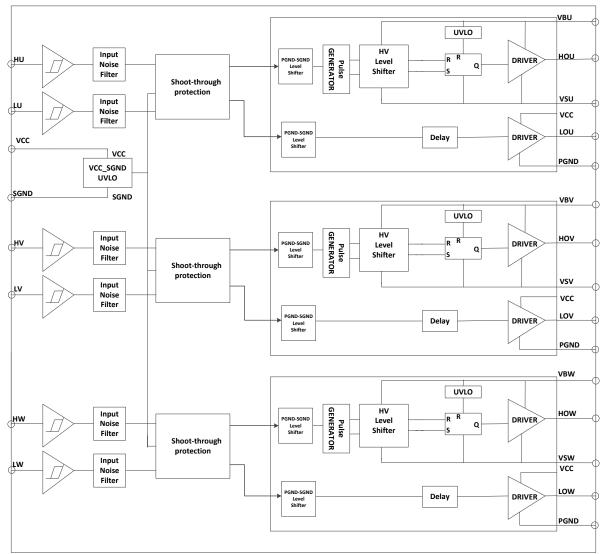

### **BLOCK DIAGRAM**

### **FEATURES**

- Integrated 600V half-bridge high side driver

- Driver up to 3-phase half-bridge gates

- Built-in deadtime control

- Shoot-through protection

- Under voltage lockout for VCC and VBS

- 3.3V, 5V, 15V input logic Compatible

- Built-in input filter

•

- -40<sup>°</sup>C to 125<sup>°</sup>C operating range

- Common-Mode dv/dt Noise Canceling Circuit

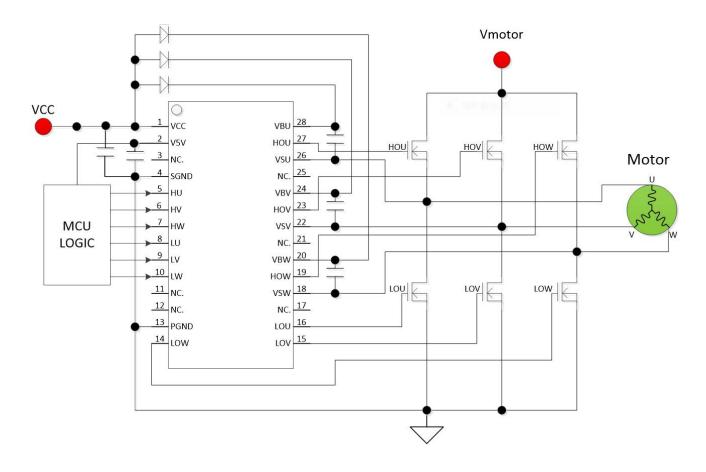

## **TYPICAL APPLICATION CIRCUIT**

### **ORDER INFORMATION**

| Valid Part Number | Package Type         | Top Code  |

|-------------------|----------------------|-----------|

| FX7388 -S         | 20 Pins, SOP, 300mil | FX7388 -S |

| FX7388-S1         | 24 Pins, SOP, 300mil | FX7388-S1 |

| FX7388-S2         | 28 Pins, SOP, 300mil | FX7388-S2 |

### PIN CONFIGURATION SOP20 AND SOP24 PACKAGE

| 0    | 20     | VCC          | VBU - |

|------|--------|--------------|-------|

| -vcc | VBU 20 | V5V          | HOU-  |

| ни   | HOU 19 | ни           | vsu-  |

| HV   | VSU 18 | HV           | NC.   |

| нw   | VBV 17 | 5 HW         | VBV   |

| - 10 | HOV 16 | <u>6</u> LU  | HOV   |

|      | VSV 15 | -7 LV        | vsv   |

|      | VBW 14 | <u>-8</u> LW | NC.   |

| GND  | HOW 13 | 9 GND        | VBW   |

| LOW  | VSW 12 | 10 LOW       | HOW   |

| LOV  | LOU 11 | 11 LOV       | vsw   |

|      |        | 12 LOU       | NC.   |

#### **PIN DESCRIPTION**

| Pin Name | Description                                             |       | Pin No. |  |  |

|----------|---------------------------------------------------------|-------|---------|--|--|

| Pin Name | Description                                             | SOP20 | SOP24   |  |  |

| VCC      | Logic and low-side gate drivers power supply voltage    | 1     | 1       |  |  |

| V5V      | 5V LDO output                                           |       | 2       |  |  |

| HU       | Logic input for high-side gate U-phase driver           | 2     | 3       |  |  |

| HV       | Logic input for high-side gate V-phase driver           | 3     | 4       |  |  |

| HW       | Logic input for high-side gate W-phase driver           | 4     | 5       |  |  |

| LU       | Logic input for low-side gate U-phase driver            | 5     | 6       |  |  |

| LV       | Logic input for low-side gate V-phase driver            | 6     | 7       |  |  |

| LW       | Logic input for low-side gate W-phase driver            | 7     | 8       |  |  |

| GND      | Logic ground and low-side gate drivers ground           | 8     | 9       |  |  |

| LOW      | Low-side gate driver W-phase output                     | 9     | 10      |  |  |

| LOV      | Low-side gate driver V-phase output                     | 10    | 11      |  |  |

| LOU      | Low-side gate driver U-phase output                     | 11    | 12      |  |  |

| NC.      | Not Connected                                           |       | 13      |  |  |

| VSW      | High-side driver W-phase floating supply offset voltage | 12    | 14      |  |  |

| HOW      | High-side driver W-phase gate driver output             | 13    | 15      |  |  |

| VBW      | High-side driver W-phase floating supply                | 14    | 16      |  |  |

| NC.      | Not Connected                                           |       | 17      |  |  |

| VSV      | High-side driver V-phase floating supply offset voltage | 15    | 18      |  |  |

| HOV      | High-side driver V-phase gate driver output             | 16    | 19      |  |  |

| VBV      | High-side driver V-phase floating supply                | 17    | 20      |  |  |

| NC.      | Not Connected                                           |       | 21      |  |  |

| VSU      | High-side driver U-phase floating supply offset voltage | 18    | 22      |  |  |

| HOU      | High-side driver U-phase gate driver output             | 19    | 23      |  |  |

| VBU      | High-side driver U-phase floating supply                | 20    | 24      |  |  |

#### SOP28 PACKAGE

| 0       |        |

|---------|--------|

| 1 vcc   | VBU 28 |

| 2 V5V   | HOU 27 |

| 3 NC.   | VSU 26 |

| 4 SGND  | NC. 25 |

| 5 HU    | VBV 24 |

| 6 HV    | HOV 23 |

| 7 HW    | V5V 22 |

| 8 10    | NC. 21 |

| 9 LV    | VBW 20 |

| 10 LW   | HOW 19 |

| 11 NC.  | vsw 18 |

| 12 NC.  | NC. 17 |

| 13 PGND | LOU 16 |

| 14 LOW  | LOV 15 |

#### **PIN DESCRIPTION**

| Pin Name | Description                                             | Pin No. |

|----------|---------------------------------------------------------|---------|

| VCC      | Logic and low-side gate drivers power supply voltage    | 1       |

| V5V      | 5V LDO output                                           | 2       |

| NC.      | Not Connected                                           | 3       |

| SGND     | Logic ground                                            | 4       |

| HU       | Logic input for high-side gate U-phase driver           | 5       |

| HV       | Logic input for high-side gate V-phase driver           | 6       |

| HW       | Logic input for high-side gate W-phase driver           | 7       |

| LU       | Logic input for low-side gate U-phase driver            | 8       |

| LV       | Logic input for low-side gate V-phase driver            | 9       |

| LW       | Logic input for low-side gate W-phase driver            | 10      |

| NC.      | Not Connected                                           | 11      |

| NC.      | Not Connected                                           | 12      |

| PGND     | Low-side gate drivers ground                            | 13      |

| LOW      | Low-side gate driver W-phase output                     | 14      |

| LOV      | Low-side gate driver V-phase output                     | 15      |

| LOU      | Low-side gate driver U-phase output                     | 16      |

| NC.      | Not Connected                                           | 17      |

| VSW      | High-side driver W-phase floating supply offset voltage | 18      |

| HOW      | High-side driver W-phase gate driver output             | 19      |

| VBW      | High-side driver W-phase floating supply                | 20      |

| NC.      | Not Connected                                           | 21      |

| VSV      | High-side driver V-phase floating supply offset voltage | 22      |

| HOV      | High-side driver V-phase gate driver output             | 23      |

| VBV      | High-side driver V-phase floating supply                | 24      |

| NC.      | Not Connected                                           | 25      |

| VSU      | High-side driver U-phase floating supply offset voltage | 26      |

| HOU      | High-side driver U-phase gate driver output             | 27      |

| VBU      | High-side driver U-phase floating supply                | 28      |

## **FUNCTION DESCRIPTION**

#### LOW SIDE POWER SUPPLY (VCC, GND (SGND, PGND))

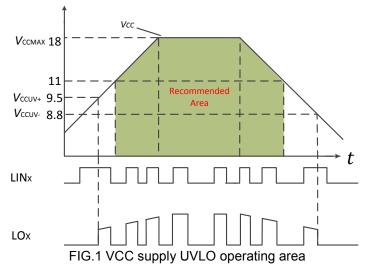

VCC is the low side supply and it provides power to both input logic and low side output power stage. In FX7388-S2, input logic is referenced to SGND as well as the under-voltage detection circuit. Output power stage is referenced to PGND. PGND ground is floating respect to SGND ground with a recommended range of operation of +/-5V, which guarantees enough margin of gate to source voltage, V<sub>GS</sub>, to driver power devices such as power MOSFET. The built-in under-voltage lockout circuit enables the device to operate at sufficient power on when a typical VCC supply voltage higher than  $V_{CCUV+}$  =9.5 is present, shown as FIG1. The IC shuts down all the gate drivers outputs, when the VCC supply voltage is below  $V_{CCUV-}$  =8.8 V, shown as FIG1. This prevents the external power devices from extremely low gate voltage levels during on-state and therefore from excessive power dissipation.

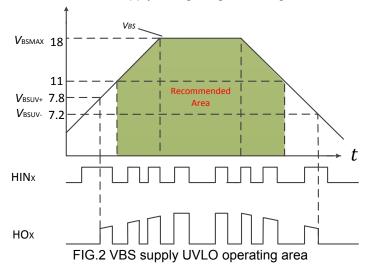

#### HIGH SIDE POWER SUPPLY (VBU-VSU, VBV-VSV, VBW-VSW)

VB to VS is the high side supply voltage. The totally high side circuitry can float with respect to SGND following the external high side power device emitter/source voltage. Due to the internally low power consumption, the whole high side circuitry can be supplied by bootstrap topology connected to VCC, and it can be powered with small bootstrap capacitors.

The device operating area as a function of the supply voltage is given in Figure 2.

### LOW SIDE AND HIGH CONTROL INPUT LOGIC (HU, V, W / LU, V, W)

The Schmitt trigger threshold of each input is designed enough low such to guarantee LSTTL and CMOS compatibility down to 3.3 V controller outputs. Input Schmitt trigger and advanced noise filter provide beneficial noise rejection to short input pulses. An internal pull-down resistor of about  $200k\Omega$  (positive logic) pre-biases each input during VCC supply start-up state. It is anyway recommended for proper work of the driver not to provide input pulse-width lower than 400ns.

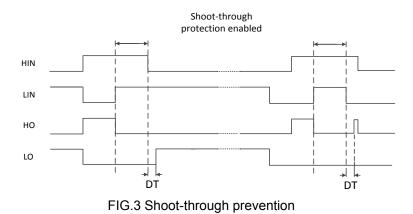

### SHOOT-THROUGH PREVENTION

The IC is equipped with shoot-through prevention circuitry (also known as cross conduction prevention circuitry). Figure 3 shows how this prevention circuitry prevents both the high- and low-side switches from conducting at the same time. During the inputs controlling high side driver and low side driver are both "high", the both driver outputs are pulled down "low" to shutdown two power devices in the same bridge.

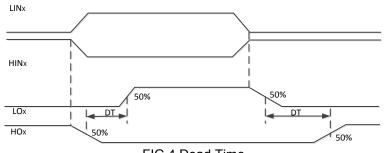

### DEAD TIME

The IC features integrated a fixed dead-time protection circuitry. The dead time feature inserts a time period (a minimum dead time) in which both the high- and low-side power switches are held off; this is done to ensure that the power switch being turned off has fully turned off before the second power switch is turned on. This minimum dead time is automatically inserted whenever the external dead time is shorter than DT; external dead times larger than DT are not modified by the gate driver. Figure 4 illustrates the dead time period and the relationship between the output gate signals.

FIG.4 Dead Time

### GATE DRIVER (HOU, V, W, LOU, V, W)

Low side and high side driver outputs are specifically designed for pulse operation and dedicated to drive the power devices such as IGBT and MOSFET. Low side outputs (i.e. LOU, V, W) are state triggered by the respective inputs, while high side outputs (i.e. HOU, V, W) are only changed at the edge of the respective inputs. In particular, after releasing from an under voltage condition of the VBS supply, a new turn-on signal (edge) is necessary to activate the respective high side output, while after releasing from a under voltage condition of the VBS supply, and under voltage condition of the VCC supply, the low side outputs can directly switch to the state of their respective inputs and don't suffer from the trouble as high side driver

## **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device or make the function abnormal. All the voltage parameters are absolute voltages referenced to IC SGND unless otherwise stated in the table.

| Parameter                            | Symbol               | Min.                     | Max.                      | Units |

|--------------------------------------|----------------------|--------------------------|---------------------------|-------|

| High-side floating supply voltage    | V <sub>B.U.V.W</sub> | -0.3                     | 600                       |       |

| High-side offset voltage             | Vs.u.v.w             | V <sub>B.U.V.W</sub> -18 | V <sub>B.U.V.W</sub> +0.3 |       |

| High-side gate driver output voltage | Vho.u.v.w            | Vs.u.v.w-0.3             | V <sub>S.U.V.W</sub> +0.3 |       |

| Low-side gate driver output voltage  | VLO.U.V.W            | PGND-0.3                 | Vcc+0.3                   | V     |

| Logic input voltage                  | Vh.u.v.w<br>Vl.u.v.w | -0.3                     | 20                        | v     |

| Low-side supply voltage              | Vcc                  | -0.3                     | 20                        |       |

| Logic gate driver return             | PGND                 | Vcc-18                   | Vcc+0.3                   |       |

| Allowable Offset Voltage Slew Rate   | dV/dt                |                          | 40                        | V/ns  |

| Junction temperature                 | TJ                   | -40                      | +125                      | C     |

| Storage temperature                  | Ts                   | -50                      | +150                      | C     |

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                       | Symbol               | Min.               | Тур. | Max.               | Units |

|-------------------------------------------------|----------------------|--------------------|------|--------------------|-------|

| Low-side supply voltage                         | Vcc                  | 11                 | -    | 18                 |       |

| High-side Floating Supply Offset Voltage(note1) | Vs.u.v.w             | V <sub>B</sub> -18 | -    | V <sub>B</sub> -11 |       |

| High-side Floating Supply Voltage               | V <sub>B.U.V.W</sub> | -8                 | -    | 600                |       |

| High-side gate driver output voltage            | VHO.U.V.W            | Vs                 | -    | VB                 | V     |

| Low-side gate driver output voltage             | VLO.U.V.W            | PGND               | -    | Vcc                | v     |

| Logic gate driver return                        | PGND                 | -3                 |      | 3                  |       |

| Logic input voltage                             | Vh.u.v.w<br>Vl.u.v.w | 0                  | -    | 5                  |       |

| IC operating Junction temperature               | TJ                   | -40                | -    | +125               | ĉ     |

Note1: For VBS=12V, normal Logic operation for Vs of -8 V to 600 V. The parameter is only guaranteed by design.

# STATIC ELECTRICAL CHARACTERISTICS

(VCC-SGND) =(VB-VS)=12V. TAMB=25°C unless otherwise specified. The VIN, VTH and IIN Parameters are reference to SGND and are applicable to all six channels. The Vo and Io parameters are referenced to respective Vs and PGND and are applicable to the respective output leads. The Vccuv parameters are referenced to SGND. The VBSUV parameters are referenced to Vs.

| Parameter                                                                     | Symbol             | Test<br>Conditions                                          | Min. | Тур. | Max. | Uni<br>t |

|-------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------|------|------|------|----------|

| Low Side Power Supply Characteristics                                         | •                  |                                                             |      |      |      |          |

| VCC quiescent current in UVLO mode                                            | Ιανος              | VH.U.V.W<br>=VL.U.V.W=0 or<br>5V,                           | 200  | 350  | 500  | μA       |

| VCC operating Vcc supply current                                              | Ivccop             | f <sub>L.U.V.W</sub> =20k,<br>f <sub>H.U.V.W</sub> =20k,    | -    | 1200 | -    | •        |

| VCC supply under-voltage positive going threshold                             | V <sub>CCUV+</sub> |                                                             | 8.0  | 9.5  | 11.0 |          |

| VCC supply under-voltage negative going threshold                             | V <sub>CCUV-</sub> |                                                             | 7.3  | 8.8  | 10.3 | V        |

| Vcc supply under-voltage lockout hysteresis                                   | V <sub>CCHYS</sub> |                                                             | -    | 0.7  | -    |          |

| High Side Floating Power Supply Characteristics                               |                    |                                                             |      |      |      |          |

| High side VBS supply under-voltage positive going threshold                   | V <sub>BSUV+</sub> |                                                             | 6.8  | 7.8  | 8.8  |          |

| High side VBS supply under-voltage negative going threshold                   | VBSUV-             |                                                             | 6.2  | 7.2  | 8.2  | V        |

| High side VBS supply under-voltage lockout<br>hysteresis                      | VBSUVHYS           |                                                             | -    | 0.6  | -    |          |

| High side VBS quiescent current in UVLO mode                                  | IQBS               | V <sub>BS</sub> =12V                                        | 35   | 54   | 75   |          |

| Offset supply leakage current                                                 | Ilk                | V <sub>B</sub> =V <sub>S</sub> =600V<br>V <sub>CC</sub> =0V | -    | -    | 1    | μA       |

| Gate Driver Output Section                                                    | •                  |                                                             |      |      |      |          |

| High Side Output High Short-Circuit Pulse Current                             | IHO+               | V <sub>HO</sub> =V <sub>S</sub> =0                          | -    | 160  | -    |          |

| High Side Output Low Short-Circuit Pulse Current                              | Іно-               | V <sub>HO</sub> =V <sub>B</sub> =12V                        | -    | 340  | -    | mA       |

| Low Side Output High Short-Circuit Pulse Current                              | ILO+               | VLO=PGND=0                                                  | -    | 160  | -    | ША       |

| Low Side Output Low Short-Circuit Pulse Current                               | ILO-               | VLO=VCC=12V                                                 | -    | 340  | -    |          |

| Allowable Negative VS Pin Voltage for HU.V.W<br>Signal Propagation to HOU.V.W | Vsn                | V <sub>BS</sub> =12V                                        | -    | -10  | -8   | V        |

| Logic Input Section                                                           |                    |                                                             |      |      |      |          |

| Logic"1" Input voltage HU.V.W and LU.V.W                                      | VIH                |                                                             | 2.8  | -    | -    |          |

| Logic"0" Input voltage HU.V.W and LU.V.W                                      | VIL                |                                                             | -    | -    | 0.8  | v        |

| Input positive going threshold                                                | VIN,TH+            |                                                             | -    | 2.0  | -    | v        |

| Input negative going threshold                                                | Vin,th-            |                                                             | -    | 1.5  | -    |          |

| Logic "1" Input bias current                                                  | l <sub>IN+</sub>   | V <sub>IN</sub> =5V                                         | -    | 25   | -    | uA       |

| Logic "0" Input bias current                                                  | I <sub>IN-</sub>   | V <sub>IN</sub> =0                                          | -    | 0    | -    | uA       |

| LDO Characteristic (Only for FX7388 -S1 and FX7                               | 388- S2)           |                                                             |      |      |      |          |

| Output Voltage                                                                | V <sub>LDO</sub>   | VCC=12V                                                     | 4.5  | 5    | 5.5  | V        |

| Output Current                                                                | I <sub>LDO</sub>   |                                                             | -    | 20   | 30   | mA       |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

(VCC-SGND) =(VB-VS)=12V, Vs.u.v.w=SGND=PGND, and Cload=1nF unless otherwise specified, TAMB=25°C.

| Parameter                            | Symbol              | Test Conditions                                                              | Min. | Тур. | Max. | Unit |

|--------------------------------------|---------------------|------------------------------------------------------------------------------|------|------|------|------|

| Turn-On propagation delay            | ton                 | V <sub>H.U.V.W</sub> or V <sub>L.U.V.W</sub> =5V,<br>V <sub>S.U.V.W</sub> =0 | 300  | 510  | 700  |      |

| Turn-Off Propagation delay           | t <sub>OFF</sub>    | VH.U.V.W OF VL.U.V.W=0,<br>Vs.U.V.W=0                                        | 300  | 570  | 700  |      |

| Turn-On Rise time                    | t <sub>R</sub>      | V <sub>H.U.V.W</sub> or V <sub>L.U.V.W</sub> =5V,<br>V <sub>S.U.V.W</sub> =0 | -    | 90   | -    |      |

| Turn-Off Fall time                   | t⊧                  | V <sub>H.U.V.W</sub> or V <sub>L.U.V.W</sub> =0,<br>V <sub>S.U.V.W</sub> =0  | -    | 40   | -    | ns   |

| Input Filtering Time                 | t <sub>FLT,IN</sub> |                                                                              | -    | 400  | -    |      |

| Dead Time                            | DT                  |                                                                              | 150  | 230  | 310  |      |

| Dead-Time Matching(All Six Channels) | MDT                 |                                                                              | -    | -    | 100  |      |

| Delay Matching(All Six Channels)     | MT                  |                                                                              | -    | -    | 150  | ]    |

| Output Pulse-Width Matching          | РМ                  | PW <sub>IN</sub> =10us,<br>PM=PW <sub>OUT</sub> -PW <sub>IN</sub>            | -    | -    | 100  |      |

# PACKAGE INFORMATION 20 PINS, SOP, 300MIL

24 PINS, SOP, 300MIL

28 Pins, SOP 300MIL