Panasonic Semiconductor Singapore

A Division of Panasonic Semiconductor Asia Pte Ltd

Company Registration No. 197803125E 22, Ang Mo Kio Industrial Park 2, Singapore 569506. Tel: 65)64818811 Fax: 65)64816486

## DOCUMENT COVER PAGE

**APPROVED**

Note: This cover page establishes the Doc No., Title and current status of the aftached to the status

| Doc No.   | SDSC-PSE-AN17827A                  | issue Levei    | Rev   | Eff Date |  |

|-----------|------------------------------------|----------------|-------|----------|--|

| DOC NO.   | 3030-1 3E-AN17027A                 | 1              | 0     | 9-Dec-05 |  |

| Doc Title | Product Specification for AN17827A | Total no. of p | ages  | 16       |  |

|           | Product Specification for ANT/02/A | excluding this | page) |          |  |

## **Revision History**

| Issue    | Rev | Eff Date  | S/N | Page | Change Details | Remarks |

|----------|-----|-----------|-----|------|----------------|---------|

| 1        | 0   | 09-Dec-05 |     |      | First issue    |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

|          |     |           |     |      |                |         |

| <u> </u> |     |           |     |      |                |         |

|          | L   |           |     |      |                |         |

| Cada Na i I (                    |        | 07           |                                 |                                                 | Teta           |              | PROVEI             | द्या ह<br>) |

|----------------------------------|--------|--------------|---------------------------------|-------------------------------------------------|----------------|--------------|--------------------|-------------|

| Code No.: (                      | J3F42  | 297          |                                 |                                                 |                | Paper<br>16  |                    | JUL         |

|                                  |        | 12           |                                 |                                                 |                |              |                    |             |

|                                  |        |              |                                 |                                                 |                | <u>*</u> )   |                    |             |

|                                  |        |              |                                 |                                                 |                |              |                    |             |

|                                  | F      | Proc         | luct S                          | Stand                                           | ard            | S            |                    |             |

|                                  |        | Part No.     |                                 | AN178                                           | 827A           |              |                    |             |

|                                  | Pack   | age Cod      | e No.                           | DIP016-P-                                       | 0300P          |              |                    |             |

| -<br>                            | x      |              |                                 |                                                 |                |              |                    |             |

|                                  |        |              |                                 | 2:<br>1:                                        |                |              |                    |             |

| 8                                |        |              |                                 |                                                 |                |              |                    |             |

|                                  |        |              | Semicondu                       | l Business Ur<br>ctor Company<br>c Industrial C | /              |              |                    |             |

|                                  | Es     | tablished by | Applied by                      | Checked by                                      | Prepared t     | у            |                    |             |

|                                  | S      | .Okada       | M.Hiramota                      | a 2 Gali                                        | 1/01           | >            |                    |             |

|                                  |        | S.Okada      | M.Hiramatsu                     | Yasuo Higuchi                                   | Iskandar       |              |                    |             |

|                                  | ÷      | (96)         |                                 |                                                 |                |              |                    |             |

| 2005-12-09                       |        | 1            | 550335-355-51-51-51-51-51-51-51 |                                                 |                |              | ****               | -           |

| Established R<br>211782700105110 | evised | L            | s                               | emiconductor Comp                               | any, Matsushit | a Electric I | ndustrial Co., Lto | J.          |

|  | Product Standar | ds A<br>EXT |  | 827A<br>D <sub>Page</sub> |  |

|--|-----------------|-------------|--|---------------------------|--|

|--|-----------------|-------------|--|---------------------------|--|

# Contents

| Overview                       | 3  |

|--------------------------------|----|

| ■ Features                     | 3  |

| Applications                   | 3  |

| Package                        | 3  |

| ■ Туре                         | 3  |

| Application Circuit Example    | 4  |

| Block Diagram                  | 5  |

| Pin Descriptions               | 6  |

| Absolute Maximum Ratings       | 7  |

| Operating Supply Voltage Range | 7  |

| Electrical Characteristics     | 8  |

| ■ Test Circuit Diagram         | 9  |

| Technical Data 10-1            | 15 |

| Usage Notes 1                  | 16 |

| ····· | Product Standards | APPRO<br>ANT<br>EXTERNAL<br>Total Pages | 827A<br>ISSUE<br>Page |

|-------|-------------------|-----------------------------------------|-----------------------|

|       |                   | 16                                      | 3                     |

# AN17827A

# A single channel BTL audio power amplifier IC

#### Overview

AN17827A is a monolithic integrated circuit designed for 2.5 W X 1 (8 $\Omega$ ) and. It is a single channel BTL IC suitable for operation in audio application.

#### Features

- Few external components no Boucherot cells (output C, R) and no negative feedback capacitors.

- . Built-in Thermal Protection circuit.

- High ripple rejection.

#### Applications

• IC for audio applications

#### Package

16 pin plastic Dual Inline Package (DIP type)

#### Type

• Silicon Monolithic Bipolar IC

2005-12-09

Revised

211782700305110

Established

|                   | APPRO            | VED  |  |

|-------------------|------------------|------|--|

|                   | EXTERNA 82798SUE |      |  |

| Product Standards | Total Pages      | Page |  |

|                   | 16               | 4    |  |

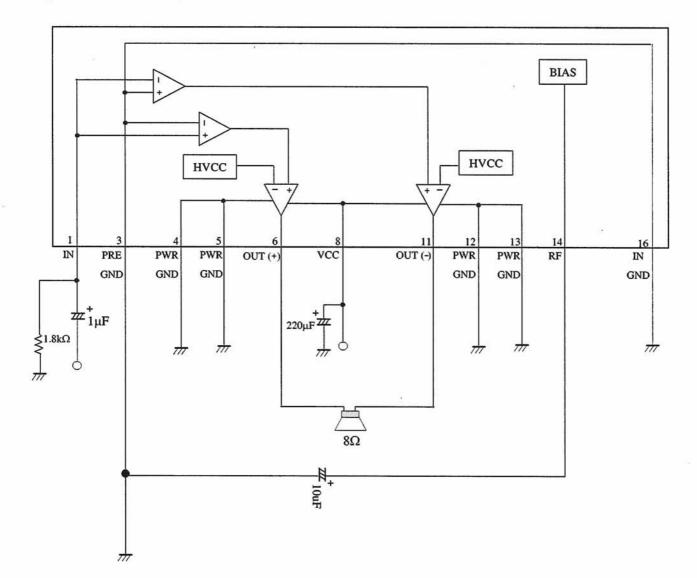

# Application Circuit Example

| 2005-12-09    |         |                                                                 |

|---------------|---------|-----------------------------------------------------------------|

| Established   | Revised |                                                                 |

| 2117827004051 | 10      | Semiconductor Company, Matsushita Electric Industrial Co., Ltd. |

| <b></b> |                   | APPRO            | VED  |  |

|---------|-------------------|------------------|------|--|

|         |                   | EXTERNA 82798SUE |      |  |

|         | Product Standards | Total Pages      | Page |  |

|         |                   | 16               | 5    |  |

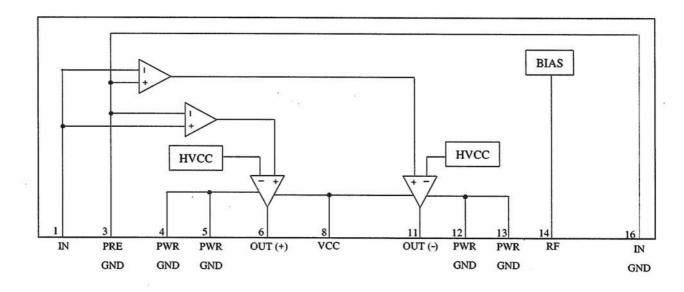

# Block Diagram

|                   | APPRO            | VED  |  |

|-------------------|------------------|------|--|

|                   | EXTERNA 8279 SUE |      |  |

| Product Standards | Total Pages      | Page |  |

|                   | 16               | 6    |  |

# Pin Descriptions

| Pin No. | Pin name | Туре              | Description       |

|---------|----------|-------------------|-------------------|

| 1       | IN       | Input             | Input signal      |

| 2       | NC       | Not connected     | Not Connected     |

| 3       | PRE-GND  | Ground            | Ground            |

| 4       | PWR GND  | Ground            | Ground .          |

| 5       | PWR GND  | Ground            | Ground            |

| 6       | OUT(+)   | Output            | Positive Output   |

| 7       | NC       | Not connected     | Not Connected     |

| 8       | VCC      | Power supply      | 8.0V power supply |

| 9       | NC       | Not connected     | Not Connected     |

| 10      | NC       | Not connected     | Not Connected     |

| 11      | OUT(-)   | Output            | Negative output   |

| 12      | PWR GND  | Ground            | Ground            |

| 13      | PWR GND  | Ground            | Ground            |

| 14      | RF       | Reference voltage | Ripple Filter     |

| 15      | NC       | Not connected     | Not Connected     |

| 16      | IN GND   | Ground            | Ground            |

| 2005-12-09  |         | 80<br>10 |  |  |

|-------------|---------|----------|--|--|

| Established | Revised |          |  |  |

211782700605110

|                   | APPRC       | VED     |

|-------------------|-------------|---------|

|                   | EXTERNA     | 82KASUE |

| Product Standards | Total Pages | Page    |

|                   | 16          | 7       |

## Absolute Maximum Ratings

| A<br>No. | Parameter                     | Symbol           | Rating    | Unit | Note |

|----------|-------------------------------|------------------|-----------|------|------|

| 1        | Supply voltage                | v <sub>cc</sub>  | 14.9      | v    | *1   |

| 2        | Supply current                | I <sub>cc</sub>  | 1         | A    |      |

| 3        | Power dissipation             | PD               | 0.728     | w    | *2   |

| 4        | Operating ambient temperature | T <sub>opr</sub> | -20~ +75  | °C   | *3   |

| 5        | Storage temperature           | T <sub>stg</sub> | -55~ +150 | °C   | *3   |

Note) \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2: The power dissipation shown is the value at Ta = 75 °C for the independent (unmounted) IC package without a heat sink.

When using this IC, refer to the Pd-Ta diagram of the package standard page 18 and use under the condition not exceeding the allowable value. \*3: Except for the operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

## Operating supply voltage range

.

| Parameter            | Symbol          | Range    | Unit | Note |

|----------------------|-----------------|----------|------|------|

| Supply voltage range | V <sub>cc</sub> | 6 ~ 14.5 | v    | -    |

| 2005-12-09  |         |  |

|-------------|---------|--|

| Established | Revised |  |

|             |         |  |

211782700705110

| <br>5<br>         | APPROVED<br>EXTERNIA SUE |      |  |

|-------------------|--------------------------|------|--|

|                   |                          |      |  |

| Product Standards | Total Pages              | Page |  |

|                   | 16                       | 8    |  |

# Electrical Characteristics at Vcc =8 V, RL = 8 Ω, freq = 1 kHz unless otherwise specified.

(Note :  $T_a = 25 \text{ °C} \pm 2 \text{ °C}$  unless otherwise specified.)

| в   | Parameter                    | Symbol          | Test     | Conditions                                   | Limits |     |     |         |       |

|-----|------------------------------|-----------------|----------|----------------------------------------------|--------|-----|-----|---------|-------|

| No. |                              | Symbol          | circuits |                                              | Min    | Тур | Max | Unit    | Notes |

| 1   | Quiescent Circuit Current    | I <sub>CQ</sub> | 1        | No input signal, RL = $\infty$               | 7      | 15  | 30  | mA      |       |

| 2   | Output Noise<br>Voltage      | Vno             | 1        | No input signal                              | -      | 0.3 | 0.7 | mV[rms] | 1     |

| 3   | Voltage Gain                 | Gv              | 1        | Vin=20 mV                                    | 38     | 40  | 42  | dB      |       |

| 4   | Total Harmonic<br>Distortion | THD             | 1        | Vin=20 mV                                    | -      | 0.2 | 0.5 | %       |       |

| 5   | Maximum Output<br>Power      | Ро              | 1        | THD =10 %                                    | 2      | 2.5 | -   | w       |       |

| 6   | Output Offset Voltage        | Voff            | 1        |                                              | -350   | 0   | 350 | mV      |       |

| 7   | Ripple Rejection             | RR              | 1        | Freq-ripple = 120 Hz,<br>V-ripple = 1 V[rms] | 35     | 50  | -   | dB      | 1     |

Note) \*1: For this measurement, use the 20Hz ~ 20kHz (12dB/OCT) filter.

211782700805110

|   | ана стана и стана и стана с | APPRO       | VED                  |  |

|---|-----------------------------------------------------------------------------------------------------------------|-------------|----------------------|--|

| 1 |                                                                                                                 | EXTERNA     | 2 <mark>% SUE</mark> |  |

|   | Product Standards                                                                                               | Total Pages | Page                 |  |

|   |                                                                                                                 | 16          | 9                    |  |

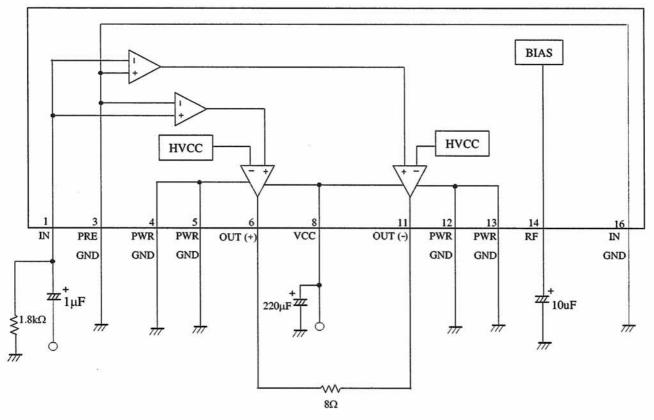

# Test Circuit Diagram

Test Circuit 1

211782700905110

|                                            | APPRO       | VED    |

|--------------------------------------------|-------------|--------|

| 145 ST & 2013 6 455.5 10 10 10 10 10 10 20 | EXTERNA     | 2 ASUE |

| Product Standards                          | Total Pages | Page   |

|                                            | 16          | 10     |

• I/O block circuit diagrams and pin function descriptions

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin No. | Waveform<br>and Voltage | Internal circuit                                        | Description     |

|---------|-------------------------|---------------------------------------------------------|-----------------|

| 1       | 0V                      | 1 200 343<br>30k 30k                                    | INPUT           |

| 2       | -                       | NC                                                      | Not Connected   |

| 3       | 0V                      | PRE GND                                                 | Pre Ground      |

| 4       | ov                      | PWR GND                                                 | Power Ground    |

| 5       | 0V                      | PWR GND                                                 | Power Ground    |

| 6       | VCC/2                   | Pre Amp<br>Driver Circuit<br>359<br>Vcc/2<br>20K<br>4,5 | Positive Output |

| 7       | -                       | NC                                                      | Not Connected   |

| 8       | (Typical)8V             | VCC .                                                   | Supply Voltage  |

| 2005-12-09     |         |                                                                |

|----------------|---------|----------------------------------------------------------------|

| Established    | Revised |                                                                |

| 21178270100511 | 10      | Semiconductor Company, Matsushita Electric Industrial Co., Ltd |

|        |                   | APPRO       | VED   |

|--------|-------------------|-------------|-------|

| - 0.1  |                   | EXTERNA     | 2 SUE |

|        | Product Standards | Total Pages | Page  |

| 11<br> |                   | 16          | 11    |

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No.     | Waveform and<br>Voltage | Internal circuit                                                                                                                                                                    | Description     |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 9              | -                       | NC                                                                                                                                                                                  | Not Connected   |

| 10             | -                       | NC                                                                                                                                                                                  | Not Connected   |

| <b>11</b><br>с | VCC/2                   | Pre Amp<br>Joriver Circuit<br>J<br>J<br>J<br>Vcc/2<br>UK<br>J<br>J<br>Driver Circuit<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J<br>J | Negative Output |

| 12             | 0V                      | PWR GND                                                                                                                                                                             | Power Ground    |

| 13             | 0V                      | PWR GND                                                                                                                                                                             | Power Ground    |

| 14             | 0.45*VCC                | 8<br>60.9k<br>2k<br>60.9k<br>2k<br>2k<br>40.125k                                                                                                                                    | Ripple Filter   |

211782701105110

|             |           | APPRO       | VED                    |

|-------------|-----------|-------------|------------------------|

|             | Let 22    | XTERNA      | 2 <mark>1/A</mark> SUE |

| Product Sta | andards 📘 | Total Pages | Page                   |

|             |           | 16          | 12                     |

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin No. | Waveform<br>and Voltage | Internal circuit | Description   |

|---------|-------------------------|------------------|---------------|

| 15      | -                       | NC               | Not Connected |

| 16      | 0V                      | IN GND           | Input Ground  |

| 2005-12-09  |         |

|-------------|---------|

| Established | Revised |

|                   | APPRO       | VED  |

|-------------------|-------------|------|

|                   | EXTERNA     | 2    |

| Product Standards | Total Pages | Page |

|                   | 16          | 13   |

· Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

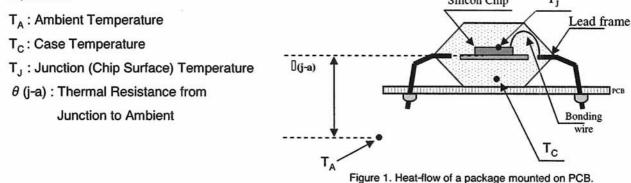

### **Power Dissipation**

Description on the measuring method and the thermal resistance Rth(j-a) of AN17827A is indicated in the following explanation. Silicon Chip  $T_{I}$

#### **Measurement Method**

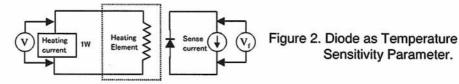

1. The heat generated by the power transistor in the IC is dissipated to the air through the case. To investigate the thermal resistance from junction to case, a diode shown in Figure 2 is used as the temperature sensitivity parameter together with a heating element (to emulate the heat from power transistor).

- 2. The linear relationship between the forward-biased voltage drop (Vbe) and junction temperature when a constant forward-biased current is applied can be used to compute the junction temperature with respect to the power dissipation in the junction region.

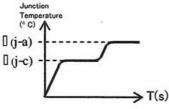

- 3. For example, with heating power 1W(1V,1A) initiated at the heating element and the temperature sampling interval from 0 to 500us to ensure thermal equilibrium is reached, the temperature dependent voltage, V<sub>f</sub> is measured and converted to junction temperature as shown in Figure 3.

Figure 3.  $\theta$  (j-a) Characteristic Plot

5. The junction temperature can be used to compute the thermal resistance from junction to case,  $\theta$  (j-a) using *Equation(1)* where T<sub>c</sub> is the case temperature.

$$\theta(j-a) = \frac{Tj - Ta}{1W} \qquad Equation (1)$$

#### Thermal resistance

The thermal resistance from junction to case,  $\theta$  (j-a) for AN17827A measured using the method mention above is 40°C/W

| 2005-12-09<br>Established | Revised |                                                            |

|---------------------------|---------|------------------------------------------------------------|

| 2117827013051             |         | Semiconductor Company, Matsushita Electric Industrial Co., |

| 5. |                   | APPRO       | VED                                |

|----|-------------------|-------------|------------------------------------|

|    |                   | EXTERNA     | <mark>l₂<mark>∦</mark>∕γSUE</mark> |

|    | Product Standards | Total Pages | Page                               |

|    |                   | 16          | 14                                 |

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

Junction temperature estimation

$Tj = Ta + [](j-a) \times Pd$

Pd: Power dissipation according to application given by (VCC x ICC) - Output power

| 2005-12-09  |         |

|-------------|---------|

| Established | Revised |

|                   | APPROVED    |                                   |

|-------------------|-------------|-----------------------------------|

|                   | EXTERNAS    | 2 <mark>₩<mark>A</mark>SUE</mark> |

| Product Standards | Total Pages | Page                              |

|                   | 16          | 15                                |

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

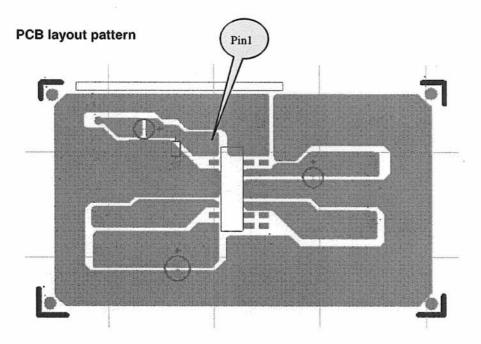

PCB area:98.3mm X 58.78 mm = 5778.07 mm²PCB thickness:1.5 mmMaterial:FR (Flame Retardant)4

2005-12-09 Established Revised

211782701505110

|                   | APPROVED    |       |  |

|-------------------|-------------|-------|--|

|                   | EXTERNA     | 2 SUE |  |

| Product Standards | Total Pages | Page  |  |

|                   | 16          | 16    |  |

#### Usage Notes

- Carry out the thermal design with sufficient margin such that the power dissipation will not be exceeded under the necessary conditions of power supply voltage, load impedance and ambient temperature.

- The protection circuit is for maintaining safety against an abnormal operation. Therefore, design the

protection circuit such that it should not operate during normal operation. Especially for the over-temperature

protection circuit, if the area of safe operation or the absolute maximum rating is momentarily exceeded by

output pin to VCC short, or output pin to GND short (Ground fault), the LSI might be damaged before the

over-temperature protection circuit starts working.

- Pay attention to the PCB (Printed-Circuit-Board) pattern layout in order to prevent damage due to short circuit between pins. In addition, for the pin configuration, refer to the pin functional description diagram (Sheet No.6).

- Do not mount the LSI in the reverse direction onto the PCB (Printed-Circuit-Board). It might be damaged when power is applied.

- Carry out visual inspection on the PCB (Printed-Circuit-Board) before applying the power, otherwise damage might happen due to problems such as solder-bridge between the pins of the semiconductor device. Also, perform a full technical verification on the assembly quality, because the same damage may happen due to conductive substances, such as solder ball, that adhere to the LSI during transportation.

- Take notice in the use of this product that it might be damaged or occasionally emit smoke when an

abnormal state occurs such as output pin-VCC short, output pin-GND short, output-to-output-pin short (load

short), or pin to pin leakage current. (And, safety measures such as an installation of fuses are

recommended because the extent of the above-mentioned damage and smoke emission will depend on the

current capability of the power supply.)

- When carrying out derivative product expansion or when the product is going to be used in a new set, verify the safety including the long-term reliability for each set.

- Check the risk that is caused by the failure of external components.

- The Input pin of this product is necessary to be tied to ground through a resistor as it has significant effect on the output offset and the supply surge susceptibility.

2005-12-09 Established Revised

211782701605111