# ACPL-K71T, ACPL-K72T, ACPL-K74T and ACPL-K75T

Automotive High Speed Low Power Digital Optocouplers with R<sup>2</sup>Coupler<sup>™</sup> Isolation and AEC-Q100 Grade 1 Qualification

# **Data Sheet**

# Description

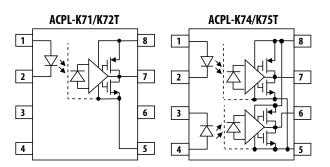

The ACPL-K71T and ACPL-K72T are high speed digital CMOS optocouplers package suitable for emerging electric vehicle applications. The ACPL-K74T and ACPL-K75T are dual channel equivalent of the ACPL-K71T and ACPL-K72T respectively. All products are available in the stretched SO-8 package outline, designed to be compatible with standard surface mount processes.

ACPL-K71T and ACPL-K74T are high speed mode with fastest propagation delay (max 35ns at  $I_F=10$ mA) while ACPL-K72T and ACPL-K75T are low power mode with lowest LED drive current of 4mA for standard digital isolation switching.

Each channel of the digital optocoupler has a CMOS detector IC with an integrated photodiode, a high speed trans-impedance amplifier, and a voltage comparator with an output driver.

Avago R<sup>2</sup>Coupler provides with reinforced insulation and reliability that delivers safe signal isolation critical in automotive and high temperature industrial applications.

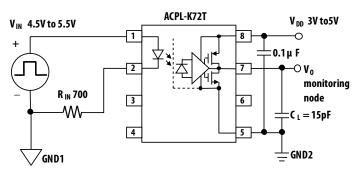

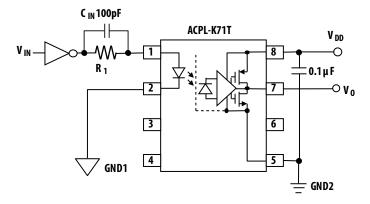

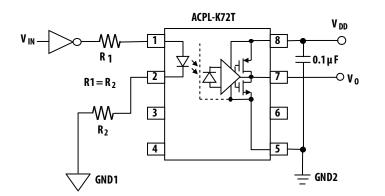

### **Functional Diagram**

Note: The connection of a 0.1  $\mu\text{F}$  bypass capacitor between pins 5 and 8 is recommended.

### Features

- Qualified to AEC-Q100 Grade 1 Test Guidelines

- Automotive Wide Temperature Range: –40°C to 125°C

- High Temperature and Reliability, High Speed Digital Interface for Automotive Application.

- 5 V CMOS compatibility

- 40 kV/ $\mu$ s Common-Mode Rejection at V<sub>CM</sub>=1000V Typ.

- Low Propagation Delay :

ACPL-K71T, ACPL-K74T: 25ns Typ.@ I<sub>F</sub> = 10mA

- ACPL-K72T, ACPLK75T: 60ns Typ.@ I<sub>F</sub> = 4mA

- Worldwide Safety Approval:

- UL 1577 approval, 5kV<sub>RMS</sub> /1 min.

- CSA Approval

- IEC/EN/DIN EN 60747-5-5

#### Applications

- CAN Bus and SPI Communications Interface

- High Temperature Digital/Analog Signal Isolation

- Automotive IPM Driver for DC-DC converters and motor inverters

- Power Transistor Isolation

### **Truth Table**

| LED | Vo   |

|-----|------|

| ON  | LOW  |

| OFF | HIGH |

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

# **Ordering Information**

| Part number | Option<br>(RoHS Compliant) | Package   | Surface<br>Mount | Tape<br>& Reel | UL 5000 V <sub>RMS</sub> / 1<br>Minute rating | IEC/EN/DIN EN<br>60747-5-5 | Quantity      |

|-------------|----------------------------|-----------|------------------|----------------|-----------------------------------------------|----------------------------|---------------|

| ACPL-K71T   | -000E                      | Stretched | Х                |                | Х                                             |                            | 80 per tube   |

|             | -060E                      | SO-8      | Х                |                | Х                                             | Х                          | 80 per tube   |

|             | -500E                      |           | Х                | Х              | Х                                             |                            | 1000 per reel |

|             | -560E                      |           | Х                | Х              | Х                                             | Х                          | 1000 per reel |

| ACPL-K72T   | -000E                      | Stretched | Х                |                | Х                                             |                            | 80 per tube   |

|             | -060E                      | SO-8      | Х                |                | Х                                             | Х                          | 80 per tube   |

|             | -500E                      |           | Х                | Х              | Х                                             |                            | 1000 per reel |

|             | -560E                      |           | Х                | Х              | Х                                             | Х                          | 1000 per reel |

| ACPL-K74T   | -000E                      | Stretched | Х                |                | Х                                             |                            | 80 per tube   |

|             | -060E                      | SO-8      | Х                |                | Х                                             | Х                          | 80 per tube   |

|             | -500E                      |           | Х                | Х              | Х                                             |                            | 1000 per reel |

|             | -560E                      |           | Х                | Х              | Х                                             | Х                          | 1000 per reel |

| ACPL-K75T   | -000E                      | Stretched | Х                |                | Х                                             |                            | 80 per tube   |

|             | -060E                      | SO-8      | Х                |                | Х                                             | Х                          | 80 per tube   |

|             | -500E                      |           | Х                | Х              | Х                                             |                            | 1000 per reel |

|             | -560E                      |           | Х                | Х              | Х                                             | х                          | 1000 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

Example 1:

ACPL-K71T-560E to order product of SSO-8 Surface Mount package in Tape and Reel packaging with IEC/EN/DIN EN 60747-5-5 Safety Approval in RoHS compliant.

Option datasheets are available. Contact your Avago sales representative or authorized distributor for information.

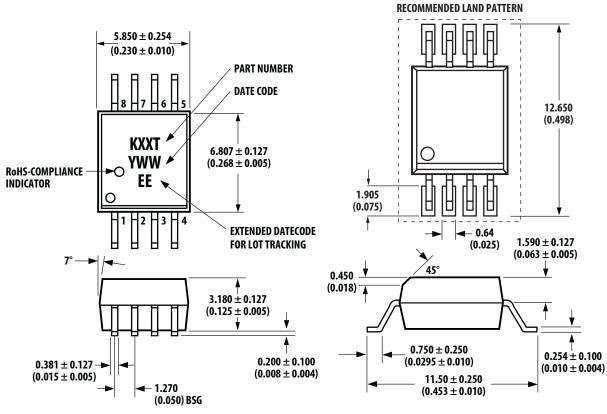

### Package Outline Dimensions (Stretched SO8)

Dimensions in millimeters and (inches).

Note: Lead coplanarity = 0.1 mm (0.004 inches). Floating lead protrusion = 0.25mm (10mils) max.

### **Recommended Pb-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision). Note: Non-halide flux should be used.

### **Regulatory Information**

The ACPL-K71T, ACPL-K72T, ACPL-K74T and ACPL-K75T are approved by the following organizations:

UL

Approval under UL 1577, component recognition program up to  $V_{ISO} = 5kV_{RMS}$ .

CSA

Approval under CSA Component Acceptance Notice #5.

### **IEC/EN/DIN EN 60747-5-5**

Approval under IEC/EN/DIN EN 60747-5-5.

# Insulation and Safety Related Specifications

| Parameter                                               | Symbol |      | Units | Conditions                                                                                                                         |

|---------------------------------------------------------|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External<br>Air Gap (Clearance)                 | L(101) | 8    | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External<br>Tracking (Creepage)                 | L(102) | 8    | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal<br>Plastic Gap<br>(Internal Clearance) |        | 0.08 | mm    | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking<br>Index)  | CTI    | 175  | V     | DIN IEC 112/VDE 0303 Part 1                                                                                                        |

| Isolation Group<br>(DIN VDE0109)                        |        | Illa |       | Material Group (DIN VDE 0109)                                                                                                      |

# IEC/EN/DIN EN 60747-5-5 Insulation Related Characteristic (Option 060 only)

| Description                                                                                       | Symbol                | Characteristic  | Units             |

|---------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------|

| Installation classification per DIN VDE 0110/1.89, Table 1                                        |                       |                 |                   |

| for rated mains voltage $\leq$ 600 V rms                                                          |                       | I-IV            |                   |

| for rated mains voltage $\leq$ 1000 V rms                                                         |                       | 1-111           |                   |

| Climatic Classification                                                                           |                       | 40/125/21       |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                                              |                       | 2               |                   |

| Maximum Working Insulation Voltage                                                                | V <sub>IORM</sub>     | 1140            | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method b                                                            | V <sub>PR</sub>       | 2137            | VPEAK             |

| $V_{\text{IORM}} \times 1.875 = V_{\text{PR}}$ , 100% Production Test with $t_{\text{m}} = 1$ sec |                       |                 |                   |

| Partial Discharge < 5 pC                                                                          |                       |                 |                   |

| Input to Output Test Voltage, Method a                                                            | V <sub>PR</sub>       | 1824            | VPEAK             |

| $V_{IORM} \times 1.6 = V_{PR}$ , Type and sample test, $t_m = 10$ sec,                            |                       |                 |                   |

| Partial Discharge < 5 pC                                                                          |                       |                 |                   |

| Highest Allowable Overvoltage                                                                     | VIOTM                 | 8000            | VPEAK             |

| (Transient Overvoltage, t <sub>ini</sub> = 60 sec)                                                |                       |                 |                   |

| Safety Limiting Values                                                                            |                       |                 |                   |

| (Maximum values allowed in the event of a failure)                                                |                       |                 |                   |

| Case Temperature                                                                                  | Τs                    | 175             | °C                |

| Input Current                                                                                     | I <sub>S,INPUT</sub>  | 230             | mA                |

| Output Power                                                                                      | P <sub>S,OUTPUT</sub> | 600             | mW                |

| Insulation Resistance at $T_S$ , $V_{IO} = 500 V$                                                 | R <sub>S</sub>        | 10 <sup>9</sup> | Ω                 |

|                                                                                                   |                       |                 |                   |

# **Absolute Maximum Ratings**

| Parameter                         | Symbol               | Min.    | Max.                                          | Units | Test Conditions                         |  |  |

|-----------------------------------|----------------------|---------|-----------------------------------------------|-------|-----------------------------------------|--|--|

| Storage Temperature               | Ts                   | -55     | 130                                           | °C    |                                         |  |  |

| Ambient Operating Temperature     | T <sub>A</sub>       | -40     | 125                                           | °C    |                                         |  |  |

| Supply Voltages                   | V <sub>DD</sub>      | 0       | 6.5                                           | V     |                                         |  |  |

| Output Voltage                    | Vo                   | -0.5    | V <sub>DD</sub> +0.5                          | V     |                                         |  |  |

| Average Forward Input Current     | IF                   |         | 20.0                                          | mA    |                                         |  |  |

| Peak Transient Input Current      | I <sub>F(TRAN)</sub> |         | 1                                             | А     | ≤ 1µs Pulse Width, 300pps               |  |  |

|                                   |                      |         | 80                                            | mA    | $\leq$ 1µs Pulse Width, <10% Duty Cycle |  |  |

| Reverse Input Voltage             | Vr                   |         | 5                                             | V     |                                         |  |  |

| Input Power Dissipation           | PI                   |         | 40                                            | mW    |                                         |  |  |

| Output Power Dissipation          | Ро                   |         | 30                                            | mW    |                                         |  |  |

| Lead Solder Temperature           |                      | 260°C f | 260°C for 10 sec., 1.6 mm below seating plane |       |                                         |  |  |

| Solder Reflow Temperature Profile |                      | See Sol | See Solder Reflow Temperature Profile Section |       |                                         |  |  |

# **Recommended Operating Conditions**

| Parameter                 | Symbol              | Min. | Max. | Units | Note |

|---------------------------|---------------------|------|------|-------|------|

| Supply Voltage            | V <sub>CC</sub>     | 3.0  | 5.5  | V     |      |

| Operating Temperature     | T <sub>A</sub>      | -40  | 125  | °C    |      |

| Forward Input Current     | I <sub>F(ON)</sub>  | 4    | 15   | mA    |      |

| Forward Off State Voltage | V <sub>F(OFF)</sub> |      | 0.8  | V     |      |

| Input Threshold Current   | lтн                 |      | 3.5  | mA    |      |

# **Electrical Specifications**

Over recommended temperature  $T_A = -40^{\circ}$ C to  $125^{\circ}$ C,  $3.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}$ . All typical specifications are at  $T_A = 25^{\circ}$ C,  $V_{DD} = 5$ V.

| Parameter                                         | Symbol           | Min.                 | Тур. | Max. | Units | Test Conditions                             | Fig | Notes |

|---------------------------------------------------|------------------|----------------------|------|------|-------|---------------------------------------------|-----|-------|

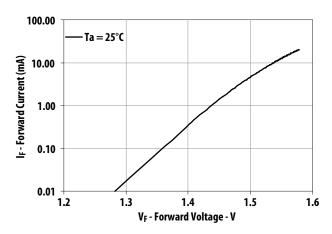

| LED Forward Voltage                               | V <sub>F</sub>   | 1.45                 | 1.5  | 1.75 | V     | I <sub>F</sub> =10 mA, T <sub>A</sub> =25°C |     |       |

|                                                   |                  | 1.25                 | 1.5  | 1.85 | V     | I <sub>F</sub> =10 mA                       |     |       |

| Vf Temperature Coefficient                        |                  |                      | -1.5 |      | mV/°C |                                             |     |       |

| Input Capacitance                                 | C <sub>IN</sub>  |                      | 90   |      | рF    |                                             |     |       |

| Input Reverse Breakdown Voltage                   | BV <sub>R</sub>  | 5.0                  |      |      | V     | $I_R = 10 \ \mu A$                          |     |       |

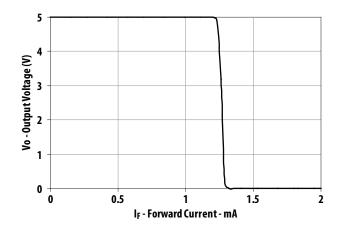

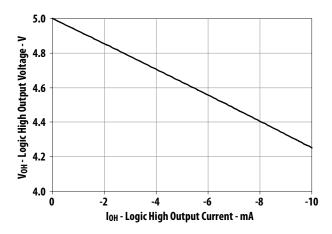

| Logic High Output Voltage                         | V <sub>OH</sub>  | V <sub>DD</sub> -0.6 |      |      | V     | I <sub>OH</sub> = -3.2 mA                   | 4   |       |

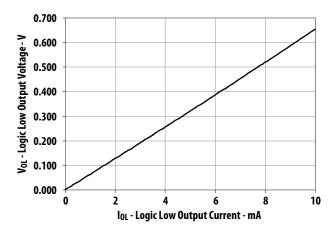

| Logic Low Output Voltage                          | V <sub>OL</sub>  |                      |      | 0.6  | V     | $I_{OL} = 4 \text{ mA}$                     | 3   |       |

| Logic Low Output Supply<br>Current (per channel)  | I <sub>DDL</sub> |                      | 0.9  | 1.5  | mA    |                                             |     |       |

| Logic High Output Supply<br>Current (per channel) | IDDH             |                      | 0.9  | 1.5  | mA    |                                             |     |       |

### ACPL-K71T, ACPL-K74T High Speed Mode Switching Specifications

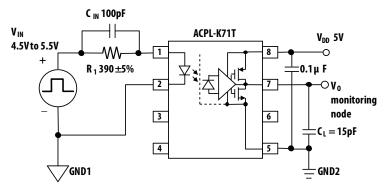

Over recommended temperature  $T_A = -40^{\circ}$ C to 125°C, 4.5 V  $\leq V_{DD} \leq 5.5$  V. All typical specifications are at  $T_A = 25^{\circ}$ C,  $V_{DD} = 5$ V.

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                                                                                                                                                                             | Fig    | Notes |

|--------------------------------------------------------|------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

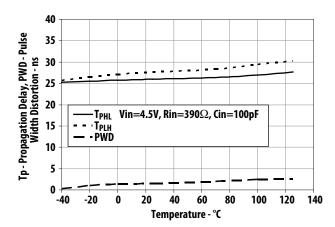

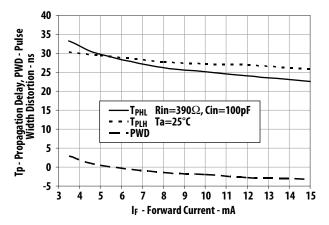

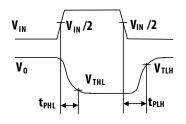

| Propagation Delay Time<br>to Logic Low Output          | t <sub>PHL</sub> |      | 25   | 35   | ns    | $\begin{split} V_{IN} &= 4.5 V\text{-} 5.5 V, \\ R_{IN} &= 390 \Omega \pm 5\%, \\ C_{IN} &= 100 \text{pF}, \text{C}_L = 15 \text{pF} \\ V_{THL} &= 0.8 V \\ V_{TLH} &= 80\% \text{ of } V_{DD} \end{split}$ | 5,6,11 | 1,2,3 |

| Propagation Delay Time<br>to Logic High Output         | t <sub>PLH</sub> |      | 25   | 35   | ns    |                                                                                                                                                                                                             |        |       |

| Pulse Width Distortion                                 | PWD              |      | 0    | 12   | ns    |                                                                                                                                                                                                             |        |       |

| Propagation Delay Skew                                 | t <sub>PSK</sub> |      |      | 15   | ns    |                                                                                                                                                                                                             |        |       |

| Output Rise Time (10% – 90%)                           | t <sub>R</sub>   |      | 10   |      | ns    |                                                                                                                                                                                                             |        |       |

| Output Fall Time (90% - 10%)                           | t <sub>F</sub>   |      | 10   |      | ns    |                                                                                                                                                                                                             |        |       |

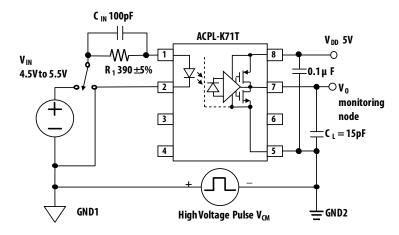

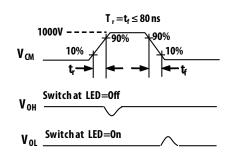

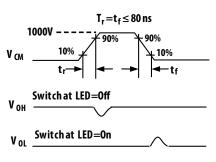

| Common Mode Transient<br>Immunity at Logic High Output | CM <sub>H</sub>  | 15   | 25   |      | kV/μs | $\begin{split} V_{IN} &= 0V, \\ R_{IN} &= 390 \Omega \pm 5\%, \ C_{IN} &= 100 \text{pF}, \\ V_{CM} &= 1000V, \ T_A &= 25^\circ\text{C} \end{split}$                                                         | 12     | 4     |

| Common Mode Transient<br>Immunity at Logic High Output | CM <sub>L</sub>  | 15   | 25   |      | kV/µs | $\begin{split} V_{IN} &= 4.5V\text{-}5.5V , \\ R_{IN} &= 390\Omega \pm 5\%,  C_{IN} = 100\text{pF}, \\ V_{CM} &= 1000V,  T_A = 25^\circ\text{C} \end{split}$                                                | 12     | 5     |

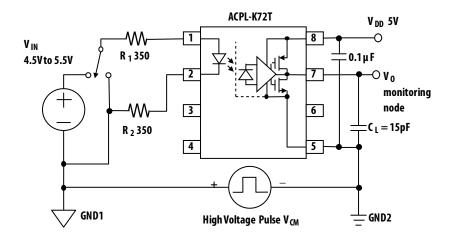

# ACPL-K72T, ACPL-K75T Low Power Mode Switching Specifications

Over recommended temperature  $T_A = -40^{\circ}$ C to 125°C, 3.0 V  $\leq V_{DD} \leq 5.5$  V. All typical specifications are at  $T_A = 25^{\circ}$ C,  $V_{DD} = 5$ V.

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                                                                                                                                                | Fig                | Notes |

|--------------------------------------------------------|------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|

| Propagation Delay Time<br>to Logic Low Output          | t <sub>PHL</sub> |      | 60   | 100  | ns    | $I_F = 4mA, C_L = 15pF$<br>$V_{THL} = 0.8V$<br>$V_{TLH} = 80\% \text{ of } V_{DD}$                                                                                             | 7, 8, 9,<br>10, 13 | 1,2,3 |

| Propagation Delay Time<br>to Logic High Output         | t <sub>PLH</sub> |      | 35   | 100  | ns    |                                                                                                                                                                                |                    |       |

| Pulse Width Distortion                                 | PWD              |      | 25   | 50   | ns    |                                                                                                                                                                                |                    |       |

| Propagation Delay Skew                                 | t <sub>PSK</sub> |      |      | 60   | ns    |                                                                                                                                                                                |                    |       |

| Output Rise Time<br>(10% – 90%)                        | t <sub>R</sub>   |      | 10   |      | ns    |                                                                                                                                                                                |                    |       |

| Output Fall Time<br>(90% - 10%)                        | t <sub>F</sub>   |      | 10   |      | ns    |                                                                                                                                                                                |                    |       |

| Common Mode Transient<br>Immunity at Logic High Output | CM <sub>H</sub>  | 25   | 40   |      | kV/μs | $ \begin{array}{l} \mbox{LED Driving Circuit Fig 13,} \\ V_{IN} = 0V, \\ R1 = 350\Omega \pm 5\%, \\ R2 = 350\Omega \pm 5\%, \\ V_{CM} = 1000V, T_A = 25^{\circ}C \end{array} $ | 14                 | 4     |

| Common Mode Transient<br>Immunity at Logic High Output | CM <sub>L</sub>  | 25   | 40   |      | kV/μs | LED Driving Circuit Fig 14,<br>$V_{IN} = 4.5-5.5V$ ,<br>$R1 = 350\Omega \pm 5\%$ ,<br>$R2 = 350\Omega \pm 5\%$ ,<br>$V_{CM} = 1000V$ , $T_A = 25^{\circ}C$                     | 14                 | 5     |

### **Package Characteristics**

All Typical at  $T_A = 25^{\circ}C$ .

| Parameter                                   | Symbol           | Min. | Тур.             | Max. | Units            | Test Conditions                                                                                  | Notes |

|---------------------------------------------|------------------|------|------------------|------|------------------|--------------------------------------------------------------------------------------------------|-------|

| Input-Output Momentary<br>Withstand Voltage | V <sub>ISO</sub> | 5000 |                  |      | V <sub>RMS</sub> | $\label{eq:RH} \begin{array}{l} RH \leq 50\%,  t=1   minute, \\ T_{A} = 25^{\circ}C \end{array}$ | 6, 7  |

| Input-Output Resistance                     | R <sub>I-O</sub> |      | 10 <sup>14</sup> |      | Ω                | $V_{I-O} = 500 V dc$                                                                             | 6     |

| Input-Output Capacitance                    | C I-O            |      | 0.6              |      | pF               | f = 1 MHz, T <sub>A</sub> = 25°C                                                                 | 6     |

|                                             |                  |      |                  |      |                  |                                                                                                  |       |

Notes:

2. PWD is defined as |t<sub>PHL</sub> - t<sub>PLH</sub>|.

3. t<sub>PSK</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature within the recommended operating conditions.

4. CM<sub>H</sub> is the maximum tolerable rate of rise of the common mode voltage to assure that the output will remain in a high logic state.

5. CML is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state.

6. Device considered a two terminal device: pins 1, 2, 3 and 4 shorted together, and pins 5, 6, 7 and 8 shorted together.

7. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage >  $6000V_{RMS}$  for 1 second.

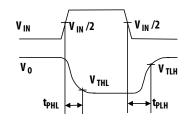

<sup>1.</sup>  $t_{PHL}$  propagation delay is measured from the 50% ( $V_{IN}$  or  $I_F$ ) on the rising edge of the input pulse to the 0.8V of  $V_{DD}$  of the falling edge of the  $V_O$  signal.  $t_{PLH}$  propagation delay is measured from the 50% ( $V_{IN}$  or  $I_F$ ) on the falling edge of the input pulse to the 80% level of the rising edge of the  $V_O$  signal.

**Performance Plots**

Figure 1. Typical Diode Input Forward Current Characteristic

Figure 3 Typical Logic Low Output Voltage vs Low Low Output Current

Figure 5. ACPL-K71T/K74T (High Speed) Typical Propagation Delay vs Temperature

Figure 2. Typical Output Voltage vs Input Forward Current

Figure 4. Typical Logic High Output Voltage vs Logic High Output Current

Figure 6. ACPL-K71T/K74T (High Speed) Typical Propagation Delay vs Input Forward Current

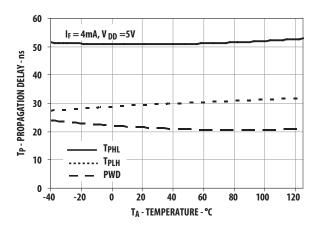

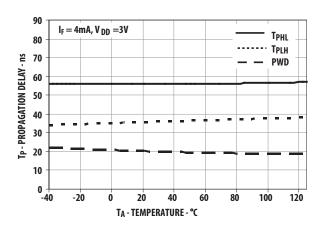

Figure 7. ACPL-K72T/K75T (5V) Typical Propagation Delay vs Temperature

Figure 9. ACPL-K72T/K75T (3V) Typical Propagation Delay vs Temperature

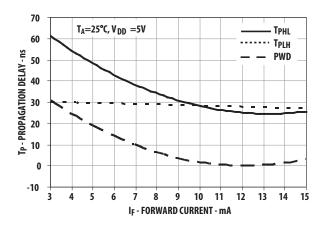

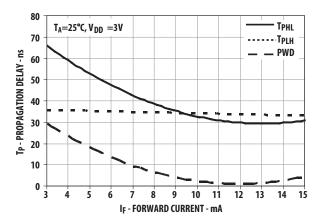

Figure 8. ACPL-K72T/K75T (5V) Typical Propagation Delay vs Input Forward Current

Figure 10. ACPL-K72T/K75T (3V) Typical Propagation Delay vs Input Forward Current

### ACPL-K71T/K74T High Speed Mode:

Figure 11. High Speed Mode Switching Test Circuit and Typical Waveform

Figure 12. High Speed Mode CMR Test Circuit and Typical Waveform

Figure 13. Low Power Mode Switching Test Circuit and Typical Waveform

Figure 14. Low Power Mode CMR Test Circuit

### **Recommended Application Circuits**

| Truth Table |     |      |  |  |  |  |  |  |  |

|-------------|-----|------|--|--|--|--|--|--|--|

| VIN         | LED | Vo   |  |  |  |  |  |  |  |

| LOW         | ON  | LOW  |  |  |  |  |  |  |  |

| HIGH        | OFF | HIGH |  |  |  |  |  |  |  |

Figure 15. Recommended Application Circuit for ACPL-K71T/K74T High Speed Performance

| Truth | Table |

|-------|-------|

|       |       |

| V <sub>IN</sub> | LED | Vo   |  |  |  |

|-----------------|-----|------|--|--|--|

| LOW             | ON  | LOW  |  |  |  |

| HIGH            | OFF | HIGH |  |  |  |

Figure 16. Recommended Application Circuit for ACPL-K72T/K75T Low Power Performance

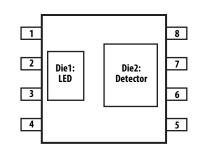

### Thermal Resistance Model for ACPL-K71T/K72T

The diagram of ACPL-K71T/K72T for measurement is shown in Figure 17. Here, one die is heated first and the temperatures of all the dice are recorded after thermal equilibrium is reached. Then, the 2nd die is heated and all the dice temperatures are recorded. With the known ambient temperature, the die junction temperature and power dissipation, the thermal resistance can be calculated. The thermal resistance calculation can be cast in matrix form. This yields a 2 by 2 matrix for our case of two heat sources.

| $R_{11}$ | $R_{12}$        | х | P1             | _ | $\Delta T_1$<br>$\Delta T_2$ |

|----------|-----------------|---|----------------|---|------------------------------|

| $R_{21}$ | R <sub>22</sub> | ~ | P <sub>2</sub> | _ | $\Delta T_2$                 |

$\begin{array}{l} R_{11}: \mbox{Thermal Resistance of Die1 due to heating of Die1 (°C/W)} \\ R_{12}: \mbox{Thermal Resistance of Die1 due to heating of Die2 (°C/W)} \\ R_{21}: \mbox{Thermal Resistance of Die2 due to heating of Die1 (°C/W)} \\ R_{22}: \mbox{Thermal Resistance of Die2 due to heating of Die2 (°C/W)} \\ \end{array}$

P<sub>1</sub>: Power dissipation of Die1 (W)

P<sub>2</sub> : Power dissipation of Die2 (W)

$T_1$  : Junction temperature of Die1 due to heat from all dice (°C)

$T_2$  : Junction temperature of Die2 due to heat from all dice (°C)

T<sub>a</sub> : Ambient temperature (°C)

$\Delta T_1$ : Temperature difference between Die1 junction and ambient (°C)  $\Delta T_2$ : Temperature deference between Die2 junction and ambient (°C)

$T_1 = (R_{11} \times P_1 + R_{12} \times P_2) + T_a$  $T_2 = (R_{21} \times P_1 + R_{22} \times P_2) + T_a$

Measurement data on a low K board:

$R_{11} = 160 \text{°C/W}, R_{12} = R_{21} = 74 \text{°C/W}, R_{22} = 115 \text{°C/W}$

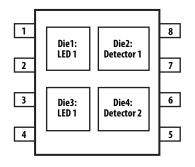

### Thermal Resistance Model for ACPL-K74T/K75T

The diagram of ACPL-K74T/K75T for measurement is shown in Figure 18. Here, one die is heated first and the temperatures of all the dice are recorded after thermal equilibrium is reached. Then, the 2nd, 3rd and 4th die is heated and all the dice temperatures are recorded. With the known ambient temperature, the die junction temperature and power dissipation, the thermal resistance can be calculated. The thermal resistance calculation can be cast in matrix form. This yields a 4 by 4 matrix for our case of two heat sources.

| R <sub>11</sub> | $R_{12}$        | $R_{13}$        | $R_{14}$        |   | P <sub>1</sub> |   | $\Delta T_1$                 |  |

|-----------------|-----------------|-----------------|-----------------|---|----------------|---|------------------------------|--|

| $R_{21}$        | R <sub>22</sub> | R <sub>23</sub> | R <sub>24</sub> | v | P <sub>2</sub> | _ | $\Delta T_2$<br>$\Delta T_3$ |  |

| $R_{31}$        | $R_{32}$        | $R_{33}$        | $R_{34}$        | ^ | P <sub>3</sub> | = | $\Delta T_3$                 |  |

| $R_{41}$        |                 | $R_{43}$        |                 |   | P4             |   | $\Delta T_4$                 |  |

$\begin{array}{l} R_{11} : \mbox{Thermal Resistance of Die1 due to heating of Die1 (°C/W)} \\ R_{12} : \mbox{Thermal Resistance of Die1 due to heating of Die2 (°C/W)} \\ R_{13} : \mbox{Thermal Resistance of Die1 due to heating of Die3 (°C/W)} \\ R_{14} : \mbox{Thermal Resistance of Die1 due to heating of Die4 (°C/W)} \end{array}$

$\begin{array}{l} R_{21} : \mbox{Thermal Resistance of Die2 due to heating of Die1 (°C/W)} \\ R_{22} : \mbox{Thermal Resistance of Die2 due to heating of Die2 (°C/W)} \\ R_{23} : \mbox{Thermal Resistance of Die2 due to heating of Die3 (°C/W)} \end{array}$

$R_{24}\,$  :Thermal Resistance of Die2 due to heating of Die4 (°C/W)  $\,$

Figure 18. Diagram of ACPL-K74T/K75T for measurement

Figure 17. Diagram of ACPL-K71T/K72T for measurement

R<sub>31</sub> : Thermal Resistance of Die3 due to heating of Die1 (°C/W)

R<sub>32</sub> : Thermal Resistance of Die3 due to heating of Die2 (°C/W)

R<sub>33</sub> : Thermal Resistance of Die3 due to heating of Die3 (°C/W)

R<sub>34</sub> : Thermal Resistance of Die3 due to heating of Die4 (°C/W)

R<sub>41</sub> : Thermal Resistance of Die4 due to heating of Die1 (°C/W)

$R_{42}$ : Thermal Resistance of Die4 due to heating of Die2 (°C/W)

R<sub>43</sub> : Thermal Resistance of Die4 due to heating of Die3 (°C/W)

R44 : Thermal Resistance of Die4 due to heating of Die4 (°C/W)

- P<sub>1</sub>: Power dissipation of Die1 (W)

- P<sub>2</sub> : Power dissipation of Die2.

- P<sub>3</sub>: Power dissipation of Die3 (W)

- P<sub>4</sub> : Power dissipation of Die4.

T<sub>1</sub> : Junction temperature of Die1 due to heat from all dice (°C)

T<sub>2</sub> : Junction temperature of Die2 due to heat from all dice (°C)

$T_3$  : Junction temperature of Die3 due to heat from all dice (°C)

T<sub>4</sub> : Junction temperature of Die4 due to heat from all dice (°C)

$T_a$  : Ambient temperature (°C)

$\Delta T_1$  : Temperature difference between Die1 junction and ambient (°C)

$\Delta T_2$ : Temperature deference between Die2 junction and ambient (°C)

$\Delta T_3$ : Temperature difference between Die3 junction and ambient (°C)

$\Delta T_4$ : Temperature deference between Die4 junction and ambient (°C)

$T_1 = (R11 \times P1 + R12 \times P2 + R13 \times P3 + R14 \times P4) + Ta -- (1)$

- $T_2 = (R21 \times P1 + R22 \times P2 + R23 \times P3 + R24 \times P4) + Ta -- (2)$

- $T_3 = (R31 \times P1 + R32 \times P2 + R33 \times P3 + R34 \times P4) + Ta -- (3)$

- $T_4 = (R41 \times P1 + R42 \times P2 + R43 \times P3 + R44 \times P4) + Ta -- (4)$

#### Measurement data on a low K board:

| R <sub>11</sub> | R <sub>12</sub> | R <sub>13</sub> | R <sub>14</sub> | R <sub>21</sub> | R <sub>22</sub> | R <sub>23</sub> | R <sub>24</sub> | R <sub>31</sub> | R <sub>32</sub> | R <sub>33</sub> | R <sub>34</sub> | R <sub>41</sub> | R <sub>42</sub> | R <sub>43</sub> | R <sub>44</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 160             | 76              | 76              | 76              | 76              | 115             | 76              | 76              | 76              | 76              | 160             | 76              | 76              | 76              | 76              | 115             |

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2012 Avago Technologies. All rights reserved. AV02-3786EN - September 26, 2012