# **CA-IS1200 Isolated Amplifier for Current Sensing**

# 1 Key Features

- Differential Input Voltage Range: ±250 mV

- Fixed Initial Gain: 8

- Low Input Offset and Drift: ±1 mV (max) at 25°C, ±4 μV/°C (max)

- Low Gain Error and Drift: ±0.5% (max) at 25°C, ±50 ppm/°C (max)

- Low Nonlinearity and Drift:

0.01% (typ) for Full Scale, ±1 ppm/°C (typ)

- 3.3-V or 5-V Operation for Both High- and Low-Side

- High CMTI: ±150 kV/μs (typ)

- Wide Operating Temperature Range: –40°C to 125°C

- Safety-Related Certifications (Pending)

- 7070-V<sub>PK</sub> (CA-IS1200G) Isolation per DIN V VDE V 0884-11 (VDE V 0884-11): 2017-01

- 5000-V<sub>RMS</sub> (CA-IS1200G) Isolation for 1 Minute per UL 1577

- CQC and TUV Certification Approvals

# 2 Applications

- Industrial Motor Controls and Drives

- Isolated Switch Mode Supplies

- Uninterruptible Power Supplies

#### 3 Description

The CA-IS1200 devices are high-precision isolated amplifiers and optimized for shunt-resistor-based current sensing. Low offset and gain error and drift guarantee that measuring accuracy is maintained over the entire operating temperature range.

The CA-IS1200 devices utilize silicon oxide  $(SiO_2)$  isolation barriers and support up to  $3750-V_{RMS}$  (CA-IS1200U) or 5000- $V_{RMS}$  (CA-IS1200G) galvanic isolation per UL 1577. This technology separates high- and low-voltage domain to protect lower-voltage parts from damage and provides low emissions as well as strong anti-interference capability from magnetic changes. The high common-mode transient immunity (CMTI) means that the CA-IS1200 devices transmit correct signals through isolation barriers and are suitable for industrial motor controls and drives which require high-voltage and high-power switching. The internal input common-mode overvoltage and missing high-side supply voltage detection functions contribute to fault diagnostics and system safety.

The CA-IS1200 devices are packaged in 8-pin DUB or widebody SOIC packages and specified over the extended industrial temperature range of  $-40^{\circ}$ C to 125°C.

### **Device Information**

| PART<br>NUMBER | PACKAGE      | BODY SIZE (NOM)   |

|----------------|--------------|-------------------|

| CA-IS1200U     | DUB8 (U)     | 9.20 mm × 6.62 mm |

| CA-IS1200G     | SOIC8-WB (G) | 5.85 mm × 7.50 mm |

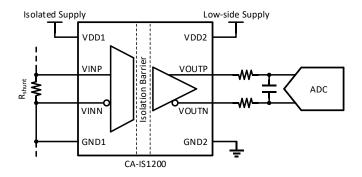

# **Simplified Schematic**

# 4 Ordering Guide

# Table 4-1 Ordering Guide for Valid Ordering Part Number

| Ordering Part Number | Specified Input Range | Isolation Rating      | Package  |

|----------------------|-----------------------|-----------------------|----------|

| CA-IS1200U           | ±250 mV               | 3750 V <sub>RMS</sub> | DUB8     |

| CA-IS1200G           | ±250 mV               | 5000 V <sub>RMS</sub> | SOIC8-WB |

# CA-IS1200U, CA-IS1200G Version 1.01, 2022/12/20

# **Table of Contents**

| 1 | Кеу   | Features                              | 1  |

|---|-------|---------------------------------------|----|

| 2 | Арр   | lications                             | 1  |

| 3 | Desc  | cription                              | 1  |

| 4 | Orde  | ering Guide                           | 2  |

| 5 | Revi  | sion History                          | 3  |

| 6 | Pin I | Descriptions and Functions            | 4  |

| 7 | Spec  | cifications                           | 5  |

|   | 7.1   | Absolute Maximum Ratings <sup>1</sup> | 5  |

|   | 7.2   | ESD Ratings                           | 5  |

|   | 7.3   | Recommended Operating Conditions      | 5  |

|   | 7.4   | Thermal Information                   | 5  |

|   | 7.5   | Power Ratings                         | 5  |

|   | 7.6   | Insulation Specifications             | 6  |

|   | 7.7   | Safety-Related Certifications         | 7  |

|   | 7.8   | Electrical Characteristics            | 8  |

|   | 7.9   | Typical Characteristics               | 10 |

| 8 | Para  | meter Measurement Information         | 15 |

| 9 | Deta  | ailed Description                     | 16 |

|    | 9.1  | Syst    | em Overview                                  | 16 |

|----|------|---------|----------------------------------------------|----|

|    | 9.2  | Feat    | ure Description                              | 16 |

|    |      | 9.2.1   | Analog Input                                 | 16 |

|    |      | 9.2.2   | Signal Transmission Across Isolation Barrier | 16 |

|    |      | 9.2.3   | Fail-Safe Output                             | 17 |

| 10 |      | Applic  | ation and Implementation                     | 19 |

|    |      | 10.1.1  | Typical Application for Current Sensing      | 19 |

|    |      | 10.1.2  | Choose Proper R <sub>shunt</sub>             | 19 |

|    |      | 10.1.3  | Input Filter                                 | 20 |

|    |      | 10.1.4  | Power Supply Recommendations                 | 20 |

|    |      | 10.1.5  | Output Filter                                | 20 |

|    |      | 10.1.6  | Error Analysis in Voltage Sensing            |    |

|    |      | 10.1.7  | Caution                                      | 21 |

| 11 |      | Packa   | ge Information                               | 22 |

|    | 11.1 | . 8-Pii | n DUB Package                                | 22 |

|    | 11.2 | 8-Pii   | n Wide Body SOIC Package                     | 23 |

| 12 |      | Solder  | ing Information                              | 24 |

| 13 |      | Tape a  | nd Reel Information                          | 25 |

| 14 |      | Impor   | tant Notice                                  | 26 |

# 5 Revision History

| Revision     | Description                           | Rev Date   | Page     |

|--------------|---------------------------------------|------------|----------|

| Version 1.00 | NA                                    |            | NA       |

| Version 1.01 | Changed POD and Type reel information | 2022/12/20 | 21,22,24 |

Version 1.01, 2022/12/20

# 6 Pin Descriptions and Functions

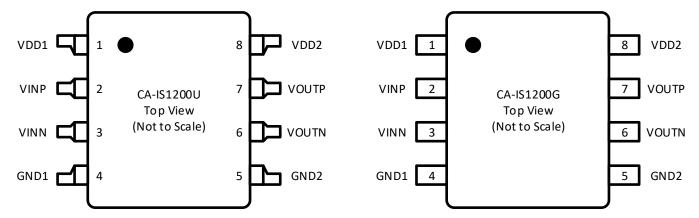

# Figure 6-1 CA-IS1200 Top View

# Table 6-1 CA-IS1200 Pin Description and Functions

| NAME  | PIN NUMBER | ТҮРЕ   | DESCRIPTION                          |

|-------|------------|--------|--------------------------------------|

| VDD1  | 1          | Power  | High-side power supply, 3 V to 5.5 V |

| VINP  | 2          | Input  | Noninverting analog input            |

| VINN  | 3          | Input  | Inverting analog input               |

| GND1  | 4          | Ground | High-side ground                     |

| GND2  | 5          | Ground | Low-side ground                      |

| VOUTN | 6          | Output | Inverting analog output              |

| VOUTP | 7          | Output | Noninverting analog output           |

| VDD2  | 8          | Power  | Low-side power supply, 3 V to 5.5 V  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>1</sup>

|                  | PARAMETER                                   | MIN        | MAX                     | UNIT |

|------------------|---------------------------------------------|------------|-------------------------|------|

| VDD1, VDD2       | Supply voltage <sup>2</sup>                 | -0.5       | 6.5                     | V    |

| VINP, VINN       | Analog input voltage                        | GND1 – 6   | 6.5                     | V    |

| VOUTP, VOUTN     | Analog output voltage                       | GND2 – 0.5 | VDD2 + 0.5 <sup>3</sup> | V    |

| I <sub>IN</sub>  | Input current to any pin except supply pins | -10        | 10                      | mA   |

| Tj               | Junction Temperature                        |            | 150                     | °C   |

| T <sub>STG</sub> | Storage Temperature                         | -65        | 150                     | °C   |

NOTE:

1. Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All voltage values are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values.

- 3. Maximum voltage must not exceed 6.5 V.

### 7.2 ESD Ratings

|                                          |                                                                           | VALUE | UNIT |

|------------------------------------------|---------------------------------------------------------------------------|-------|------|

| V <sub>ESD</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins              | ±4000 | V    |

|                                          | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins | ±2000 | v    |

### 7.3 Recommended Operating Conditions

|                | PARAMETER                                      | MIN | NOM | MAX | UNIT |

|----------------|------------------------------------------------|-----|-----|-----|------|

| VDD1           | High-side supply voltage, with respect to GND1 | 3.0 | 5.0 | 5.5 | V    |

| VDD2           | Low-side supply voltage, with respect to GND2  | 3.0 | 3.3 | 5.5 | V    |

| T <sub>A</sub> | Ambient Temperature                            | -40 |     | 125 | °C   |

### 7.4 Thermal Information

|                          | THERMAL METRIC                               | VALUE<br>(U) | VALUE<br>(G) | UNIT |

|--------------------------|----------------------------------------------|--------------|--------------|------|

| R <sub>θJA</sub>         | Junction-to-ambient thermal resistance       | 73.3         | 110.1        | °C/W |

| R <sub>0JC(top)</sub>    | Junction-to-case (top) thermal resistance    | 63.2         | 51.7         | °C/W |

| R <sub>θJB</sub>         | Junction-to-board thermal resistance         | 43.0         | 66.4         | °C/W |

| Ψ <sub>.</sub> ,         | Junction-to-top characterization parameter   | 27.4         | 16.0         | °C/W |

| ψ <sub>JB</sub>          | Junction-to-board characterization parameter | 42.7         | 64.5         | °C/W |

| R <sub>0JC(bottom)</sub> | Junction-to-case (bottom) thermal resistance | NA           | NA           | °C/W |

#### 7.5 Power Ratings

|                 | PARAMETER                                | TEST CONDITIONS     | VALUE  | UNIT |  |

|-----------------|------------------------------------------|---------------------|--------|------|--|

| D               | Maximum power dissipation for both sides | VDD1 = VDD2 = 5.5 V | 129.25 | mW   |  |

| PD              | Maximum power dissipation for both sides | VDD1 = VDD2 = 3.6 V | 76.32  | mvv  |  |

| D               | Maximum nawar dissination for high side  | VDD1 = 5.5 V        | 85.25  | mW   |  |

| P <sub>D1</sub> | Maximum power dissipation for high-side  | VDD1 = 3.6 V        | 50.40  |      |  |

|                 | Maximum navyor dissination for law side  | VDD2 = 5.5 V        | 44.00  |      |  |

| P <sub>D2</sub> | Maximum power dissipation for low-side   | VDD2 = 3.6 V        | 25.92  | mW   |  |

Version 1.01, 2022/12/20

#### 7.6 Insulation Specifications

|                   | PARAMETR                                          | TEST CONDITIONS                                                                                                                                                                             | VALUE<br>(U)      | VALUE<br>(G) | UNI             |

|-------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|-----------------|

| CLR               | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                                                                                                                                          | 6.1               | 8            | mm              |

| CPG               | External creepage <sup>1</sup>                    | Shortest terminal-to-terminal distance across the package surface                                                                                                                           | 6.8               | 8            | mm              |

| DTI               | Distance through the insulation                   | Minimum internal gap (internal clearance)                                                                                                                                                   | 28                | 28           | μm              |

| СТІ               | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                       | > 600             | > 600        | V               |

|                   | Material group                                    | According to IEC 60664-1                                                                                                                                                                    | I                 | I            |                 |

|                   |                                                   | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                                  | I-IV              | I-IV         |                 |

|                   | Overvoltage category per IEC 60664-1              | Rated mains voltage ≤ 400 V <sub>RMS</sub>                                                                                                                                                  | I-IV              | I-IV         |                 |

|                   |                                                   | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                  | -                 | -            |                 |

| DIN V VD          | E V 0884-11:2017-01 <sup>2</sup>                  |                                                                                                                                                                                             |                   |              |                 |

| VIORM             | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                                        | 1414              | 1414         | VP              |

| V <sub>IOWM</sub> | Maximum working isolation voltage                 | AC voltage; Time dependent dielectric<br>breakdown (TDDB) Test                                                                                                                              | 1000              | 1000         | V <sub>RN</sub> |

|                   |                                                   | DC voltage                                                                                                                                                                                  | 1414              | 1414         | VD              |

| VIOTM             | Maximum transient isolation voltage               | $V_{\text{TEST}} = V_{\text{IOTM}},$<br>t = 60 s (qualification);<br>$V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}},$<br>t = 1 s (100% production)                                           | 5300              | 7070         | VPF             |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>3</sup>      | Test method per IEC 60065, 1.2/50 $\mu$ s waveform,<br>V <sub>TEST</sub> = 1.6 × V <sub>IOSM</sub> (qualification)                                                                          | 5000              | 6250         | VPI             |

|                   |                                                   | Method a, After input/output safety test<br>subgroup 2/3,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s;<br>$V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10$ s                                   | ≤ 5               | ≤ 5          |                 |

| q <sub>pd</sub>   | Apparent charge <sup>4</sup>                      | Method a, After environmental tests subgroup 1,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s;<br>$V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10$ s                                             | ≤ 5               | ≤ 5          | рC              |

|                   |                                                   | Method b1, At routine test (100% production)<br>and preconditioning (type test)<br>$V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1 s$ ;<br>$V_{pd(m)} = 1.875 \times V_{IORM}$ , $t_m = 1 s$ | ≤5 ≤5             |              |                 |

| CIO               | Barrier capacitance, input to output <sup>5</sup> | $V_{IO} = 0.4 \times sin (2\pi ft), f = 1 MHz$                                                                                                                                              | ~ 1               | ~ 1          | pF              |

|                   |                                                   | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                              | > 1012            | > 1012       |                 |

| R <sub>IO</sub>   | Isolation resistance <sup>5</sup>                 | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                     | > 1011            | > 1011       | Ω               |

|                   |                                                   | V <sub>IO</sub> = 500 V at T <sub>s</sub> = 150°C                                                                                                                                           | > 10 <sup>9</sup> | > 109        |                 |

|                   | Pollution degree                                  |                                                                                                                                                                                             | 2                 | 2            |                 |

| UL 1577           | -                                                 | 1                                                                                                                                                                                           |                   |              | 1               |

|                   |                                                   | $V_{\text{TEST}} = V_{\text{ISO}}$ , t = 60 s (qualification),                                                                                                                              |                   |              | <u> </u>        |

#### NOTE:

1. Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

2. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

3. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

4. Apparent charge is electrical discharge caused by a partial discharge (pd).

5. All pins on each side of the barrier tied together creating a two-terminal device.

Version 1.01, 2022/12/20

# 上海川土微电子有限公司

# 7.7 Safety-Related Certifications

| VDE (Pending)                            | UL                                 | CQC (Pending)                        |  |  |

|------------------------------------------|------------------------------------|--------------------------------------|--|--|

| Certified according to DIN V VDE V 0884- | Recognized under UL 1577 Component | Certified according to GB4943.1-2011 |  |  |

| 11:2017-01                               | Recognition Program                |                                      |  |  |

| Certification number:                    | Certification number:              | Certification number:                |  |  |

|                                          | E511334-20200520                   |                                      |  |  |

Version 1.01, 2022/12/20

#### 7.8 Electrical Characteristics

All minimum and maximum specifications apply from  $T_A = -40^{\circ}$ C to 125°C, VDD1 = 3 V to 5.5 V, VDD2 = 3 V to 5.5 V, VINP = -250 mV to 250 mV, and VINN = GND1 = 0 V (unless otherwise noted). All typical specifications are at  $T_A = 25^{\circ}$ C, VDD1 = 5 V, and VDD2 = 3.3 V (unless otherwise noted).

|                       | PARAMETER                                            | TEST CONDITIONS                                                                  | MIN      | ТҮР        | MAX           | UNIT              |

|-----------------------|------------------------------------------------------|----------------------------------------------------------------------------------|----------|------------|---------------|-------------------|

| ANALOG I              | NPUT                                                 |                                                                                  |          |            |               | -                 |

| V <sub>Clipping</sub> | Maximum input voltage before clipping<br>output      | VINP – VINN                                                                      |          | ±320       |               | mV                |

| V <sub>FSR</sub>      | Specified linear full-scale input range              | VINP – VINN                                                                      | -250     |            | 250           | mV                |

| V <sub>CM</sub>       | Operating common-mode input voltage                  | (VINP + VINN) / 2 to GND1                                                        | -0.16    |            | VDD1 –<br>2.1 | v                 |

| V <sub>CMOV</sub>     | Common-mode overvoltage threshold                    | (VINP + VINN) / 2 to GND1                                                        | VDD1 – 2 |            |               | V                 |

| V <sub>CMOV_HYS</sub> | Hysteresis of common-mode over-<br>voltage threshold |                                                                                  |          | 100        |               | mV                |

| Vos                   | Input offset voltage                                 | Initial, at T <sub>A</sub> = 25°C,<br>VINP = VINN = GND1                         | -1       | ±0.05      | 1             | mV                |

| TCV <sub>OS</sub>     | Input offset voltage drift                           |                                                                                  | -4       | ±1         | 4             | μV/°C             |

| CMRR <sub>IN</sub>    | Input common-mode rejection ratio                    | DC, VINP = VINN<br>f <sub>IN</sub> = 10 kHz, VINP = VINN                         |          | -98<br>-98 |               | dB                |

| CIN                   | Single-ended input capacitance                       | $f_{\rm IN} = 275$ kHz, VINN = GND1                                              |          | 2          |               | pF                |

| C <sub>IND</sub>      | Differential input capacitance                       | f <sub>IN</sub> = 275 kHz                                                        |          | 1          |               | pF                |

| R <sub>IN</sub>       | Single-ended input resistance                        | VINN = GND1                                                                      |          | 19         |               | kΩ                |

| R <sub>IND</sub>      | Differential input resistance                        |                                                                                  |          | 22         |               | kΩ                |

| I <sub>IN</sub>       | Input current                                        | $VINP = VINN = GND1,$ $I_{IN} = (I_{INP} + I_{INN}) / 2$                         | -41      | -30        | -24           | μΑ                |

| TCI <sub>IN</sub>     | Input current drift                                  |                                                                                  |          | ±1         |               | nA/°C             |

| I <sub>INOS</sub>     | Input offset current                                 |                                                                                  |          | ±5         |               | nA                |

| BWIN                  | Input bandwidth                                      |                                                                                  |          | 1000       |               | kHz               |

| ANALOG C              | DUTPUT                                               | •                                                                                |          |            |               | •                 |

|                       | Gain <sup>1</sup>                                    | Initial, at T <sub>A</sub> = 25°C                                                |          | 8          |               | V/V               |

| E <sub>G</sub>        | Gain error                                           | Initial, at T <sub>A</sub> = 25°C                                                | -0.5%    | ±0.05%     | 0.5%          |                   |

| TCE <sub>G</sub>      | Gain error drift                                     |                                                                                  | -50      | ±15        | 50            | ppm/°0            |

| NL                    | Nonlinearity <sup>2</sup>                            |                                                                                  | -0.03%   | ±0.01%     | 0.03%         |                   |

| TCNL                  | Nonlinearity drift                                   |                                                                                  |          | ±1         |               | ppm/°(            |

|                       | Output noise                                         | VINP = VINN = GND1, BW = 100 kHz                                                 |          | 330        |               | μV <sub>RMS</sub> |

| THD                   | Total harmonic distortion                            | V <sub>IN</sub> = 500 mV <sub>pp</sub> , f <sub>IN</sub> = 10 kHz, BW = 100 kHz  |          | -85        |               | dB                |

| CNID                  |                                                      | V <sub>IN</sub> = 500 mV <sub>pp</sub> , f <sub>IN</sub> = 1 kHz, BW = 10<br>kHz | 83       |            |               | – dB              |

| SNR                   | Signal-to-noise ratio                                | V <sub>IN</sub> = 500 mV <sub>pp</sub> , f <sub>IN</sub> = 10 kHz, BW = 100 kHz  | 68       |            |               |                   |

|                       |                                                      | At VDD1, DC                                                                      |          | -100       |               |                   |

| סכסס                  | Power supply rejection ratio                         | At VDD1, 100-mV and 10-kHz ripple                                                |          | -90        |               |                   |

| PSRR                  | Power supply rejection ratio <sup>3</sup>            | At VDD2, DC                                                                      |          | -100       |               | dB                |

|                       |                                                      | At VDD2, 100-mV and 10-kHz ripple                                                |          | -98        |               |                   |

| V <sub>CMOUT</sub>    | Common-mode output voltage                           |                                                                                  | 1.39     | 1.45       | 1.51          | V                 |

| V <sub>FAILSAFE</sub> | Fail-safe differential output voltage                | $V_{CMOV} \le V_{CM}$ or VDD1 missing                                            |          | -2.53      | -2.43         | V                 |

| losc                  | Output short-circuit current                         | VOUTP or VOUTN shorts to VDD2 or<br>GND2                                         |          | ±13        |               | mA                |

| R <sub>OUT</sub>      | Output resistance                                    | On VOUTP or VOUTN                                                                |          | < 0.2      |               | Ω                 |

| BWOUT                 | Output bandwidth (-3 dB)                             |                                                                                  | 250      | 310        |               | kHz               |

| CMTI                  | Common-mode transient immunity                       | GND1 – GND2  = 1.5 kV; See Figure<br>8-1                                         | 100      | 150        |               | kV/μs             |

| POWER SU              | JPPLY                                                |                                                                                  | •        |            |               |                   |

| VDD <sub>UV</sub>     | VDD undervoltage threshold                           | VDD1 or VDD2 rising                                                              |          | 2.5        | 2.7           | V                 |

### Version 1.01, 2022/12/20

| 上海川土微电子有限公司 |

|-------------|

|             |

| וחחו                                |                                      | $3.0 \text{ V} \leq \text{VDD1} \leq 3.6 \text{ V}$ | 9.3  | 14.0 |     |

|-------------------------------------|--------------------------------------|-----------------------------------------------------|------|------|-----|

| IDD1                                | High-side supply current             | $4.5 V \le VDD1 \le 5.5 V$                          | 10.7 | 15.5 | mA  |

| 10.02                               | Loui cido cumplu ourront             | 3.0 V ≤ VDD2 ≤ 3.6 V                                | 5.2  | 7.2  |     |

| IDD2                                | Low-side supply current              | $4.5 \text{ V} \leq \text{VDD2} \leq 5.5 \text{ V}$ | 5.7  | 8.0  | mA  |

|                                     |                                      |                                                     |      |      |     |

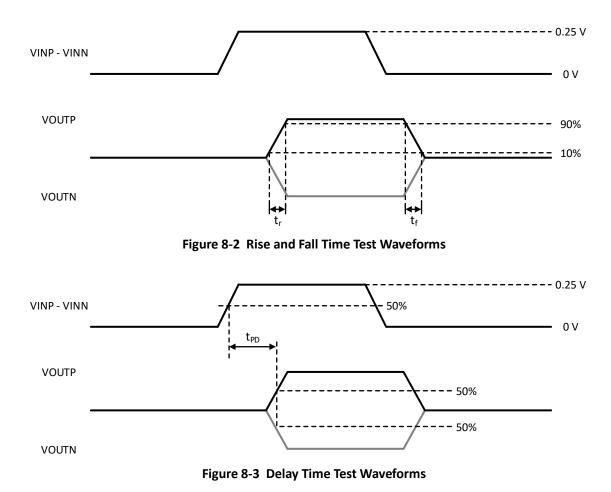

| t <sub>r</sub> Rise time of VO      | Rise time of VOUT (10% – 90%)        | VINP = 0 to 0.25 V step;                            | 1.2  |      |     |

|                                     |                                      | See Figure 8-2                                      | 1.2  |      | μs  |

| +                                   | Fall time of VOUT (90% – 10%)        | VINP = 0.25 V to 0 step;                            | 1.2  |      | μs  |

| $t_f$ Fall time of VOUT (90% – 10%) |                                      | See Figure 8-2                                      | 1.2  |      | μ   |

| $t_{PD}$                            | VIN to VOUT signal delay (50% – 50%) | Output unfiltered; See Figure 8-3                   | 1.5  | 2.1  | μs  |

| t <sub>AS</sub>                     | Analog settling time                 | VDD1 = 0 to 3 V step and 3.0 V $\leq$               | 500  |      | 110 |

|                                     | Analog setting tille                 | VDD2, to VOUT valid (0.1% settling)                 | 500  |      | μs  |

| NOTE.                               |                                      |                                                     |      |      |     |

#### NOTE:

-

The gain is defined as the slope of the optimum line derived by the method of least squares between differential input voltage (VINP – VINN) and differential output voltage (VOUTP – VOUTN) over the specified input range.

2. Nonlinearity is defined as a fraction of the half of the peak-to-peak value of differential output voltage deviation divided by the full-scale differential output voltage.

3. This parameter is input referred.

Version 1.01, 2022/12/20

CHIPANALOG 上海川土微电子有限公司

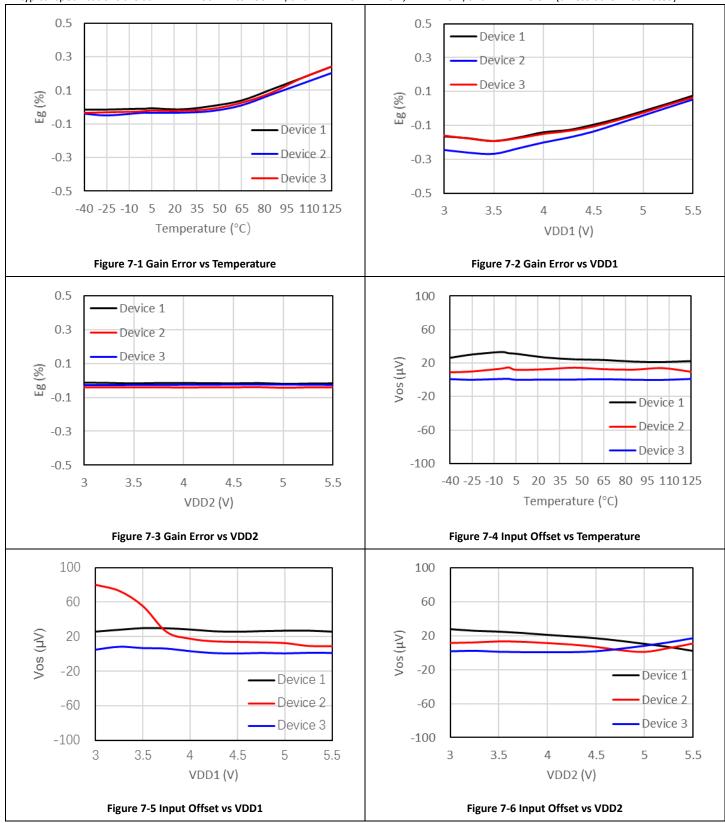

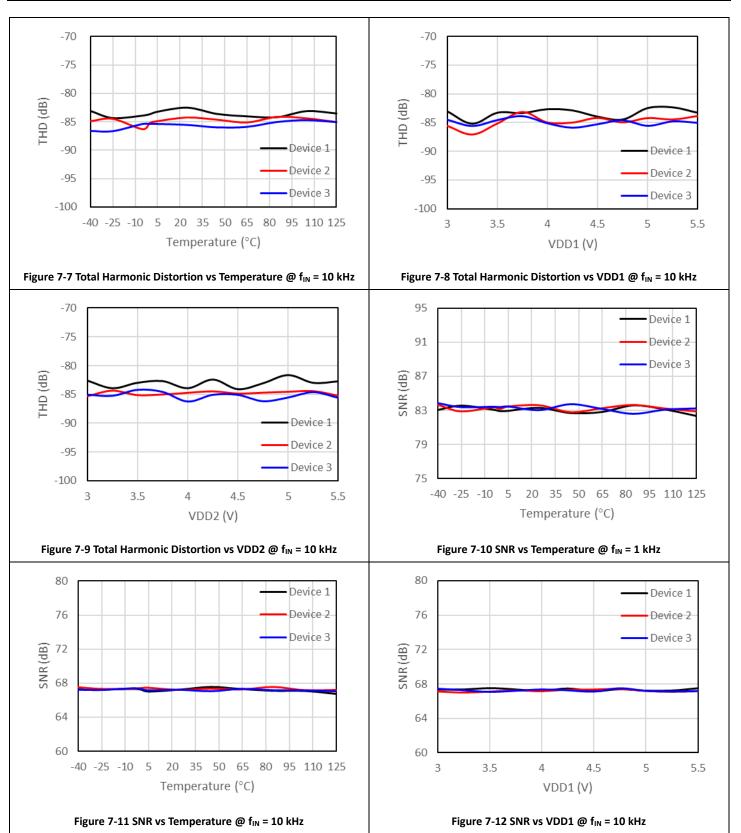

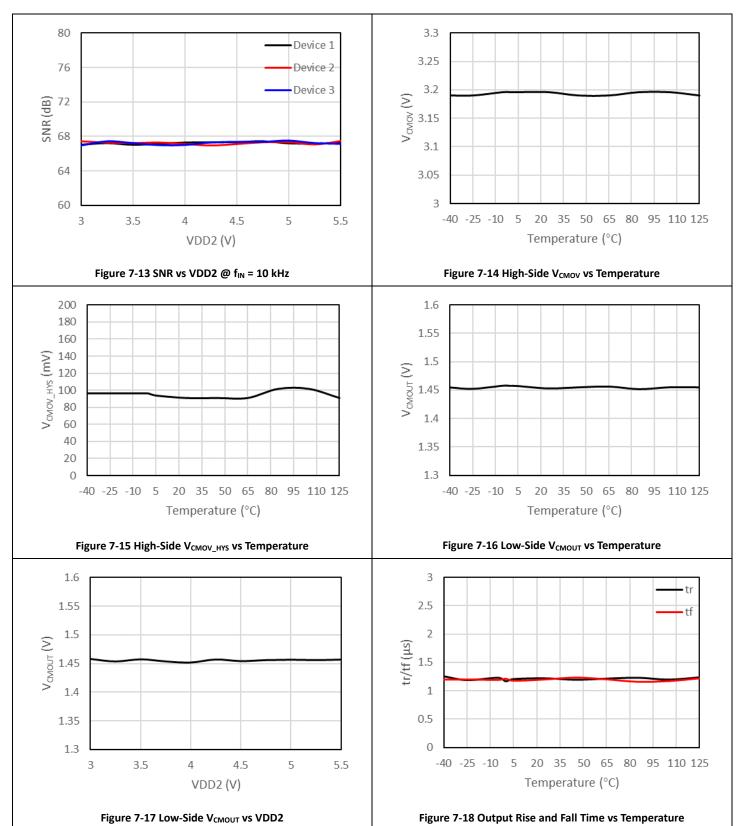

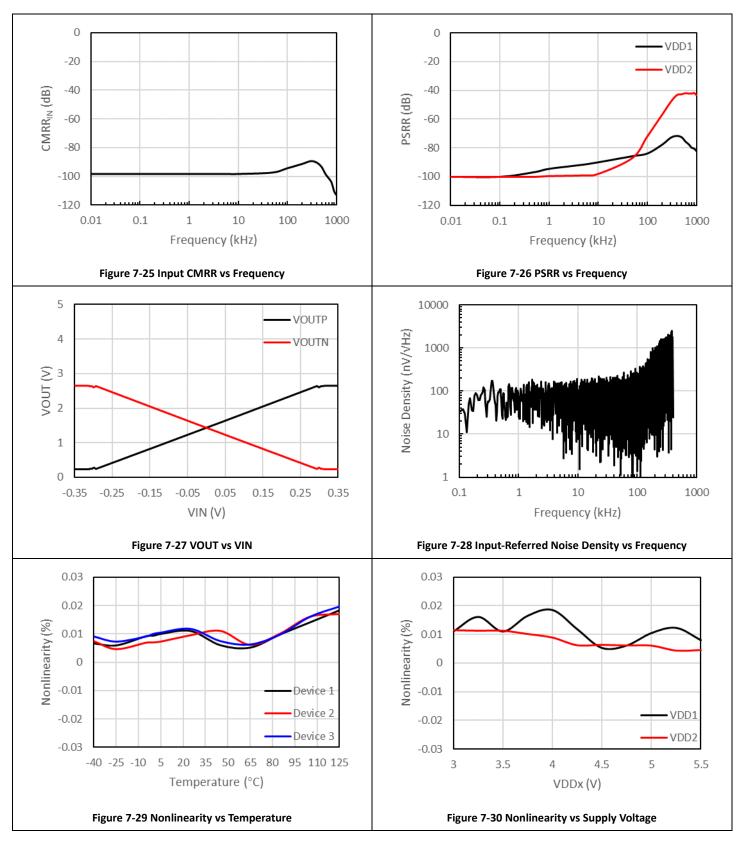

# 7.9 Typical Characteristics

All typical specifications are at VINP = -250 mV to 250 mV, and VINN = GND1 = 0 V, VDD1 = 5 V, and VDD2 = 3.3 V (unless otherwise noted).

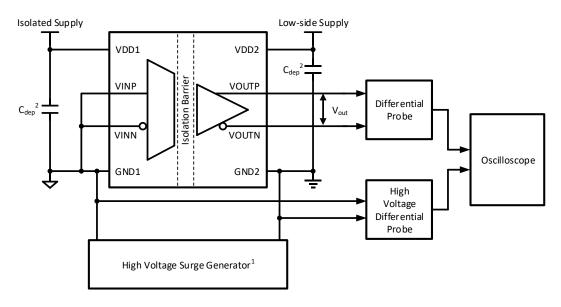

# 8 Parameter Measurement Information

#### Note:

- 1. The High Voltage Surge Generator generates repetitive high voltage surges with > 1 kV amplitude and < 10 ns rise time or fall time to generate common-mode transient noise with > 150 kV/μs slew rate.

- 2.  $C_{dep}$  is the 0.1~1  $\mu$ F decoupling capacitor.

CHIPANALOG 上海川土微电子有限公司

# Version 1.01, 2022/12/20 9 Detailed Description

### 9.1 System Overview

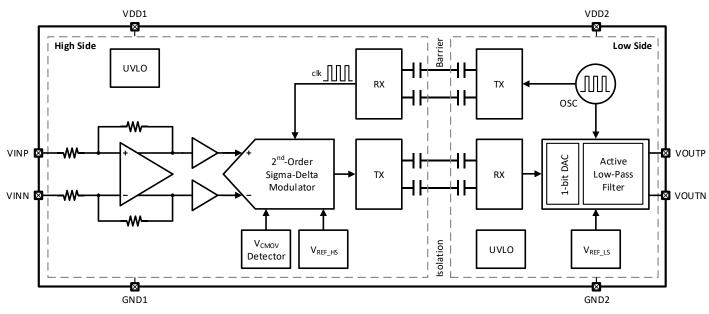

The CA-IS1200 devices are high-precision isolated amplifiers designed for shunt-resistor-based current sensing. The functional block diagram of this device is shown in Figure 9-1. At high side, the fully differential amplifier pre-amplifies the measuring voltage across a shunt resistor and then drives a 2<sup>nd</sup>-order Sigma-Delta ( $\Sigma\Delta$ ) modulator. This modulator converts the analog signal to a digital bitstream. For transmission across the SiO<sub>2</sub>-based isolation barrier, the digital stream is further modulated with a high-frequency carrier using a simple on-off keying (OOK) modulation scheme. The receiver (RX) recoveries the modulated signal to the original digital bitstream at low side. After processed by a 1-bit digital-to-analog converter (DAC), the digital bitstream is sent to an active low-pass filter to produce the analog output. For synchronization of the whole chip, the clock is generated at low side and sent back to high side ensuring that all clocks come from one source.

Figure 9-1 Functional Block Diagram of CA-IS1200

# 9.2 Feature Description

# 9.2.1 Analog Input

The CA-IS1200 device utilizes a fully differential amplifier stage to pre-amplify the measuring voltage across the shunt resistor. The nominal gain of the front-end differential amplifier is 4, contributing part of the total gain and ensuring that the 2<sup>nd</sup>-order Sigma-Delta modulator is not saturated when the analog input is within the specific input voltage range. This gain is set by the internal high-precision resistor network. The tens-of-several-k $\Omega$  input resistance means it can bring in more gain error and offset if CA-IS1200 devices are applied in measurement where the input signal sources are high-impedance (refer to Error Analysis in Voltage Sensing for detailed information).

The ESD structure of CA-IS1200 supports the absolute maximum analog input voltage (with respect to GND1) to range from GND1 - 6 V to VDD1 + 0.5 V. To guarantee the long-term reliability and device performance, the differential analog input voltage and the input common-mode voltage of CA-IS1200 must be kept within the specific range.

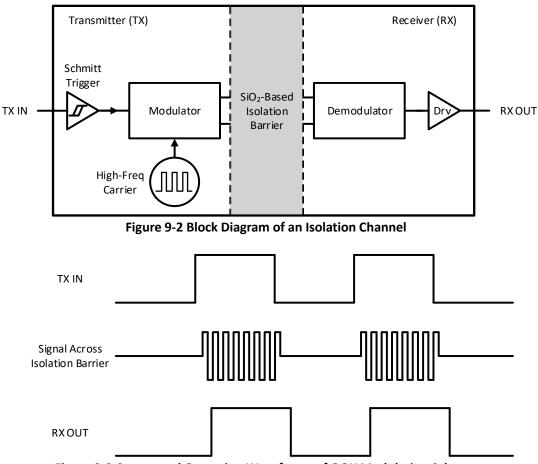

# 9.2.2 Signal Transmission Across Isolation Barrier

The CA-IS1200 devices utilize a simple on-off keying (OOK) modulation scheme to transmit the digital bitstream across the SiO<sub>2</sub>based isolation barrier which supports up to 3750-V<sub>RMS</sub> (CA-IS1200U) or 5000-V<sub>RMS</sub> (CA-IS1200G) galvanic isolation between high- and low-voltage domain. The block diagram of an isolation channel is shown in Figure 9-2. As shown in Figure 9-3, the transmitter (TX) modulates the digital bitstream with a high-frequency carrier when the signal is HIGH while sends no signal

# CA-IS1200U, CA-IS1200G Version 1.01, 2022/12/20

when the signal is LOW. The receiver (RX) demodulates the signal across the isolation barrier and reproduces the digital bitstream faithfully. The isolation channel adopts fully differential capacitive-coupled structure which is insensitive to common-mode transient noises, thus the CMTI performance can be maximized. This structure and related circuitry also provide low emissions and strong anti-interference capability from magnetic changes.

Figure 9-3 Conceptual Operation Waveforms of OOK Modulation Scheme

# 9.2.3 Fail-Safe Output

The CA-IS1200 devices have fail-safe output function which is activated in two conditions:

- The high-side power supply is missing;

- The common-mode input voltage V<sub>CM</sub> exceeds the common-mode overvoltage threshold V<sub>CMOV</sub>.

As shown in Figure 9-4 and Figure 9-5, the fail-safe output is a more negative differential output voltage which can be distinguished from the negative clipping output voltage. This function contributes to fault diagnostics and system safety.

| 02              | <mark>3</mark> 500¢/                | ′ <mark>4</mark> 500⊽/ | * 880.0  | 50.00%/ 停止 | 🗜 🚹 1430 | 0 2                                                | <mark>3</mark> 5000/ <mark>4</mark> 5                                         | 5000/ 🔆 880.0                                                    | 양 50.00%/ 停止                                                          | 🗜 🚺 1430                                                                                                        |

|-----------------|-------------------------------------|------------------------|----------|------------|----------|----------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                 |                                     |                        | -        |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        |          |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        | -        |            |          | the statistical in the limit is many slite surgest | bried maar til kali van til kali kiel geet meer tie bried op het meer ken wat | <mark>់  </mark><br>សោយមាននេះស្រោយស្រែបីស្រីសូមីព្រះសារស្រែបូមីស | Alt Dynalis di Kolstvely, kriji bi konstituturi, din konstituturi, di | an substanting the second s |

|                 |                                     |                        |          |            |          | aritemen. Jupite Includents methodise              |                                                                               |                                                                  | er werk eine der eine die der die | aljadni un etnini Caarlantini II. da                                                                            |

|                 |                                     |                        | -        |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        |          |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        |          | -2.536 V   |          |                                                    | VC                                                                            | TUOV – ATU                                                       | v − _2 372 V                                                          |                                                                                                                 |

|                 |                                     | v001r -                | V00111 - | -2.550 V   |          |                                                    | v.                                                                            | 011 - 00011                                                      | V = -2.372 V                                                          |                                                                                                                 |

|                 |                                     |                        | -        |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        | -        |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     | ,                      | Ţ        |            |          |                                                    |                                                                               | an di camana a di Mana a Vilan Indonesia                         |                                                                       |                                                                                                                 |

| VOUTP           |                                     |                        | -        |            |          | <b>₽</b> VOUTP                                     |                                                                               |                                                                  |                                                                       |                                                                                                                 |

|                 |                                     |                        | -        |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

| 平均值(3): 135.8mV |                                     | ): 2.6719V             |          |            |          | 平均值(3): 213.5mV                                    | 平均值(4): 2.58                                                                  |                                                                  |                                                                       |                                                                                                                 |

| ◆ 源<br>VOUTP �  | 测量选择<br>平均值                         | 测试<br>平均值              | 设置       | 清除測量值      | 统计信息     | ● 源<br>VOUTP <b>②</b> 派                            | 测量选择 测<br>平均值 平均                                                              | 试                                                                | 清除測量值                                                                 | 统计信息                                                                                                            |

|                 | Figure 9-4 Typical Fail-Safe Output |                        |          |            |          |                                                    |                                                                               |                                                                  |                                                                       |                                                                                                                 |

10 Application and Implementation

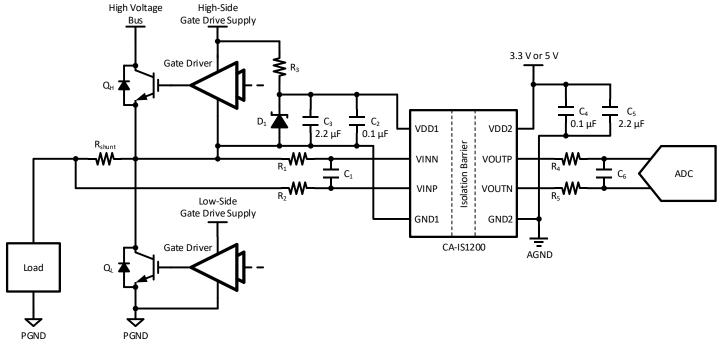

### **10.1.1 Typical Application for Current Sensing**

#### Figure 10-1 Typical Application for Current Sensing

The typical application for current sensing is shown in Figure 10-1. The CA-IS1200 device is used to amplify the voltage across the shunt resistor ( $R_{shunt}$ ) and transmit it to the low-voltage side for control circuit to process. The differential input and the high CMTI of CA-IS1200 ensure the reliable and accurate measurement in the high-noise and high-power switching applications such as industrial motor drives. The voltage of  $R_{shunt}$  with respect to PGND varies from 0 V to the high voltage bus when switching, thus isolation is required. The CA-IS1200 devices support up to  $3750-V_{RMS}$  (CA-IS1200U) or  $5000-V_{RMS}$  (CA-IS1200G) galvanic isolation, making them suitable for these high-voltage industrial applications.

In a three-phase motor drive application, this circuit could be repeated three times and one for each phase in order to measure each phase current.

#### 10.1.2 Choose Proper R<sub>shunt</sub>

The value chosen of shunt resistor is a trade off between power dissipation and measuring accuracy. Small value resistors minimize power dissipation, while large value resistors take advantage of the full performance input range of the Sigma-Delta modulator.

Consider the following restrictions to choose proper value of the shunt resistor R<sub>shunt</sub>:

- The voltage drop across R<sub>shunt</sub> caused by the nominal measured current is within the linear differential input voltage range V<sub>FSR</sub>;

- The voltage drop across R<sub>shunt</sub> caused by the maximum allowed current must not exceed the maximum input voltage before clipping output |V<sub>Clipping</sub>|.

For best performance, place the shunt resistor close to the inputs of CA-IS1200 and keep the layout of both connections symmetrical. This ensures that any noises occurring at high side are coupled equally to the inputs and would be rejected as a

# CA-IS1200U, CA-IS1200G Version 1.01, 2022/12/20

common-mode signal. Kelvin connection is recommended between R<sub>shunt</sub> and the inputs of CA-IS1200 to remove the impact from any voltage drops across the trace and leads.

# 10.1.3 Input Filter

The typical input bandwidth of CA-IS1200 is 1 MHz. A first-order passive RC low-pass filter could be placed between  $R_{shunt}$  and the inputs to narrow the input bandwidth. Choose  $R_1 = R_2 = 10 \Omega$  and  $C_1 = 20 \text{ nF}$  could provide a cutoff frequency of approximately 400 kHz.  $R_1$  and  $R_2$  should be low-value enough compared to the input impedance of CA-IS1200 to reduce gain error.

# **10.1.4 Power Supply Recommendations**

The high-side power supply of CA-IS1200 could be generated directly derived from the high-side gate drive power supply by utilizing a Zener diode (D<sub>1</sub>) to produce a 3.3-V or 5-V ( $\pm$ 10%) voltage. And a low-ESR decoupling capacitor of 0.1  $\mu$ F (C<sub>2</sub>) is recommended to place as close as possible to the VDD1 pin of CA-IS1200. Additional 2.2- $\mu$ F capacitor (C<sub>3</sub>) is recommended for better filtering to the high-side power-supply path.

Similarly, a 0.1- $\mu$ F decoupling capacitor (C<sub>4</sub>) followed by an additional capacitor (C<sub>5</sub>) from 2.2  $\mu$ F to 10  $\mu$ F should be placed as close as to the VDD2 pin of CA-IS1200 to filter the low-side power supply path.

Figure 10-2 Typical Application for Voltage Sensing

# 10.1.5 Output Filter

Another first-order passive RC low-pass filter could be placed between the outputs of CA-IS1200 and the ADC to satisfy the potential requirement for anti-aliasing filtering. The characteristics of this filter depends on the structure and sampling frequency of the ADC. Choose  $R_4 = R_5 = 4.7 \text{ k}\Omega$  and  $C_6 = 180 \text{ pF}$  could provide a cutoff frequency of approximately 94 kHz.

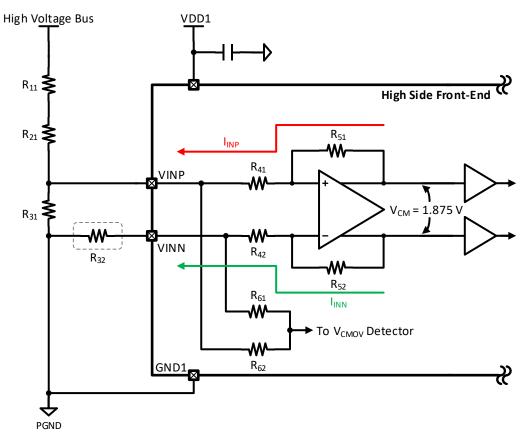

# 10.1.6 Error Analysis in Voltage Sensing

The CA-IS1200 devices may also be used in the applications of voltage sensing as shown in Figure 10-2. The resistors  $R_{11}$ ,  $R_{21}$  and  $R_{31}$  make up the resistor divider to scale down the high voltage from bus. Typically, the value of  $R_{11}$  and  $R_{21}$  is much larger than  $R_{31}$  to keep the input voltage of CA-IS1200 within the specific range.

In CA-IS1200, resistors  $R_{41}$  and  $R_{51}$  (or  $R_{42}$  and  $R_{52}$ ) are used to set the gain of front-end amplifier. The typical values are  $R_{41} = R_{42} = 12.5 \text{ k}\Omega$  and  $R_{51} = R_{52} = 50 \text{ k}\Omega$ . Resistors  $R_{61}$  and  $R_{62}$  are used to sense the common-mode voltage of the input in CA-IS1200. The typical values are  $R_{61} = R_{62} = 100 \text{ k}\Omega$ .

First, consider the situation in which  $R_{32}$  is not used. Additional gain error and offset would arise in these applications for CA-IS1200. On the one hand, the limited input impedance of CA-IS1200 is parallel with the external sensing resistor  $R_{31}$ , resulting in impedance change and thus additional gain error. On the other hand, the output common-mode voltage  $V_{CM}$  of the front-end differential amplifier in CA-IS1200 is biased to 1.875 V, which would generate bias current  $I_{INP}$  and  $I_{INN}$  flowing through the front-end resistor network. The bias current  $I_{INP}$  also flows through  $R_{31}$  while  $I_{INN}$  flows directly to PGND in the case of omitting  $R_{32}$ , which results in unbalance and thus additional offset.

To eliminate the effect of the bias current, resistor  $R_{32}$  equal to sensing resistor  $R_{31}$  is recommended to be added between VINN and PGND. The resistor  $R_{31}$  would bring in additional gain error  $E_{GA}$  and could be calculated as Eq. 1 describes.

$$E_{GA} = R_{31} / (R_{31} + R_{41})$$

(Eq. 1)

To reduce the effect of this gain error, the value of  $R_{31}$  should be chosen much smaller compared to  $R_{41}$ . And this gain error could also be minimized by the system-level gain calibration.

### 10.1.7 Caution

Do not leave the inputs of CA-IS1200 floating. If the VINP and VINN are left floating, the input common-mode voltage would be pulled to a high level by internal bias, which could activate the fail-safe mode under certain power supply and may lead to system-level abnormal reaction (refer to Fail-Safe Output for detailed information).

# Version 1.01, 2022/12/20

# 11 Package Information

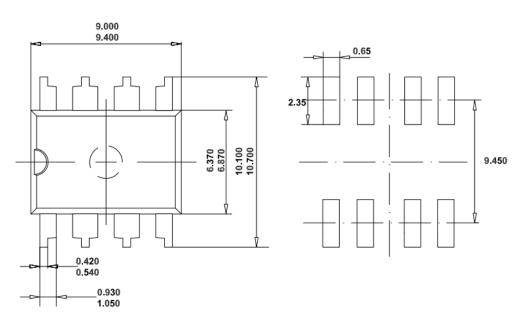

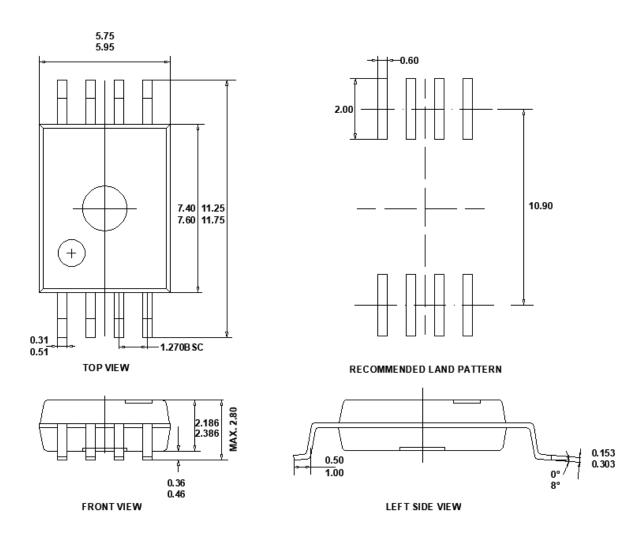

### 11.1 DUB8 Package

The figure below illustrates the package details for the CA-IS1200U isolated amplifier in an 8-pin DUB package. The values for the dimensions are shown in millimeters.

TOP VIEW

RECOMMENDED LAND PATTERN

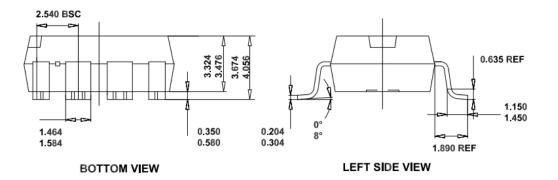

# 11.2 Wide Body SOIC8 Package

The figure below illustrates the package details and the recommended land pattern details for the CA-IS1200G isolated amplifier in an 8-pin wide-body SOIC package. The values for the dimensions are shown in millimeters.

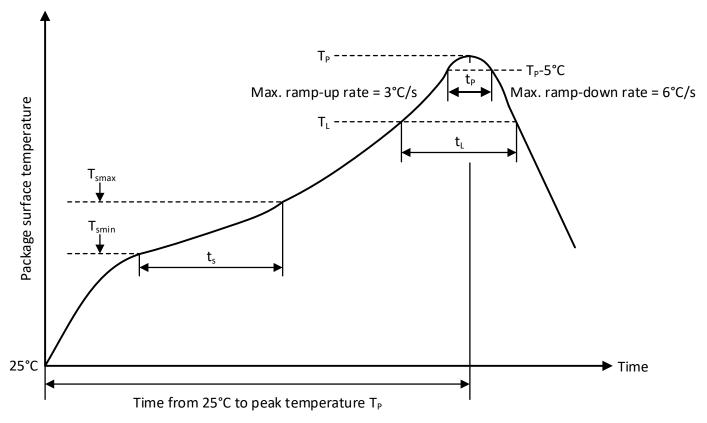

# 12 Soldering Information

# Figure 12-1 Soldering Temperature Curve

| Profile Feature                                                        | Pb-Free Soldering |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------|-------------------|--|--|--|--|--|--|--|--|

| Ramp-up rate ( $T_L$ = 217°C to peak $T_P$ )                           | 3°C/s max         |  |  |  |  |  |  |  |  |

| Time $t_s$ of preheat temp ( $T_{smin}$ = 150°C to $T_{smax}$ = 200°C) | 60~120 seconds    |  |  |  |  |  |  |  |  |

| Time $t_L$ to be maintained above 217°C                                | 60~150 seconds    |  |  |  |  |  |  |  |  |

| Peak temperature T <sub>P</sub>                                        | 260°C             |  |  |  |  |  |  |  |  |

| Time t <sub>P</sub> within 5°C of actual peak temp                     | 30 seconds max    |  |  |  |  |  |  |  |  |

| Ramp-down rate (peak $T_P$ to $T_L = 217^{\circ}C$ )                   | 6°C/s max         |  |  |  |  |  |  |  |  |

| Time from 25°C to peak temperature T <sub>P</sub>                      | 8 minutes max     |  |  |  |  |  |  |  |  |

**Table 12-1 Soldering Temperature Parameters**

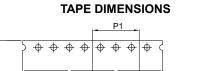

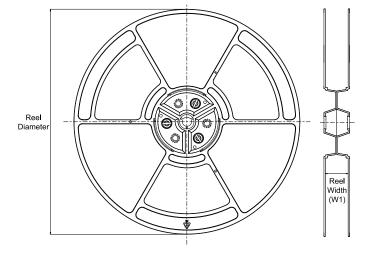

# **13** Tape and Reel Information

|    | A0<br>K0                                                  |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| К0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

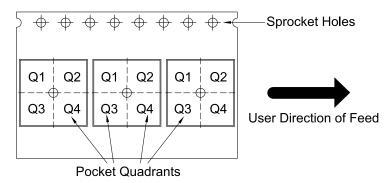

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadran<br>t |

|------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|----------------------|

| CA-IS1200U | DUB             | U                  | 8    | 800  | 330                      | 24.4                     | 10.90      | 9.60       | 4.30       | 16.00      | 24.00     | Q1                   |

| CA-IS1200G | SOIC            | G                  | 8    | 1000 | 330                      | 16.4                     | 11.95      | 6.15       | 3.20       | 16.00      | 16.00     | Q1                   |

# 14 Important Notice

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

### **Trademark Information**

Chipanalog Inc. <sup>®</sup>, Chipanalog<sup>®</sup> are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com