### **FEATURES**

| Count Resolution ±19,999                            |

|-----------------------------------------------------|

| Resolution on 200 mV Scale 10μλ                     |

| True Differential Input and Reference               |

| Low Power Consumption500µA at 9\                    |

| Direct LCD Driver for 4-1/2 Digits, Decimal Points, |

| Low-Battery Indicator, and Continuity Indicator     |

| Overrange and Underrange Outputs                    |

| Range Select Input10:1                              |

| High Common-Mode Rejection Ratio 110dE              |

**External Phase Compensation Not Required**

#### ORDERING INFORMATION

|           | Pin    |             | Temperature  |

|-----------|--------|-------------|--------------|

| Part No.  | Layout | Package     | Range        |

| TC7129CKW | Formed | 44-Pin PQFP | 0°C to +70°C |

| TC7129CLW | _      | 44-Pin PLCC | 0°C to +70°C |

| TC7129CPL | Normal | 40-Pin PDIP | 0°C to +70°C |

#### **GENERAL DESCRIPTION**

The TC7129 is a 4-1/2 digit analog-to-digital converter (ADC) that directly drives a multiplexed liquid crystal display (LCD). Fabricated in high-performance, low-power CMOS, the TC7129 ADC is designed specifically for high-resolution, battery-powered digital multimeter applications. The traditional dual-slope method of A/D conversion has been enhanced with a successive integration technique to produce readings accurate to better than 0.005% of full scale, and resolution down to  $10\mu V$  per count.

The TC7129 includes features important to multimeter applications. It detects and indicates low-battery condition. A continuity output drives an annunciator on the display, and can be used with an external driver to sound an audible alarm. Overrange and underrange outputs and a range-change input provide the ability to create auto-ranging instruments. For snapshot readings, the TC7129 includes a latch-and-hold input to freeze the present reading. This combination of features makes the TC7129 the ideal choice for full-featured multimeter and digital measurement applications.

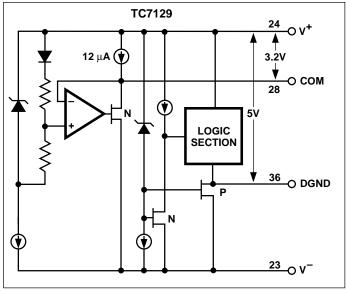

#### TYPICAL OPERATING CIRCUIT

© 2001 Microchip Technology Inc. DS21459A

# **TC7129**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )                       |

|--------------------------------------------------------------------------|

| V <sub>DISP</sub> V <sup>+</sup> to (DGND – 0.3V)<br>Digital Input, Pins |

| 1, 2, 19, 20, 21, 22, 27, 37, 39, 40 DGND to V <sup>+</sup>              |

| Analog Input, Pins 25, 29, 30 V+ to V-                                   |

| Package Power Dissipation (T <sub>A</sub> ≤ 70°C)                        |

| Plastic DIP1.23W                                                         |

| PLCC1.23W                                                                |

| Plastic QFP1.00W                                                         |

| Operating Temperature Range0°C to +70°C                                  |

| Storage Temperature Range – 65°C to +150°C                               |

| Lead Temperature (Soldering, 10 sec)+300°C                               |

**Notes:** Input voltages may exceed supply voltages, provided input current is limited to  $\pm 400~\mu A$ . Currents above this value may result in invalid display readings but will not destroy the device if limited to  $\pm 1~mA$ .

Dissipation ratings assume device is mounted with all leads soldered to printed circuit board.

\*Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS:** $V^+$ to $V^- = 9V$ , $V_{REF} = 1V$ , $T_A = +25^{\circ}C$ , $f_{CLK} = 120$ kHz, unless otherwise indicated. Pin numbers refer to 40-pin DIP.

| Symbol               | Parameter                                           | eter Test Conditions                                                                  |            |                                                | Max      | Unit              |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|------------|------------------------------------------------|----------|-------------------|

| Input                |                                                     |                                                                                       |            |                                                |          |                   |

|                      | Zero Input Reading                                  | V <sub>IN</sub> = 0V, 200mV Scale                                                     | -0000      | 0000                                           | +0000    | Counts            |

|                      | Zero Reading Drift                                  | $V_{IN} = 0V, 0^{\circ}C < T_A < +70^{\circ}C$                                        | _          | ±0.5                                           | _        | μV/°C             |

|                      | Ratiometric Reading                                 | V <sub>IN</sub> = V <sub>REF</sub> = 1000mV, Range = 2V                               | 9997       | 9999                                           | 10000    | Counts            |

|                      | Range Change Accuracy                               | V <sub>IN</sub> = 0.1V on Low Range<br>÷V <sub>IN</sub> = 1V on High Range            | 0.9999     | 1.0000                                         | 1.0001   | Ratio             |

| RE                   | Roll-Over Error                                     | $-V_{IN} = +V_{IN} = 199mV$                                                           | _          | 1                                              | 2        | Counts            |

| NL                   | Linearity Error                                     | 200 mV Scale                                                                          | _          | 1                                              | _        | Counts            |

| CMRR                 | Common-Mode Rejection Ratio                         | V <sub>CM</sub> = 1V, V <sub>IN</sub> = 0V, 200mV Scale                               | _          | 110                                            | _        | dB                |

| CMVR                 | Common-Mode Voltage Range                           | V <sub>IN</sub> = 0V<br>200 mV Scale                                                  | _          | (V <sup>-</sup> ) +1.5<br>(V <sup>+</sup> ) -1 | _        | V<br>V            |

| e <sub>N</sub>       | Noise (Peak-to-Peak Value Not Exceeded 95% of Time) | V <sub>IN</sub> = 0V<br>200mV Scale                                                   | _          | 14                                             | _        | μV <sub>P-P</sub> |

| I <sub>IN</sub>      | Input Leakage Current                               | V <sub>IN</sub> = 0V, Pins 32, 33                                                     | _          | 1                                              | 10       | pA                |

|                      | Scale Factor Temperature Coefficient                | $V_{IN}$ = 199mV, 0°C < T <sub>A</sub> < +70°C<br>External V <sub>REF</sub> = 0ppm/°C | _          | 2                                              | 7        | ppm/°C            |

| Power                |                                                     |                                                                                       |            |                                                |          |                   |

| $\overline{V_{COM}}$ | Common Voltage                                      | V <sup>+</sup> to Pin 28                                                              | 2.8        | 3.2                                            | 3.5      | V                 |

|                      | Common Sink Current Common Source Current           | $\Delta$ Common = +0.1V<br>$\Delta$ Common = -0.1V                                    | _          | 0.6<br>10                                      | _        | mA<br>μA          |

| DGND                 | Digital Ground Voltage                              | $V^{+}$ to Pin 36, $V^{+}$ to $V^{-} = 9V$                                            | 4.5        | 5.3                                            | 5.8      | V                 |

|                      | Sink Current                                        | $\Delta$ DGND = +0.5V                                                                 | _          | 1.2                                            | _        | mA                |

|                      | Supply Voltage Range                                | V+ to V-                                                                              | 6          | 9                                              | 12       | V                 |

| Is                   | Supply Current Excluding Common Current             | V+ to V- = 9V                                                                         | _          | 0.8                                            | 1.3      | mA                |

| f <sub>CLK</sub>     | Clock Frequency                                     |                                                                                       | _          | 120                                            | 360      | kHz               |

|                      | V <sub>DISP</sub> Resistance                        | V <sub>DISP</sub> to V <sup>+</sup>                                                   | _          | 50                                             | _        | kΩ                |

|                      | Low-Battery Flag Activation Voltage                 | V <sup>+</sup> to V <sup>-</sup>                                                      | 6.3        | 7.2                                            | 7.7      | V                 |

| Digital              |                                                     |                                                                                       |            |                                                |          |                   |

|                      | Continuity Comparator Threshold Voltages            | V <sub>OUT</sub> Pin 27 = High<br>V <sub>OUT</sub> Pin 27 = Low                       | 100<br>—   | 200<br>200                                     | —<br>400 | mV<br>mV          |

|                      | Pull-Down Current                                   | Pins 37, 38, 39                                                                       | <b> </b> _ | 2                                              | 10       | μΑ                |

# **TC7129**

**ELECTRICAL CHARACTERISTICS:**  $V^+$  to  $V^- = 9V$ ,  $V_{REF} = 1V$ ,  $T_A = +25^{\circ}C$ ,  $f_{CLK} = 120$  kHz, unless otherwise indicated. Pin numbers refer to 40-pin DIP.

| Symbol | Parameter             | Test Conditions         | Min | Тур | Max | Unit |

|--------|-----------------------|-------------------------|-----|-----|-----|------|

|        | "Weak Output" Current | Pins 20, 21 Sink/Source | _   | 3/3 | _   | μΑ   |

|        | Sink/Source           | Pin 27 Sink/Source      |     | 3/9 | _   | μA   |

|        | Pin 22 Source Current |                         | _   | 40  | _   | μΑ   |

|        | Pin 22 Sink Current   |                         | _   | 3   | _   | μΑ   |

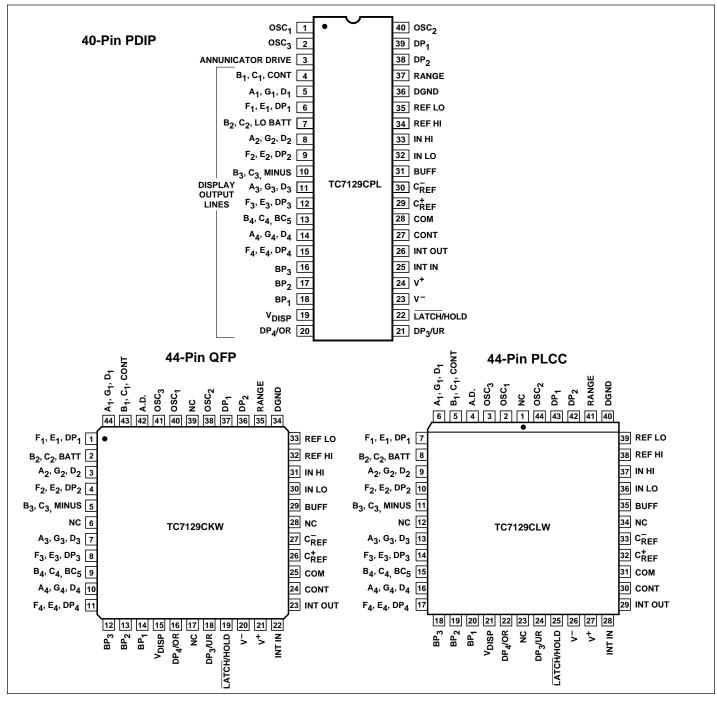

#### **PIN CONFIGURATIONS**

# TC7129

# **PIN DESCRIPTIONS**

| Pin No.<br>40-Pin<br>TC7129CPL | Pin No.<br>44-Pin<br>TC7129CKW | Pin No.<br>44-Pin<br>TC7129CLW | V Symbol                                          | Function                                                                                                                                                                                                                                                                                                                               |

|--------------------------------|--------------------------------|--------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                              | 40                             | 2                              | OSC <sub>1</sub>                                  | Input to first clock inverter.                                                                                                                                                                                                                                                                                                         |

| 2                              | 41                             | 3                              | OSC <sub>3</sub>                                  | Output of second clock inverter.                                                                                                                                                                                                                                                                                                       |

| 3                              |                                |                                | ANNUNCIATOR                                       | Backplane square-wave output for driving annunciators.                                                                                                                                                                                                                                                                                 |

| 4                              | 43                             | 5                              | B <sub>1</sub> , C <sub>1</sub> , CONT            | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 5                              | 44                             | 6                              | A <sub>1</sub> , G <sub>1</sub> , D <sub>1</sub>  | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 6                              | 1                              | 7                              | F <sub>1</sub> , E <sub>1</sub> , DP <sub>1</sub> | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 7                              | 2                              | 8                              | B <sub>2</sub> , C <sub>2</sub> , LO BATT         | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 8                              | 3                              | 9                              | A <sub>2</sub> , G <sub>2</sub> , D <sub>2</sub>  | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 9                              | 4                              | 10                             | F <sub>2</sub> , E <sub>2</sub> , DP <sub>2</sub> | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 10                             | 5                              | 11                             | B <sub>3</sub> , C <sub>3</sub> , MINUS           | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 11                             | 7                              | 13                             | A <sub>3</sub> , G <sub>3</sub> , D <sub>3</sub>  | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 12                             | 8                              | 14                             | F <sub>3</sub> , E <sub>3</sub> , DP <sub>3</sub> | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 13                             | 9                              | 15                             | B <sub>4</sub> , C <sub>4</sub> , BC <sub>5</sub> | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 14                             | 10                             | 16                             | A <sub>4</sub> , D <sub>4</sub> , G <sub>4</sub>  | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 15                             | 11                             | 17                             | F <sub>4</sub> , E <sub>4</sub> , DP <sub>4</sub> | Output to display segments.                                                                                                                                                                                                                                                                                                            |

| 16                             | 12                             | 18                             | BP <sub>3</sub>                                   | Backplane #3 output to display.                                                                                                                                                                                                                                                                                                        |

| 17                             | 13                             | 19                             | BP <sub>2</sub>                                   | Backplane #2 output to display.                                                                                                                                                                                                                                                                                                        |

| 18                             | 14                             | 20                             | BP <sub>1</sub>                                   | Backplane #1 output to display.                                                                                                                                                                                                                                                                                                        |

| 19                             | 15                             | 21                             | V <sub>DISP</sub>                                 | Negative rail for display drivers.                                                                                                                                                                                                                                                                                                     |

| 20                             | 16                             | 22                             | DP <sub>4</sub> /OR                               | Input: When HI, turns on most significant decimal point. Output: Pulled HI when result count exceeds $\pm 19,999$ .                                                                                                                                                                                                                    |

| 21                             | 18                             | 24                             | DP <sub>3</sub> /UR                               | Input: Second most significant decimal point on when HI. Output: Pulled HI when result count is less than $\pm 1000$ .                                                                                                                                                                                                                 |

| 22                             | 19                             | 25                             | LATCH/HOLD                                        | Input: When floating, ADC operates in the free-run mode. When pulled HI, the last displayed reading is held. When pulled LO, the result counter contents are shown incrementing during the deintegrate phase of cycle.  Output: Negative-going edge occurs when the data latches are updated. Can be used for converter status signal. |

| 23                             | 20                             | 26                             | V-                                                | Negative power supply terminal.                                                                                                                                                                                                                                                                                                        |

| 24                             |                                | 27                             | V+                                                | Positive power supply terminal and positive rail for display drivers.                                                                                                                                                                                                                                                                  |

| 25                             | 21                             | 28                             | INT IN                                            | Input to integrator amplifier.                                                                                                                                                                                                                                                                                                         |

| 26                             | 23                             | 29                             | INT OUT                                           | Output of integrator amplifier.                                                                                                                                                                                                                                                                                                        |

| 27                             | 24                             | 30                             | CONTINUITY                                        | Input: When LO, continuity flag on the display is OFF. When HI, continuity flag is ON. Output: HI when voltage between inputs is less than +200 mV. LO when voltage between inputs is more than +200 mV.                                                                                                                               |

| 28                             | 25                             | 31                             | COMMON                                            | Sets common-mode voltage of 3.2V below V <sup>+</sup> for DE, 10X, etc. Can be used as preregulator for external reference.                                                                                                                                                                                                            |

| 29                             | 26                             | 32                             | C <sup>†</sup> <sub>REF</sub>                     | Positive side of external reference capacitor.                                                                                                                                                                                                                                                                                         |

| 30                             | 27                             | 33                             | C <sub>REF</sub>                                  | Negative side of external reference capacitor.                                                                                                                                                                                                                                                                                         |

| 31                             | 29                             | 35                             | BUFFER                                            | Output of buffer amplifier.                                                                                                                                                                                                                                                                                                            |

| 32                             | 30                             | 36                             | IN LO                                             | Negative input voltage terminal.                                                                                                                                                                                                                                                                                                       |

| 33                             | 31                             | 37                             | IN HI                                             | Positive input voltage terminal.                                                                                                                                                                                                                                                                                                       |

### TC7129

#### PIN DESCRIPTIONS

| Pin No.<br>40-Pin<br>TC7129CPL | Pin No.<br>44-Pin<br>TC7129CKW | Pin No.<br>44-Pin<br>TC7129CLW | Symbol           | Function                                                                         |

|--------------------------------|--------------------------------|--------------------------------|------------------|----------------------------------------------------------------------------------|

| 34                             | 32                             | 38                             | REF HI           | Positive reference voltage in                                                    |

| 35                             | 33                             | 39                             | REF LO           | Negative reference voltage                                                       |

| 36                             | 34                             | 40                             | DGND             | Internal ground reference for digital section. See "±5V Power Supply" paragraph. |

| 37                             | 35                             | 41                             | RANGE            | $3\mu\text{A}$ pulldown for 200mV scale. Pulled HI externally for 2V scale.      |

| 38                             | 36                             | 42                             | DP <sub>2</sub>  | Internal 3μA pulldown. When HI, decimal point 2 will be on.                      |

| 39                             | 37                             | 43                             | DP <sub>1</sub>  | Internal 3μA pulldown. When HI, decimal point 1 will be on.                      |

| 40                             | 38                             | 44                             | OSC <sub>2</sub> | Output of first clock inverter. Input of second clock inverter.                  |

|                                | 6,17, 28, 39                   | 12, 23, 34,1                   | NC               | No Connection                                                                    |

#### COMPONENT SELECTION

(All pin designations refer to 40-Pin DIP)

The TC7129 is designed to be the heart of a highresolution analog measurement instrument. The only additional components required are a few passive elements, a voltage reference, an LCD, and a power source. Most component values are not critical; substitutes can be chosen based on the information given below.

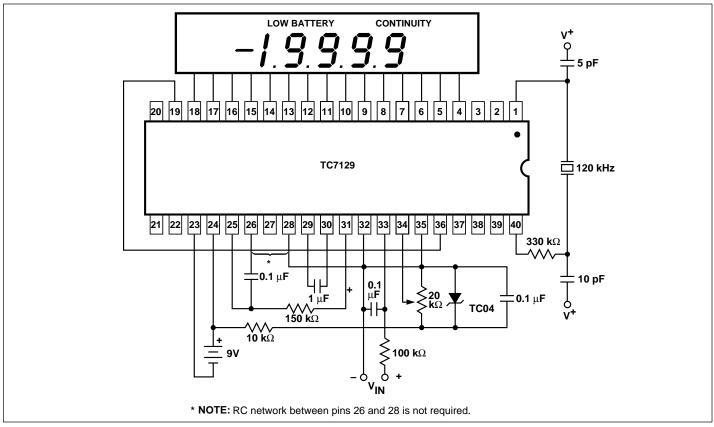

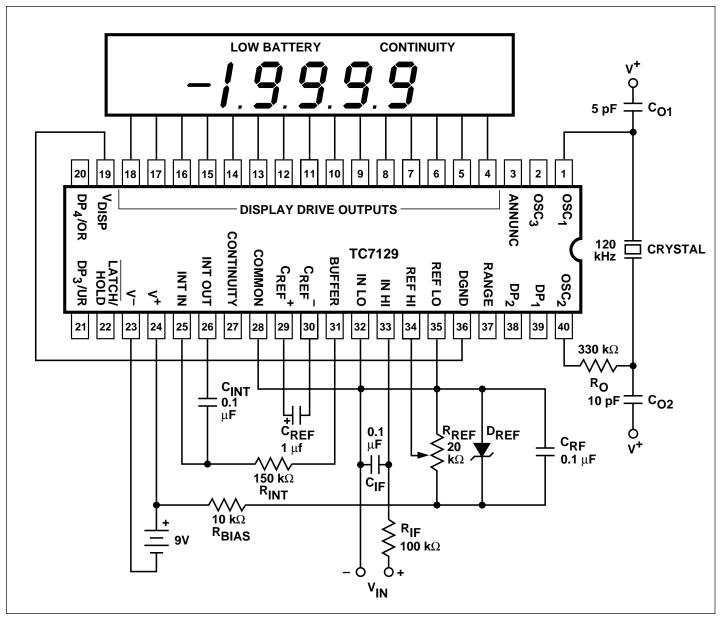

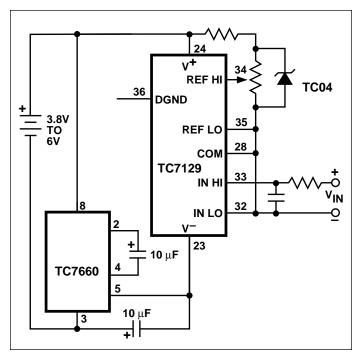

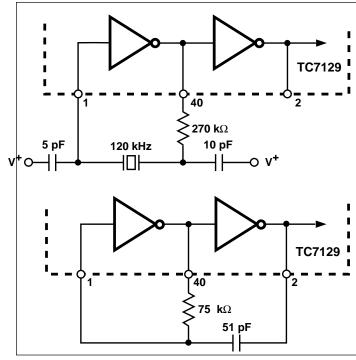

The basic circuit for a digital multimeter application is shown in Figure 1. See "Special Applications" for variations. Typical values for each component are shown. The sections below give component selection criteria.

The primary criterion for selecting the crystal oscillator is to chose a frequency that achieves maximum rejection of line-frequency noise. To do this, the integration phase should last an integral number of line cycles. The integration phase of the TC7129 is 10,000 clock cycles on the 200mV range and 1000 clock cycles on the 2V range. One clock cycle is equal to two oscillator cycles. For 60Hz rejection, the oscillator frequency should be chosen so that the period of one line cycle equals the integration time for the 2V range:

giving an oscillator frequency of 120kHz. A similar calculation gives an optimum frequency of 100kHz for 50Hz rejection.

The resistor and capacitor values are not critical; those shown work for most applications. In some situations, the capacitor values may have to be adjusted to compensate for parasitic capacitance in the circuit. The capacitors can be low-cost ceramic devices.

Some applications can use a simple RC network instead of a crystal oscillator. The RC oscillator has more potential for jitter, especially in the least significant digit. See "RC Oscillator."

### Integrating Resistor (R<sub>INT</sub>)

The integrating resistor sets the charging current for the integrating capacitor. Choose a value that provides a current between  $5\mu A$  and  $20\mu A$  at 2V, the maximum full-scale input. The typical value chosen gives a charging current of  $13.3\mu A$ :

$$I_{CHARGE} = \frac{2V}{150k\Omega} 13.3\mu A$$

Too high a value for  $R_{\rm INT}$  increases the sensitivity to noise pickup and increases errors due to leakage current. Too low a value degrades the linearity of the integration, leading to inaccurate readings.

Figure 1. Standard Circuit

TC7129

# Integrating Capacitor (C<sub>INT</sub>)

The charge stored in the integrating capacitor during the integrate phase is directly proportional to the input voltage. The primary selection criterion for  $C_{\mathsf{INT}}$  is to choose a value that gives the highest voltage swing while remaining within the high-linearity portion of the integrator output range. An integrator swing of 2V is the recommended value. The capacitor value can be calculated from the equation:

$$C_{INT} = \frac{t_{INT} \times I_{INT}}{V_{SWING}},$$

where t<sub>INT</sub> is the integration time.

Using the values derived above (assuming 60Hz operation), the equation becomes:

$$C_{INT} = \frac{16.7 msec \times 13.3 \mu A}{2V} = 0.1 \mu F.$$

The capacitor should have low dielectric absorption to ensure good integration linearity. Polypropylene and Teflon capacitors are usually suitable. A good measurement of the dielectric absorption is to connect the reference capacitor across the inputs by connecting:

#### Pin to Pin

$$20 \rightarrow 33$$

(C<sub>REF</sub><sup>+</sup> to IN HI)

$30 \rightarrow 32$  (C<sub>REF</sub><sup>-</sup> to IN LO)

A reading between 10,000 and 9998 is acceptable; anything lower indicates unacceptably high dielectric absorption.

# **Reference Capacitor** (C<sub>REF</sub>)

The reference capacitor stores the reference voltage during several phases of the measurement cycle. Low leakage is the primary selection criterion for this component. The value must be high enough to offset the effect of stray capacitance at the capacitor terminals. A value of at least  $1\mu F$  is recommended.

# Voltage Reference (D<sub>REF</sub>, R<sub>REF</sub>, R<sub>BIAS</sub>, C<sub>RF</sub>)

A TC04 band-gap reference provides a high-stability voltage reference of 1.25V. The reference potentiometer (R<sub>REF</sub>) provides an adjustment for adjusting the reference voltage; any value above 20 k $\Omega$  is adequate. The bias resistor (R<sub>BIAS</sub>) limits the current through D<sub>REF</sub> to less than 150  $\mu$ A. The reference filter capacitor (C<sub>RF</sub>) forms an RC filter with R<sub>BIAS</sub> to help eliminate noise.

## Input filter (RIF, CIF)

For added stability, an RC input noise filter is usually included in the circuit. The input filter resistor value should not exceed  $100k\Omega$ . A typical RC time constant value is 16.7msec to help reject line-frequency noise. The input filter capacitor should have low leakage for a high-impedance input.

#### **Battery**

The typical circuit uses a 9V battery as a power source. Any value between 6V and 12V can be used. For operation from batteries with voltages lower than 6V and for operation from power supplies, see "Powering the TC7129."

#### **SPECIAL APPLICATIONS**

### The TC7129 as a Replacement Part

The TC7129 is a direct pin-for-pin replacement part for the ICL7129. Note, however, that part requires a capacitor and resistor between pins 26 and 28 for phase compensation. Since the TC7129 uses internal phase compensation, these parts are not required and, in fact, **must be removed** from the circuit for stable operation.

#### Powering the TC7129

While the most common power source for the TC7129 is a 9V battery, there are other possibilities. Some of the more common ones are explained below.

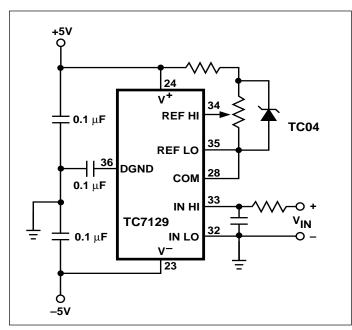

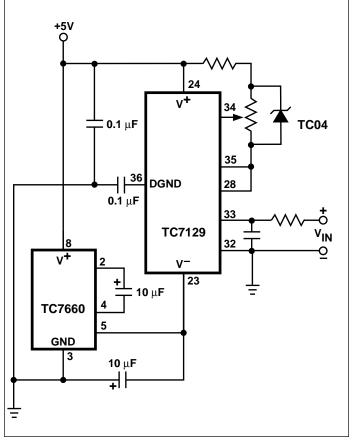

#### ±5V Power Supply

Measurements are made with respect to power supply ground. DGND (pin 36) is set internally to about 5V less than  $V^+$  (pin 24); it is not intended as a power supply input and must not be tied directly to power supply ground. (It can be used as a reference for external logic, as explained in "Connecting to External Logic." (See Figure 2.)

### Low-Voltage Battery Source

A battery with voltage between 3.8V and 6V can be used to power the TC7129 when used with a voltage-doubler circuit as shown in Figure 3. The voltage doubler uses the TC7660 DC-to-DC voltage converter and two external capacitors.

# +5V Power Supply

Measurements are made with respect to power supply ground. COMMON (pin 28) is connected to REF LO (pin 35). A voltage doubler is needed, since the supply voltage is less

than the 6V minimum needed by the TC7129. DGND (pin 36) must be isolated from power supply ground. (See Figure 4.)

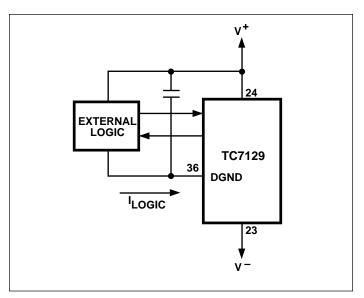

# **Connecting to External Logic**

External logic can be directly referenced to DGND (pin 36), provided that the supply current of the external logic does not exceed the sink current of DGND (Figure 5). A safe value for DGND sink current is 1.2 mA. If the sink current is expected to exceed this value, a buffer is recommended. (See Figure 6.)

Figure 2. Powering the TC7129 From a  $\pm$ 5V Power Supply

# **Temperature Compensation**

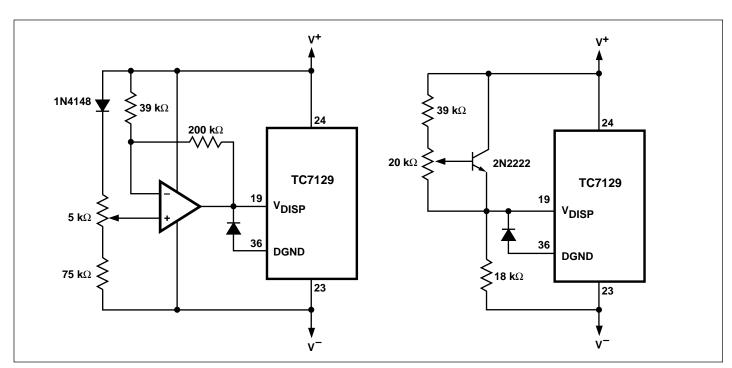

For most applications,  $V_{DISP}$  (pin 19) can be connected directly to DGND (pin 36). For applications with a wide temperature range, some LCDs require that the drive levels vary with temperature to maintain good viewing angle and display contrast. Figure 7 shows two circuits that can be adjusted to give temperature compensation of about 10 mV/°C between V+ (pin 24) and  $V_{DISP}$ . The diode between DGND and  $V_{DISP}$  should have a low turn-ON voltage because  $V_{DISP}$  cannot exceed 0.3V below DGND.

Figure 3. Powering the TC7129 From a Low-Voltage Battery

Figure 4. Powering the TC7129 From a +5V Power Supply

# **TC7129**

EXTERNAL LOGIC TC7129

JLOGIC DGND

JLOGIC TC7129

Figure 5. External Logic Referenced Directly to DGND

Figure 6. External Logic Referenced to DGND With Buffer

Figure 7. Temperature Compensating Circuits

9

#### **RC Oscillator**

For applications in which 3-1/2 digit (100  $\mu$ V) resolution is sufficient, an RC oscillator is adequate. A recommended value for the capacitor is 51pF. Other values can be used as long as they are sufficiently larger than the circuit parasitic capacitance. The resistor value is calculated from:

$$R = \frac{0.45}{\text{freg} * C}$$

For 120 kHz frequency and C = 51pF, the calculated value of R is  $75k\Omega$ . The RC oscillator and the crystal oscillator circuits are shown in Figure 8.

### **Measuring Techniques**

Two important techniques are used in the TC7129: successive integration and digital auto-zeroing. Successive integration is a refinement to the traditional dual-slope conversion technique.

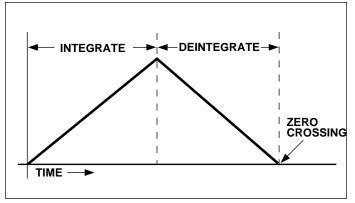

# **Dual-Slope Conversion**

A dual-slope conversion has two basic phases: integrate and deintegrate. During the integrate phase, the input signal is integrated for a fixed period of time; the integrated voltage level is thus proportional to the input voltage. During the deintegrate phase, the integrated voltage is ramped down at a fixed slope, and a counter counts the clock cycles until the integrator voltage crosses zero. The count is a

Figure 8. Oscillator Circuits

measurement of the time to ramp the integrated voltage to zero, and is therefore proportional to the input voltage being measured. This count can then be scaled and displayed as a measurement of the input voltage. Figure 9 shows the phases of the dual-slope conversion.

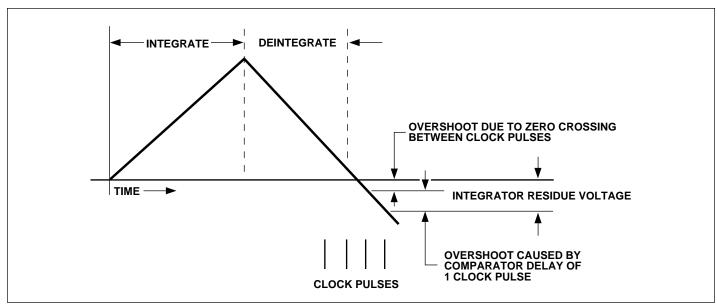

The dual-slope method has a fundamental limitation. The count can only stop on a clock cycle, so that measurement accuracy is limited to the clock frequency. In addition, a delay in the zero-crossing comparator can add to the inaccuracy. Figure 10 shows these errors in an actual measurement.

Figure 9. Dual-Slope Conversion

# **Successive Integration**

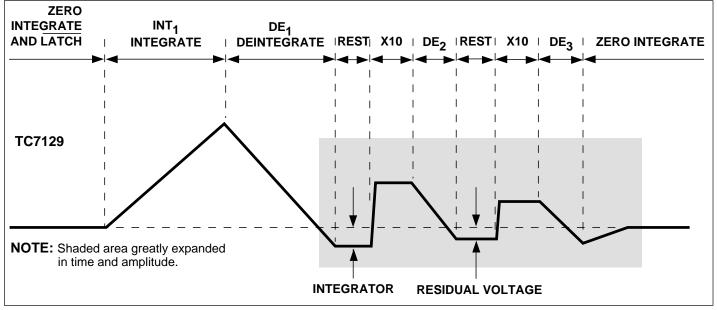

The successive integration technique picks up where dual-slope conversion ends. The overshoot voltage shown in Figure 10, called the "integrator residue voltage," is measured to obtain a correction to the initial count. Figure 11 shows the cycles in a successive integration measurement.

The waveform shown is for a negative input signal. The sequence of events during the measurement cycle is:

| Phase            | Description                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT <sub>1</sub> | Input signal is integrated for fixed time. (1000 clock cycles on 2V scale, 10,000 on 200 mV)                                                                                          |

| DE <sub>1</sub>  | Integrator voltage is ramped to zero. Counter counts up until zero crossing to produce reading accurate to 3-1/2 digits. Residue represents an overshoot of the actual input voltage. |

| REST             | Rest; circuit settles.                                                                                                                                                                |

| X10              | Residue voltage is amplified 10 times and inverted.                                                                                                                                   |

| DE <sub>2</sub>  | Integrator voltage is ramped to zero. Counter counts down until zero crossing to correct reading to 4-1/2 digits. Residue represents an undershoot of the actual input voltage.       |

| REST             | Rest; circuit settles.                                                                                                                                                                |

| X10              | Residue voltage is amplified 10 times and inverted.                                                                                                                                   |

| DE <sub>3</sub>  | Integrator voltage is ramped to zero. Counter counts up until zero crossing to correct reading to 5-1/2 digits. Residue is discarded.                                                 |

Figure 10. Accuracy Errors in Dual-Slope Conversion

Figure 11. Integrator Waveform

# **Digital Auto-Zeroing**

To eliminate the effect of amplifier offset errors, the TC7129 uses a digital auto-zeroing technique. After the input voltage is measured as described above, the measurement is repeated with the inputs shorted internally. The reading with inputs shorted is a measurement of the internal errors and is subtracted from the previous reading to obtain a corrected measurement. Digital auto-zeroing eliminates the need for an external auto-zeroing capacitor used in other ADCs.

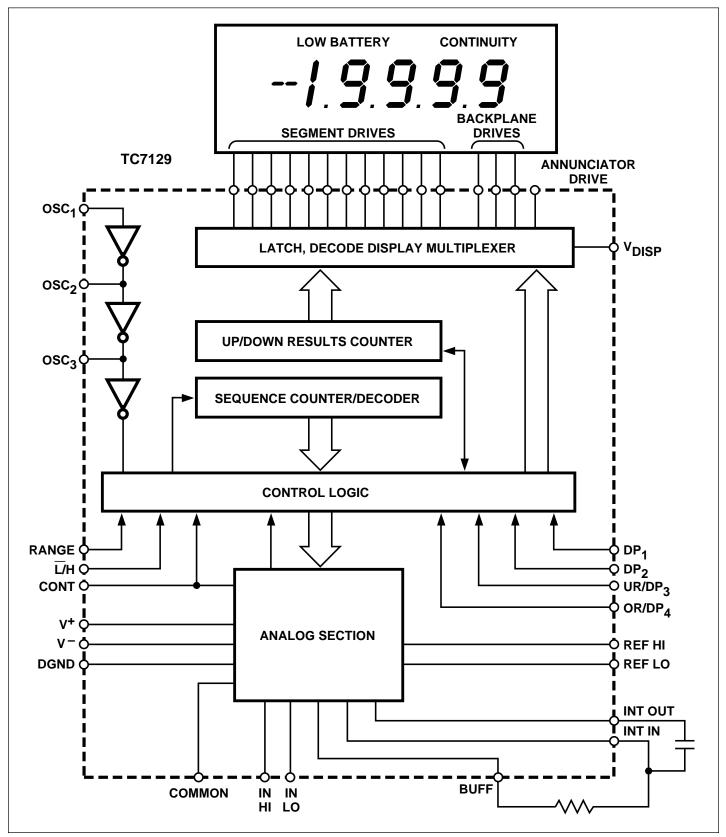

### Inside the TC7129

Figure 12 shows a simplified block diagram of the TC7129.

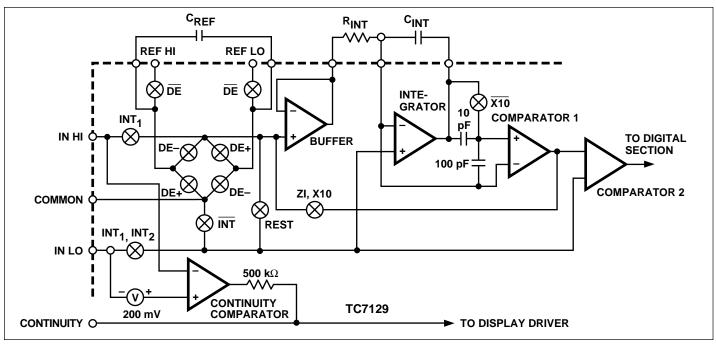

# **Integrator Section**

The integrator section includes the integrator, comparator, input buffer amplifier, and analog switches used to change the circuit configuration during the separate measurement phases described earlier.

Figure 12. Functional Block Diagram

Figure 13. Integrator Block Diagram

Table 1. Switch Legends

| Label            | Meaning                                                                         |

|------------------|---------------------------------------------------------------------------------|

| DE               | Open during all deintegrate phases.                                             |

| DE-              | Closed during all deintegrate phases when input voltage is negative.            |

| DE+              | Closed during all deintegrate phases when input voltage is positive.            |

| INT <sub>1</sub> | Closed during the first integrate phase (measurement of the input voltage).     |

| INT <sub>2</sub> | Closed during the second integrate phase (measurement of the amplifier offset). |

| ĪNT              | Open during both integrate phases.                                              |

| REST             | Closed during the rest phase.                                                   |

| ZI               | Closed during the zero-integrate phase.                                         |

| X10              | Closed during the X10 phase.                                                    |

| X10              | Open during the X10 phase.                                                      |

|                  |                                                                                 |

The buffer amplifier has a common-mode input voltage range from 1.5V above V $^-$  to 1V below V $^+$ . The integrator amplifier can swing to within 0.3V of the rails, although for best linearity the swing is usually limited to within 1V. Both amplifiers can supply up to  $80\mu A$  of output current, but should be limited to  $20\mu A$  for good linearity.

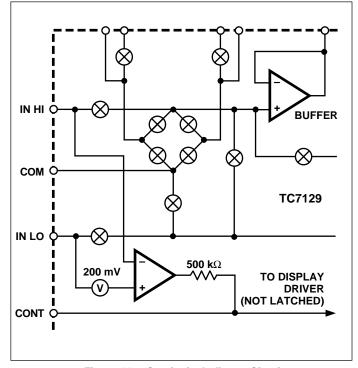

# **Continuity Indicator**

A comparator with a 200mV threshold is connected between IN HI (pin 33) and IN LO (pin 32). Whenever the voltage between inputs is less than 200mV, the

Figure 14. Continuity Indicator Circuit

CONTINUITY output (pin 27) will be pulled HIGH, activating the continuity annunciator on the display. The continuity pin can also be used as an input to drive the continuity annunciator directly from an external source. A schematic of the input/output nature of this pin is shown in Figure 15.

Figure 15. Input/Output Pin Schematic

### Common and Digital Ground

The common and digital ground (DGND) outputs are generated from internal zener diodes. The voltage between  $V^+$  and DGND is the internal supply voltage for the digital section of the TC7129. Common can source approximately 12 $\mu$ A; DGND has essentially no source capability.

#### Low Battery

The low battery annunciator turns on when supply voltage between  $V^+$  and  $V^-$  drops below 6.8V. The internal zener has a threshold of 6.3V. When the supply voltage drops below 6.8V, the transistor tied to  $V^-$  turns OFF, pulling the "Low Battery" point HIGH. (See Figure 16.)

#### **Sequence and Results Counter**

A sequence counter and associated control logic provide signals that operate the analog switches in the integrator section. The comparator output from the integrator gates

Figure 16. Digital Ground (DGND) and Common Outputs

the results counter. The results counter is a six-section up/down decade counter which holds the intermediate results from each successive integration.

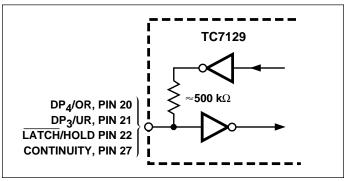

#### **Overrange and Underrange Outputs**

When the results counter holds a value greater than  $\pm 19,999$ , the DP<sub>4</sub>/OR output (pin 20) is driven HIGH. When the results counter value is less than  $\pm 1000$ , the DP<sub>3</sub>/UR output (pin 21) is driven HIGH. Both signals are valid on the falling edge of  $\overline{LATCH}/HOLD$  ( $\overline{L}/H$ ) and do not change until the end of the next conversion cycle. The signals are updated at the end of each conversion unless the  $\overline{L}/H$  input (pin 22) is held HIGH. Pins 20 and 21 can also be used as inputs for external control of decimal points 3 and 4. Figure 15 shows a schematic of the input/output nature of these pins.

### Latch/Hold

The L/H output goes LOW during the last 100 cycles of each conversion. This pulse latches the conversion data into the display driver section of the TC7129. This pin can also be used as an input. When driven HIGH, the display will not be updated; the previous reading is displayed. When driven LOW, the display reading is not latched; the sequence counter reading will be displayed. Since the counter is counting much faster than the backplanes are being updated, the reading shown in this mode is somewhat erratic.

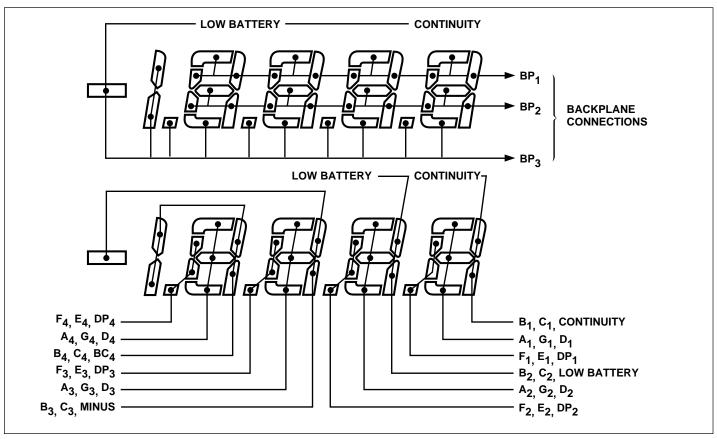

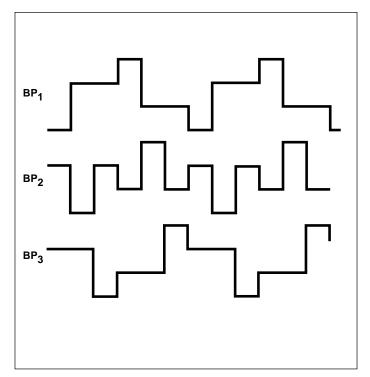

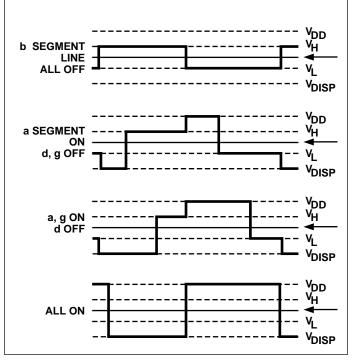

## **Display Driver**

The TC7129 drives a triplexed LCD with three backplanes. The LCD can include decimal points, polarity sign, and annunciators for continuity and low battery. Figure 17 shows the assignment of the display segments to the backplanes and segment drive lines. The backplane drive frequency is obtained by dividing the oscillator frequency by 1200. This results in a backplane drive frequency of 100Hz for 60Hz operation (120 kHz crystal) and 83.3Hz for 50Hz operation (100kHz crystal).

Backplane waveforms are shown in Figure 18. These appear on outputs BP<sub>1</sub>, BP<sub>2</sub>, BP<sub>3</sub> (pins 16, 17, and 18). They remain the same regardless of the segments being driven.

Other display output lines (pins 4 through 15) have waveforms that vary depending on the displayed values. Figure 19 shows a set of waveforms for the A, G, D outputs (pins 5, 8, 11, and 14) for several combinations of "ON" segments.

The ANNUNCIATOR DRIVE output (pin 3) is a square-wave running at the backplane frequency (100 Hz or 83.3Hz), with a peak-to-peak voltage equal to DGND voltage. Connecting an annunciator to pin 3 turns it ON; connecting it to its backplane turns it OFF.

# **TC7129**

Figure 17. Display Segment Assignments

Figure 18. Backplane Waveforms

Figure 19. Typical Display Output Waveforms

# **TC7129**

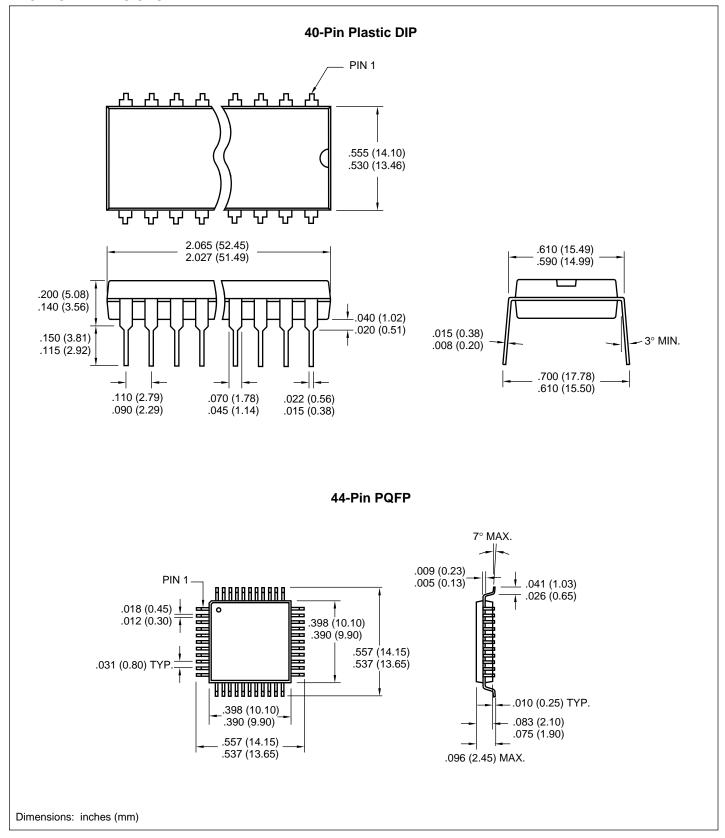

#### **PACKAGE DIMENSIONS**

# **TC7129**

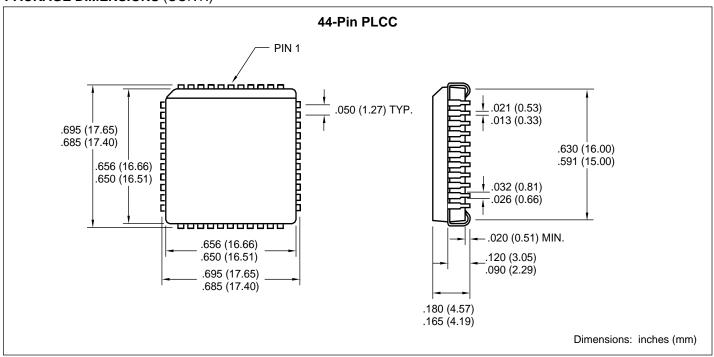

### **PACKAGE DIMENSIONS (CONT.)**

# WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

#### **Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Austin

Analog Product Sales 8303 MoPac Expressway North Suite A-201 Austin, TX 78759 Tel: 512-345-2030 Fax: 512-345-6085

#### **Boston**

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### **Boston**

Analog Product Sales Unit A-8-1 Millbrook Tarry Condominium 97 Lowell Road Concord, MA 01742 Tel: 978-371-6400 Fax: 978-371-0050

#### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

#### **Dallas**

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

#### Dayton

Two Prestige Place, Suite 130 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

#### **Detroit**

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

#### Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

# **Mountain View**

Analog Product Sales 1300 Terra Bella Avenue Mountain View, CA 94043-1836 Tel: 650-968-9241 Fax: 650-967-1590

#### **New York**

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

#### China - Beijing

Microchip Technology Beijing Office Unit 915

New China Hong Kong Manhattan Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Shanghai

Microchip Technology Shanghai Office Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### **Hong Kong**

Microchip Asia Pacific RM 2101, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc. India Liaison Office

Divyasree Chambers

1 Floor, Wing A (A3/A4)

No. 11, OiShaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

#### Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934

#### ASIA/PACIFIC (continued)

#### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850

#### Taiwan

Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### **EUROPE**

#### Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

#### Denmark

Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

Arizona Microchip Technology SARL Parc díActivite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

#### Germany

Analog Product Sales D-82152 Martinsried, Germany Tel: 49-89-895650-0 Fax: 49-89-895650-22 Italy

Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

**United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

All rights reserved. © 2001 Microchip Technology Incorporated. Printed in the USA. 1/01 Printed on recycled paper.

01/09/01

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchipis products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, except as maybe explicitly expressed herein, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.