#### **STHV748**

# 5-level, ±90 V, 2 A high-speed pulser with four independent channels

Preliminary data

#### **Features**

- High-density ultrasound transmitter

- 0 to ±90 V output voltage

- Up to 20 MHz operating frequency

- Low-power, high-voltage drivers

- 2 independently supplied half bridges for each channel in pulse wave (PW) mode

- 5-level output waveform

- ±2 A source and sink current

- Down to 20 ps jitter

- Anti-cross conduction function

- Low 2nd harmonic distortion

- Fine-tuning on propagation delay

- Fully integrated clamping-to-ground function

- 6 Ω synchronous active clamp

- Anti-leakage on output node

- Dedicated half bridge for continuous wave (CW) mode on each

- Down to 0.1 W power consumption

- ±0.6 A source and sink current

- Down to 10 ps jitter

- Fully integrated HV receiver switch

- 13.5  $\Omega$  on resistance

- HV MOS topology to minimize current consumption

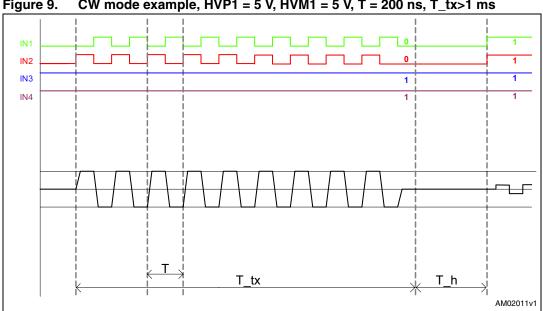

- Up to 300 MHz BW

- 2.4 V to 3.6 V CMOS logic interface

- Auxiliary integrated circuits

- Noise blocking diodes

- Fully self-biaising architecture

- Anti-memory effect for all internal HV nodes

- Thermal protection

- Stand by function

- Latch-up free due to HV SOI technology

- Very few external passive components needed

#### **Applications**

- Medical ultrasound imaging

- Pulse waveform generator

- NDT ultrasound transmission

- Piezoelectric transducers driver

#### **Description**

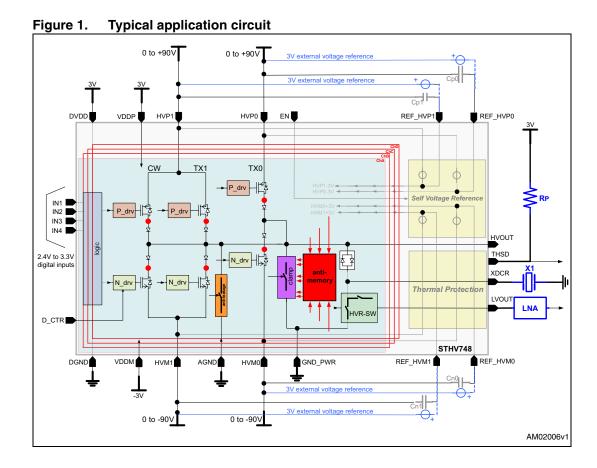

This monolithic, high-voltage, high-speed pulser generator features four independent channels. It is designed for medical ultrasound applications, but can also be used for other piezoelectric, capacitive or MEMS transducers. The device comprises a controller logic interface circuit, level translators, MOSFET gate drivers, noise blocking diodes and high-power P-channel and N-channel MOSFETs as output stage for each channel, clamping-to-ground circuitry, anti-leakage, antimemory effect block, thermal sensor and HV receiver switch (HVR\_SW) which guarantees a strong decoupling during transmission phase. Moreover the STHV748 includes self biasing and thermal shutdown blocks (see *Figure 1*).

Each channel can support up to five active output levels with two half bridges. The output stage of each channel is able to provide ±2 A peak output current. In order to reduce power dissipation during continuous wave mode, the peak current is limited to 0.6 A (a dedicated half bridge is used).

Table 1. Device summary

| Order code | Package | Packaging     |

|------------|---------|---------------|

| STHV748QTR | QFN64   | Tape and reel |

January 2010 Doc ID 15450 Rev 1 1/22

Contents STHV748

### **Contents**

| 1  | Typic | eal application circuit                     | 3 |

|----|-------|---------------------------------------------|---|

| 2  | Pin s | ettings                                     | 4 |

|    | 2.1   | Connection                                  | 4 |

|    | 2.2   | Description                                 | 4 |

|    | 2.3   | Additional pin description                  | 6 |

| 3  | Truth | table and single channel block description  | 7 |

| 4  | Туріс | cal supply reference setting                | 8 |

| 5  | Elect | rical data                                  | 9 |

|    | 5.1   | Absolute maximum ratings                    | 9 |

| 6  | Oper  | ating supply voltages and average currents1 | 0 |

|    | 6.1   | Digital inputs                              | 1 |

|    | 6.2   | Output signals 1                            | 1 |

| 7  | Elect | rical characteristics1                      | 2 |

| 8  | Timir | ngs                                         | 5 |

| 9  | Pack  | age mechanical data                         | 8 |

| 10 | Ravis | sion history                                | 1 |

### 1 Typical application circuit

Pin settings STHV748

### 2 Pin settings

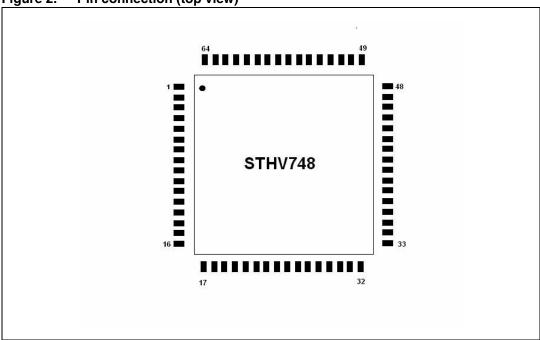

#### 2.1 Connection

Figure 2. Pin connection (top view)

Note: 0.25 mm X 100 V maximum voltage between abutted pins

### 2.2 Description

Table 2. Pin description (P = power, A = analog, D = digital)

| Pin N | Name     | Function                                                    | IN/OUT | Туре |

|-------|----------|-------------------------------------------------------------|--------|------|

| 1     | AGND     | Signal ground                                               | I      | Α    |

| 2     | REF_HVM1 | Supply for low side 1 gate driver                           | I      | Р    |

| 3     | HVM1_A   | Negative high-voltage supply 1 channel A                    | I      | Р    |

| 4     | HVM0_A   | Negative high-voltage supply 0 channel A                    | I      | Р    |

| 5     | HVOUT_A  | Channel A, high-voltage output before noise blocking diodes | 0      | Р    |

| 6     | HVP0_A   | Positive high-voltage supply 0 channel A                    | I      | Р    |

| 7     | REF_HVP1 | Supply for high side 1 gate driver                          | I      | Р    |

| 8     | HVP1_A   | Positive high-voltage supply 1 channel A                    | I      | Р    |

| 9     | HVP1_B   | Positive high-voltage supply 1 channel B                    | I      | Р    |

| 10    | REF_HVP0 | Supply for high side 0 gate driver                          | ı      | Р    |

| 11    | HVP0_B   | Positive high-voltage supply 0 channel B                    | ı      | Р    |

STHV748 Pin settings

Table 2. Pin description (P = power, A = analog, D = digital) (continued)

| Pin N | Name     | Function                                                    | IN/OUT | Туре |

|-------|----------|-------------------------------------------------------------|--------|------|

| 12    | HVOUT_B  | Channel B, high-voltage output before noise blocking diodes | 0      | Р    |

| 13    | HVM0_B   | Negative high-voltage supply 0 channel B                    | I      | Р    |

| 14    | HVM1_B   | Negative high-voltage supply 1 channel B                    | I      | Р    |

| 15    | REF_HVM0 | Supply for low side 0 gate driver                           | I      | Р    |

| 16    | D_CTR    | Delay control                                               | I      | Α    |

| 17    | IN4      | Input signal shared                                         | I      | D    |

| 18    | IN1_B    | Input signal channel B                                      | I      | D    |

| 19    | IN2_B    | Input signal channel B                                      | I      | D    |

| 20    | IN3_B    | Input signal channel B                                      | I      | D    |

| 21    | VDDP     | Positive low-voltage supply                                 | I      | Α    |

| 22    | GND_PWR  | Power ground                                                | I      | Р    |

| 23    | XDCR_B   | Channel B, high-voltage output                              | 0      | Р    |

| 24    | LVOUT_B  | Channel B, low-voltage output                               | 0      | Α    |

| 25    | LVOUT_C  | Channel C, low-voltage output                               | 0      | Α    |

| 26    | XDCR_C   | Channel C, high-voltage output                              | 0      | Р    |

| 27    | GND_PWR  | Power ground                                                | I      | Р    |

| 28    | VDDM     | Negative low-voltage supply                                 | I      | Α    |

| 29    | IN3_C    | Input signal channel C                                      | I      | D    |

| 30    | IN2_C    | Input signal channel C                                      | I      | D    |

| 31    | IN1_C    | Input signal channel C                                      | Ĺ      | D    |

| 32    | THSD     | Thermal shutdown pin                                        | I/O    | D    |

| 33    | AGND     | Signal ground                                               | I      | Α    |

| 34    | REF_HVM1 | Supply for low side 1 gate driver                           | I      | Р    |

| 35    | HVM1_C   | Negative high-voltage supply 1 channel C                    | I      | Р    |

| 36    | HVM0_C   | Negative high-voltage supply 0 channel C                    | I      | Р    |

| 37    | HVOUT_C  | Channel C, high-voltage output before noise blocking diodes | 0      | Р    |

| 38    | HVP0_C   | Positive high-voltage supply 0 channel C                    | I      | Р    |

| 39    | REF_HVP1 | Supply for high side 1 gate driver                          | I      | Р    |

| 40    | HVP1_C   | Positive high-voltage supply 1 channel C                    | I      | Р    |

| 41    | HVP1_D   | Positive high-voltage supply 1 channel D                    | I      | Р    |

| 42    | REF_HVP0 | Supply for high side 0 gate driver                          | ı      | Р    |

| 43    | HVP0_D   | Positive high-voltage supply 0 channel D                    | I      | Р    |

| 44    | HVOUT_D  | Channel D, high-voltage output before noise blocking diodes | 0      | Р    |

Pin settings STHV748

Pin N IN/OUT Name **Function Type** 45 HVM0 D Negative high-voltage supply 0 channel D Ρ 46 HVM1\_D Negative high-voltage supply 1 channel D ı Ρ REF\_HVM0 Ρ 47 Supply for low side 0 gate driver I 48 **DGND** Logic ground ı Α DVDD ı Α 49 Positive logic supply 50 IN1\_D Input signal channel D ı D 51 IN2\_D Input signal channel D I D IN3\_D Input signal channel D ı 52 D **VDDP** Ī 53 Positive low-voltage supply Α GND\_PWR Power ground ı Р 54 0 Ρ XDCR D 55 Channel D, high-voltage output LVOUT\_D Channel D, low-voltage output 0 56 Α LVOUT A 0 57 Channel A, low-voltage output Α 58 XDCR\_A Channel A, high-voltage output 0 Ρ GND PWR Ρ 59 Power ground 60 **VDDM** Negative low-voltage supply ı Α 61 IN<sub>3</sub> A Input signal channel A ı D 62 IN2\_A Input signal channel A ı D 63 IN1\_A Input signal channel A Ī D 64 ΕN Enable internal supply generators I D Exposed-Pad Substrate ı Р

Table 2. Pin description (P = power, A = analog, D = digital) (continued)

#### 2.3 Additional pin description

EN allows minimizing the power consumption. If EN=0, the self voltage reference is not supplied. Supplying reference externally the total power consumption is reduced.

THSD is a thermal flag. The output stage of THSD pin is a Nch-MOS open-drain, so this necessary to connect external pull-up resistance (Rp $\geq$ 10 k $\Omega$ ) to positive low-voltage supply (see *Figure 1*).If the internal temperature overtakes 160 °C, THSD goes down and put all the channels in HZ state. Externally forcing THSD to positive low-voltage supply, the thermal protection will be disabled.

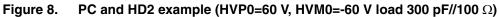

D\_CTR can be used to optimize 2nd HD performances by tuning the fall propagation delay (tdf - see table 9). If D\_CTR is equal to ground tdf has the nominal value. If D\_CTR is being varied from 2 V to 4.2 V tdf can be changed from -1ns to +600 ps respect to the nominal value.

EXPOSED-PAD is internally connected to the substrate. It can be floating or connected to a 100 V capacitance toward ground in order to reduce noise during the receiving phase.

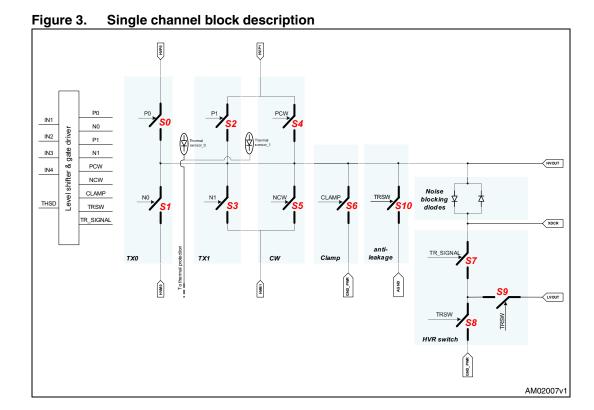

## 3 Truth table and single channel block description

4

Global Per channel Switches internal state State IN4 IN2 **THSD** IN3 IN1 S1 S2 **S7** S9 S0 S3 S4 S5 S6 S8 Clamp Х Х HVM0 HVP0 HVR\_SW Х HVP1 HΖ HVR\_SW Max HVM0 and HVM1 Max HVP0 and HVP1 CW HVM1 CW HVP1 Х Х Х HΖ Х

Table 3. Truth table for one channel

### 4 Typical supply reference setting

Table 4. Typical supply reference setting

| Symbol   | External supply mode             | Self supply mode     |

|----------|----------------------------------|----------------------|

| EN       | 0                                | 1                    |

| Cp0, Cp1 | Not used                         | 47 nF <sup>(1)</sup> |

| Cn0, Cn1 | Not used                         | 9 nF <sup>(1)</sup>  |

| REF_HVP# | Has to be connected to HVP# -3 V | Not used             |

| REF_HVM# | Has to be connected to HVM# +3 V | Not used             |

<sup>1.</sup> In Self supply mode 30  $\mu s$  after EN edge to charge external capacitance are needed.

STHV748 Electrical data

#### 5 Electrical data

### 5.1 Absolute maximum ratings

Table 5. Absolute maximum ratings

| Symbol           | Parameter                                        | Value                      | Unit |

|------------------|--------------------------------------------------|----------------------------|------|

| AGND             | Analog ground reference (1)                      | 0                          | V    |

| DGND             | Digital ground                                   | -300 to 300                | mV   |

| GND_PWR          | Power ground                                     | -1.2 to 1.2                | ٧    |

| VDDP             | Positive supply voltage                          | -0.3 to 3.9                | ٧    |

| VDDM             | Negative supply voltage                          | 0.3 to -3.9                | V    |

| DVDD             | Positive logic voltage                           | -0.3 to 3.9                | ٧    |

| HVP0             | TX0 high-voltage positive supply                 | 0 to 95                    | ٧    |

| HVP1             | TX1 high-voltage positive supply                 | ≤ HVP0                     | ٧    |

| HVM0             | TX0 high-voltage negative supply                 | 0 to -95                   | ٧    |

| HVM1             | TX1 high-voltage negative supply                 | ≥ HVM0                     | V    |

| REF_HVP#         | High-voltage positive gate supply                | -0.3 < HVP - REF_HVP < 3.3 | ٧    |

| REF_HVM#         | High-voltage negative gate supply                | -0.3 < REF_HVM - HVM < 3.3 | V    |

| XDCR             | High-voltage output                              | -95 to 95                  | ٧    |

| HVOUT            | High-voltage output before noise blocking diodes | -95 to 95                  | V    |

| LVOUT            | Low-voltage output                               | -1 to 1                    | V    |

| DIG I/O          | Digital input specified in tab1                  | -0.3 to DVDD + 0.3         | V    |

| D_CTR            | Delay control                                    | -0.3 to 4.6                | V    |

| T <sub>OP</sub>  | Operating temperature range                      | -40 to 125                 | °C   |

| T <sub>STG</sub> | Storage temperature range                        | -65 to 150                 | °C   |

<sup>1.</sup> AGND is considered like "ground reference" for all fallen voltages.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 6.

| Symbol             | Parameter                       | Value             | Unit |

|--------------------|---------------------------------|-------------------|------|

| R <sub>th,JA</sub> | Thermal resistance junction-amb | 30 <sup>(1)</sup> | °C/W |

This value is given for a two layer PCB (252P) and it's strongly sensitive to PCB layout. Increasing the number of PCB layer or adding heat singer vias this number degree (reduce)

# 6 Operating supply voltages and average currents (a)

Table 7. Supply voltages

| Symbol                 | Parameter                                                                                                                                                                                                                                                                                                                                                                                                    | Conditions             | Min  | Тур | Max               | Units |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-------------------|-------|

| VDDP                   | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                      |                        | 2.7  | 3   | 3.6               | V     |

| I <sub>VDDP</sub>      | Desitive events everent                                                                                                                                                                                                                                                                                                                                                                                      | PW mode <sup>(1)</sup> |      |     | 3                 | mA    |

| I <sub>VDDP_Q</sub>    | Positive supply current                                                                                                                                                                                                                                                                                                                                                                                      | Stand-by mode (2)      |      |     | 1                 | μΑ    |

| VDDM                   | Negative supply voltage                                                                                                                                                                                                                                                                                                                                                                                      |                        | -2.7 | -3  | -3.6              | V     |

| I <sub>VDDM</sub>      | No mating according accorded                                                                                                                                                                                                                                                                                                                                                                                 | PW mode                |      |     | 2                 | mA    |

| I <sub>VDDM_Q</sub>    | negative supply current                                                                                                                                                                                                                                                                                                                                                                                      | Stand-by mode          |      |     | 1                 | μΑ    |

| DVDD                   | Positive logic voltage                                                                                                                                                                                                                                                                                                                                                                                       |                        | 2.4  | 3   | min(3.6,VDDP+0.3) | V     |

| I_ <sub>DVD</sub>      | Louis accomply accompany                                                                                                                                                                                                                                                                                                                                                                                     | PW mode                |      |     | 10                | μΑ    |

| I_ <sub>DVD_Q</sub>    | Logic supply current                                                                                                                                                                                                                                                                                                                                                                                         | Stand-by mode          | 55   | 65  | 80                | μΑ    |

| HVP                    | High-voltage positive supply                                                                                                                                                                                                                                                                                                                                                                                 |                        | 0    |     | 90                | V     |

| I <sub>HVP</sub>       | 111/                                                                                                                                                                                                                                                                                                                                                                                                         | PW mode                |      |     | 50                | mA    |

| I <sub>HVP_Q</sub>     | HV positive supply current                                                                                                                                                                                                                                                                                                                                                                                   | Stand-by mode          |      |     | 1                 | μΑ    |

| HVM                    | High-voltage negative supply                                                                                                                                                                                                                                                                                                                                                                                 |                        | -90  |     | 0                 | V     |

| I <sub>HVM</sub>       | IN/ no anative accomply accompant                                                                                                                                                                                                                                                                                                                                                                            | PW mode                |      |     | 45                | mA    |

| I <sub>HVM_Q</sub>     | HV negative supply current                                                                                                                                                                                                                                                                                                                                                                                   | Stand-by mode          |      |     | 1                 | μΑ    |

| HVP-REF_HVP            | High-voltage positive gate supply                                                                                                                                                                                                                                                                                                                                                                            |                        | 2.7  | 3   | 3.3               | V     |

| I <sub>REF_HVP</sub>   | LIV a coltina DEE commant                                                                                                                                                                                                                                                                                                                                                                                    | PW mode                |      |     | 7                 | mA    |

| I <sub>REF_HVP_Q</sub> | HV positive HEF current                                                                                                                                                                                                                                                                                                                                                                                      | Stand-by mode          | 200  | 300 | 400               | μΑ    |

| REF_HVM-HVM            | High-voltage negative gate supply                                                                                                                                                                                                                                                                                                                                                                            |                        | 2.7  | 3   | 3.3               | V     |

| I <sub>REF_HVM</sub>   | LIV a costi sa DEE commant                                                                                                                                                                                                                                                                                                                                                                                   | PW mode                |      |     | 3                 | mA    |

| I <sub>REF_HVM_Q</sub> | The negative HEF current                                                                                                                                                                                                                                                                                                                                                                                     | Stand-by mode          | 200  | 300 | 400               | μΑ    |

| AGND                   | Ground reference                                                                                                                                                                                                                                                                                                                                                                                             |                        |      | 0   |                   | V     |

| I <sub>AGND</sub>      | Analas avalvada suvant                                                                                                                                                                                                                                                                                                                                                                                       | PW mode                |      |     | 700               | μΑ    |

| I <sub>AGND_Q</sub>    | Analog ground current                                                                                                                                                                                                                                                                                                                                                                                        | Stand-by mode          |      |     | 1                 | μΑ    |

| GND_PWR                | Power ground reference                                                                                                                                                                                                                                                                                                                                                                                       |                        |      | 0   |                   | V     |

| I <sub>GND_PWR</sub>   | DWD around oursest                                                                                                                                                                                                                                                                                                                                                                                           | PC mode <sup>(3)</sup> |      |     | 20                | mA    |

| I <sub>GND_PWR_Q</sub> | Positive supply current  Negative supply voltage  Negative supply current  Positive logic voltage  Logic supply current  High-voltage positive supply  HV positive supply current  High-voltage negative supply  HV negative supply current  High-voltage positive gate supply  HV positive REF current  High-voltage negative gate supply  HV positive REF current  Ground reference  Analog ground current | Stand-by mode          |      |     | 1                 | μΑ    |

| D_CTR                  | Delay control                                                                                                                                                                                                                                                                                                                                                                                                |                        | 0    |     | 4.2               | V     |

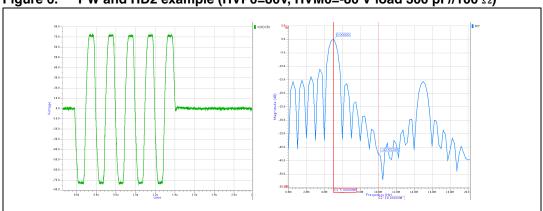

<sup>1.</sup> In PW pulse wave mode the average current is measured over 5 periods (see Figure 5)

577

<sup>2.</sup> In Stand-by mode all channels are in HZ.

<sup>3.</sup> In PC pulse cancellation mode the average current is measured over 1 period (see Figure 6)

a. Operation conditions, unless otherwise specified, only A channel on, no load, HV=90V, TX0 and TX1 on, EN=0.

### 6.1 Digital inputs

Table 8. Digital inputs

| Symbol                             | Parameter                | Min.    | Max.    | Units |

|------------------------------------|--------------------------|---------|---------|-------|

| IN1_#, IN2_#, IN3_#, IN4, EN, THSD | Input logic high-voltage | 0.8DVDD | DVDD    | V     |

| IN1_#, IN2_#, IN3_#, IN4, EN, THSD | Input logic low-voltage  | 0       | 0.2DVDD | V     |

### 6.2 Output signals

Table 9. Output signals

| Symbol | Parameter                                        | Min. | Max. | Units |

|--------|--------------------------------------------------|------|------|-------|

| HVOUT  | High-voltage output before noise blocking diodes | -90  | 90   | V     |

| XDCR   | High-voltage output                              | -90  | 90   | V     |

| LVOUT  | Low-voltage output                               | -1   | 1    | V     |

| THSD   | Thermal shutdown pin                             | 0    | 3    | V     |

Electrical characteristics STHV748

### 7 Electrical characteristics

Table 10. Static electrical characteristics (1)

| Symbol                  | Parameter                           | Condition                                                      | Min     | Тур  | Max     | Units |

|-------------------------|-------------------------------------|----------------------------------------------------------------|---------|------|---------|-------|

| 1                       | Saturation current S1 – S3          | HVP# =10V, HVM# =-10V,<br>HVOUT=0V                             | 1.18    | 1.28 | 1.40    | Α     |

| I <sub>N</sub>          | Saturation current 31 – 33          | HVP# =25V, HVM# =-25V,<br>HVOUT=0V                             |         | 1.70 |         | Α     |

| 1_                      | Saturation current S0 – S2          | HVP# =10V, HVM# =-10V,<br>HVOUT=0V                             | 1.12    | 1.26 | 1.42    | Α     |

| l <sub>P</sub>          | Saturation current 30 – 32          | HVP# =25V, HVM# =-25V,<br>HVOUT=0V                             |         | 1.70 |         | Α     |

| I <sub>NCW</sub>        | Saturation current S5               | HVP1=10V, HVM1=-10V,<br>HVOUT=0V                               | 315     | 350  | 400     | mA    |

| I <sub>PCW</sub>        | Saturation current S4               | HVP1=10V, HVM1=-10V,<br>HVOUT=0V                               | 415     | 480  | 575     | mA    |

|                         | Positive saturation current         | HVOUT=10V                                                      | 1.25    | 1.54 | 2       | Α     |

|                         | S6 (Pch)                            | HVOUT=25V                                                      |         | TBD  |         | Α     |

| I <sub>CL</sub>         | Negative saturation                 | HVOUT=10V                                                      | 1.32    | 1.59 | 2       |       |

|                         | current S6 (Nch)                    | HVOUT=25V                                                      |         | TBD  |         |       |

| IL                      | Output leakage current, per channel | HVP# = 90V, HVM# = -90V,<br>HVOUT=0V                           |         |      | 1       | μΑ    |

| D                       | Power dissipation in stand          | HVP# = 90V, HVM# = -90V,<br>HVOUT=0V, EN=0                     |         | 4    | 4.5     | μW    |

| P <sub>SB</sub>         | by mode                             | HVP# = 90V, HVM# = -90V,<br>HVOUT=0V                           |         | 126  | 150     | mW    |

| P <sub>RX</sub>         | Power dissipation in HVR_SW state   | HVP# = 90V, HVM# = -90V, EN=0, all channels in receiving phase | 25      | 30   | 40      | mW    |

| V <sub>REFP</sub>       | HVP# - REF_HVP#                     | HVP# = 90V, HVM# = -90V,<br>HVOUT=0V                           | 0.8VDDP |      | 1.2VDDP | V     |

| V <sub>REFN</sub>       | REF_HVM# - HVM#                     | HVP# = 90V, HVM# = -90V,<br>HVOUT=0V                           | 0.8VDDP |      | 1.2VDDP | V     |

| T <sub>OTP</sub>        | Over temperature threshold          | HVP# =10V, HVM# =-10V                                          | 130     | 145  | 160     | °C    |

| T <sub>HYS</sub>        | OTP Hysteresis                      | HVP# =10V, HVM# =-10V                                          |         | 40   |         | °C    |

| C <sub>HVR_SW</sub>     | HVR_SW capacitance                  | LVOUT=0V                                                       |         | 40   |         | pF    |

| R <sub>HVR_SW_ON</sub>  | R <sub>HVR_SW</sub> on resistance   | HVP# =10V, HVM# =-10V,<br>XDCR=1V, LVOUT=0V                    | 11.5    | 13.5 | 15.5    | Ω     |

| R <sub>HVR_SW_OFF</sub> | R <sub>HVR_SW</sub> off resistance  | HVP# =10V, HVM# =-10V,<br>XDCR=1V, LVOUT=0V                    | 1       |      |         | GΩ    |

Table 10. Static electrical characteristics (1) (continued)

| Symbol               | Parameter                          | Condition                                                | Min  | Тур  | Max  | Units |

|----------------------|------------------------------------|----------------------------------------------------------|------|------|------|-------|

| V                    | Voltage drop between HVP1 and XDCR | HVP# =10V, HVM# =-10V,<br>I <sub>SINK_XDCR</sub> =50mA   | 2.62 | 2.79 | 2.96 | V     |

| V <sub>DROP_CW</sub> | Voltage drop between XDCR and HVM1 | HVP# =10V, HVM# =-10V,<br>I <sub>SOURCE_XDCR</sub> =50mA | 2.69 | 2.86 | 3.03 | V     |

<sup>1.</sup> Operating conditions, unless otherwise specified, EN = 1, HVP# = 90 V, HVM# = -90 V, VDDP = 3 V, VDDM = - 3 V, DVDD = 3 V, T<sub>ROOM</sub> = 25 °C.

Electrical characteristics STHV748

Table 11. AC electrical characteristics (1)

| Symbol                  | Parameter                           | Test condition                                                        | Min | Тур | Max | Units     |

|-------------------------|-------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|-----------|

| f                       | Maximum autout fraguancy            |                                                                       | 16  |     |     | MHz       |

| f                       | Maximum output frequency            | 50pF//200Ω                                                            |     | 22  |     | MHz       |

| f <sub>CW</sub>         | Maximum output frequency CW         | HVP1 =5V, HVM1 = -5V, continuous wave mode                            | 20  |     |     | MHz       |

| f <sub>BW</sub>         | Output frequency BW                 | HVP1 = 50V, HVM1 = -50V, continuous wave mode, $50pF//200Ω$           |     | 10  |     | MHz       |

| t <sub>j</sub>          | Output jitter                       |                                                                       |     | 20  |     | ps, rms   |

| t <sub>j-CW</sub>       | CW output jitter                    | HVP1 =10V, HVM1 = -10V, continuous wave mode                          |     | 5   |     | ps, rms   |

| t <sub>f</sub>          | Fall time                           |                                                                       |     | 28  | 31  | ns        |

| t <sub>r</sub>          | Rise time                           |                                                                       |     | 28  | 31  | ns        |

| t <sub>dr</sub>         | Rise propagation delay              |                                                                       |     | 24  | 27  | ns        |

| t <sub>df</sub>         | Fall propagation delay              |                                                                       |     | 24  | 27  | ns        |

| t <sub>HVR_SW</sub>     | HVR_SW turn-on / turn-off time      |                                                                       |     | 170 |     | ns        |

|                         |                                     | 1 pulse f = 1.7MHz                                                    |     | -40 |     | dBc       |

| HD2                     | 2 <sup>nd</sup> harmonic distortion | 1 pulse f = 5MHz                                                      | -60 |     | -40 | dBc       |

| TIDZ                    |                                     | 5 pulses f = 1.7MHz                                                   |     | -40 |     | dBc       |

|                         |                                     | 5 pulses f = 5MHz                                                     | -60 |     | -40 | dBc       |

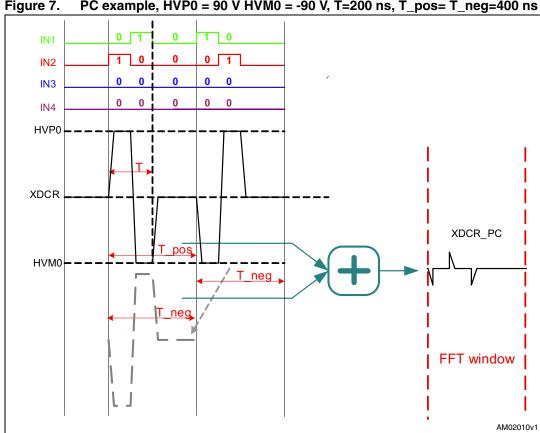

| HD2PC                   | Pulse cancellation                  | f = 1.7MHz original and inverted pulse                                |     | -40 |     | dBc       |

|                         | ruise cancenation                   | f = 5MHz original and inverted pulse                                  | -60 |     | -40 | dBc       |

| BVD                     | Burst voltage drop                  | 1 <sup>st</sup> to 128 <sup>th</sup> pulse HVP1 = 10V,<br>HVM1 = -10V |     | 2   |     | %         |

| P <sub>D_CW</sub>       | Power dissipation, per channel      | CW mode, f = 5MHz, HVP1 = 5V, HVM1 = -5V, no load                     |     |     | 70  | mW        |

| HVR_SW <sub>SPIKE</sub> | HVR_SW spike on XDCR and LVOUT      |                                                                       |     | 100 |     | $mV_{pp}$ |

| X <sub>TALK</sub>       | Cross talk between channels.        | Ampl(2ch)/Ampl(1ch), $50pF//200\Omega$                                |     | -40 |     | db        |

Operating conditions, unless otherwise specified, HVP# = 90V, HVM# = -90V, VDDP = 3V, VDDM = -3V, DVDD = 3V, EN = 0, (HVP-REF\_HVP) = 3V, (REF\_HVM-HVM) = 3V, XDCR load C = 300pF//R = 100Ω, LVOUT load C = 20pF//200Ω T<sub>ROOM</sub> = 25 °C.

STHV748 Timings

### 8 Timings

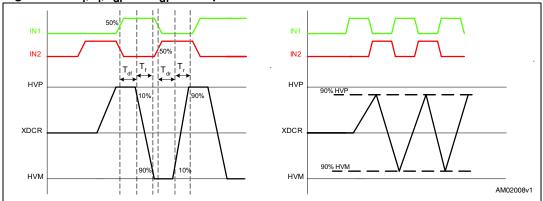

Figure 5. PW example 5 periods, HVP0 = 90 V HVM0 = -90 V, T=200 ns, T\_tx=1.2 μs

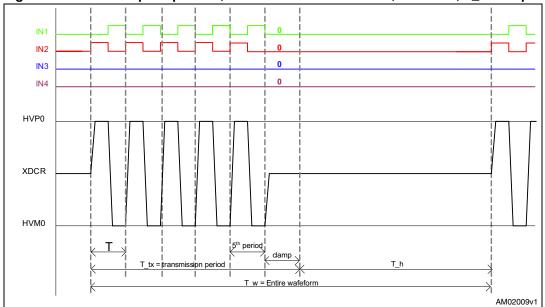

Figure 6. PW and HD2 example (HVP0=80V, HVM0=-80 V load 300 pF//100  $\Omega$ )

**Timings STHV748**

PC example, HVP0 = 90 V HVM0 = -90 V, T=200 ns, T\_pos= T\_neg=400 ns Figure 7.

**STHV748 Timings**

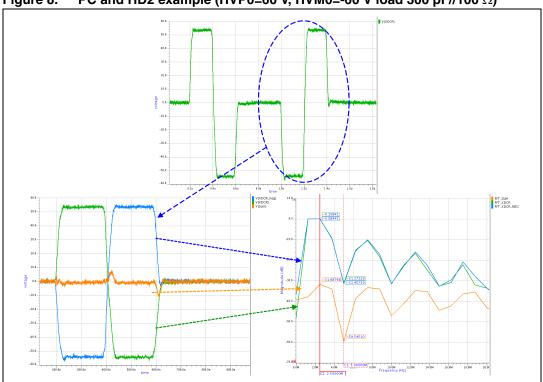

Figure 9. CW mode example, HVP1 = 5 V, HVM1 = 5 V, T = 200 ns, T\_tx>1 ms

Figure 10. HVR\_SW bandwidth

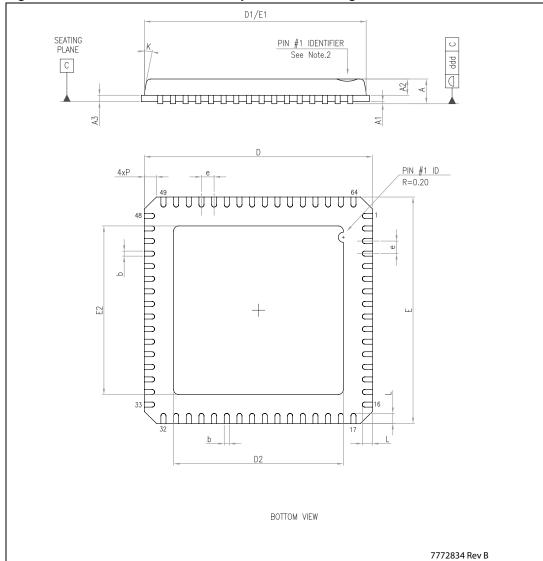

### 9 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

Table 12. QFN64 9 x 9 x 1.0 mm 64 pitch 0.50 mechanical data

| Dim | Min.                      | Тур.                     | Max. |

|-----|---------------------------|--------------------------|------|

| Α   | 0.8                       | 0.9                      | 1    |

| A1  |                           | 0.02                     | 0.05 |

| A2  |                           | 0.65                     | 1    |

| A3  |                           | 0.2                      |      |

| b   | 0.18                      | 0.25                     | 0.3  |

| D   | 8.85                      | 9                        | 9.15 |

| D1  |                           | 8.75                     |      |

| D2  | See exposed pad variation |                          |      |

| E   | 8.85                      | 9                        | 9.15 |

| E1  |                           | 8.75                     |      |

| E2  |                           | See exposed pad variatio | n    |

| е   |                           | 0.5                      |      |

| L   | 0.35                      | 0.4                      | 0.45 |

| Р   |                           |                          | 0.6  |

| K   |                           |                          | 12   |

| ddd |                           |                          | 0.08 |

Table 13. Exposed-pad variation

| Variation |      | D2   |      |      | E2   |      |  |

|-----------|------|------|------|------|------|------|--|

|           | Min. | Тур. | Max. | Min. | Тур. | Max. |  |

| А         | 4.1  | 4.25 | 4.4  | 4.1  | 4.25 | 4.4  |  |

| В         | 4.55 | 4.7  | 4.85 | 4.55 | 4.7  | 4.85 |  |

| С         | 6.95 | 7.1  | 7.25 | 6.95 | 7.1  | 7.25 |  |

| D         | 7.15 | 7.3  | 7.45 | 7.15 | 7.3  | 7.45 |  |

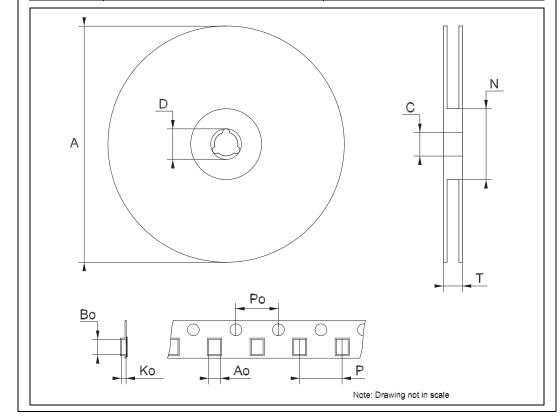

Figure 11. QFN64 9 x 9 x 1.0 mm 64 pitch 0.50 drawing

Figure 12. QFN64 9 x 9 x 1.0 mm 64 tape and reel information

| DIM. |       |     |       | inch  |      |        |

|------|-------|-----|-------|-------|------|--------|

| DIN. | MIN.  | TYP | MAX.  | MIN.  | TYP. | MAX.   |

| Α    |       |     | 330   |       |      | 12.992 |

| С    | 12.8  |     | 13.2  | 0.504 |      | 0.519  |

| D    | 20.2  |     |       | 0.795 |      |        |

| N    | 60    |     |       | 2.362 |      |        |

| Т    |       |     | 30.4  |       |      | 1.196  |

| Ao   | 12.25 |     | 12.45 | 0482  |      | 0.490  |

| Во   | 12.25 |     | 12.45 | 0482  |      | 0.490  |

| Ko   | 2.1   |     | 2.3   | 0.083 |      | 0.091  |

| Po   | 3.9   |     | 4.1   | 0.153 |      | 0.161  |

| Р    | 15.9  |     | 16.1  | 0.626 |      | 0.639  |

STHV748 Revision history

# 10 Revision history

Table 14. Document revision history

| Date        | Revision | Changes         |

|-------------|----------|-----------------|

| 20-Jan-2010 | 1        | Initial release |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

22/22 Doc ID 15450 Rev 1