#### **Features**

- 16-bit SAR ADC without Zero Latency

- Throughput Speed: 600 KSPS

- · Unipolar, Differential Analog Input

- -VREF to VREF

- External VREF

- 2.5 V to VDD

- High Linearity

- INL: ±1 LSB typical

- DNL: ±0.5 LSB typical

- THD: -91 dB at fin=1kHz, VREF=5V

- High Dynamic Range and Noise Performance

- SNR

- Dynamic Range

- Serial Interface:

- SPI Compatible

- Daisy-chain Supported

- Package: MSOP10

- Wide Operating Temperature Range:

- 40°C to +125°C

- Package: MSOP10

### **Applications**

- Data Acquisitions

- Instruments

- · Industry Measurement and Control

- Medical Equipment

- · Automatic Test Equipment

### **Description**

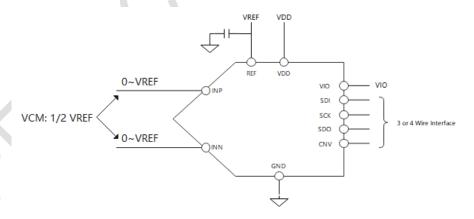

The TPC5160 is a 16-bit analog-to-digital converter (ADC). The device supports unipolar, differential input, and input range, which is -VREF ~VREF with a common-mode voltage of VREF/2.

The device operates with a 2.5 V to VDD external reference.

The device offers an SPI-compatible interface and supports daisy-chain operation for multiple devices application.

The device also offers an optional busy indicator bit, which can be used to synchronize with the host.

### **Typical Application Circuit**

# **Product Family Table**

| Order Number | Resolution | Input range | Throughput speed | Package |

|--------------|------------|-------------|------------------|---------|

| TPC5160-VS2R | 16         | -VREF~VREF  | 600K SPS         | MSOP10  |

### **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             |    |

| Typical Application Circuit             |    |

| Product Family Table                    |    |

| Revision History                        |    |

| Pin Configuration and Functions         |    |

| Pin Functions                           | 5  |

| Specifications                          | 6  |

| Absolute Maximum Ratings                |    |

| ESD, Electrostatic Discharge Protection | 6  |

| Recommended Operating Conditions        | 6  |

| Thermal Information                     | 6  |

| Electrical Characteristics              |    |

| Timing Requirements                     | 9  |

| Detailed Description                    | 11 |

| Overview                                | 11 |

| Functional Block Diagram                | 11 |

| Feature Description                     | 11 |

| Application and Implementation          | 19 |

| Application Information                 | 19 |

| Typical Application                     | 19 |

| Layout                                  | 19 |

| Layout Guideline                        | 19 |

| Layout Example                          | 19 |

| Tape and Reel Information               | 20 |

| Package Outline Dimensions              | 21 |

| MSOP10                                  | 21 |

| Order Information                       | 23 |

# **Revision History**

| Date       | Revision  | Notes               |

|------------|-----------|---------------------|

| 2022-05-23 | Rev.Pre.0 | Pre-Release Version |

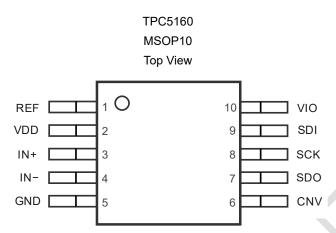

# **Pin Configuration and Functions**

#### **Pin Functions**

| P   | in   | I/O | Description                                                                                                                                                                                                        |

|-----|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name | 1/0 | Description                                                                                                                                                                                                        |

| 1   | REF  | I   | Reference voltage.                                                                                                                                                                                                 |

| 2   | VDD  | 0   | Power supply.                                                                                                                                                                                                      |

| 3   | IN+  | 0   | Positive analog Input.                                                                                                                                                                                             |

| 4   | IN-  | I   | Negative analog Input.                                                                                                                                                                                             |

| 5   | GND  | _   | Power Ground.                                                                                                                                                                                                      |

| 6   | CNV  |     | Conversion input. It initiates the conversions of the device, and selects the interface mode together with SDI.  1. Chain mode: SDI is low during CNV rising edge  2. CS mode: SDI is high during CNV rising edge. |

| 7   | SDO  |     | Serial Data output.                                                                                                                                                                                                |

| 8   | SCK  |     | Serial Data clock.                                                                                                                                                                                                 |

| 9   | SDI  |     | Serial Data input. It selects the serial mode together with CNV.                                                                                                                                                   |

| 10  | VIO  |     | Digital interface power.                                                                                                                                                                                           |

### **Specifications**

#### **Absolute Maximum Ratings**

|                  | Parameter                           | Min  | Max       | Unit |

|------------------|-------------------------------------|------|-----------|------|

| Amalan Valtana   | IN+, IN- to GND                     | -0.3 | VDD + 0.3 | V    |

| Analog Voltage   | VREF to GND                         | -0.3 | VDD + 0.3 | V    |

| Digital Valtage  | Digital Inputs to GND               | -0.3 | VIO + 0.3 | V    |

| Digital Voltage  | Digital Outputs to GND              | -0.3 | VIO + 0.3 | V    |

| Supply Voltage   | VDD to GND                          | -0.3 | 6         | V    |

|                  | VIO to GND                          | -0.3 | VDD+0.3   | V    |

| TJ               | Maximum Junction Temperature        | -40  | 150       | °C   |

| T <sub>A</sub>   | Operating Temperature Range         | -40  | 125       | °C   |

| T <sub>STG</sub> | Storage Temperature Range           | -65  | 150       | °C   |

| TL               | Lead Temperature (Soldering 10 sec) |      | 260       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | 3000          | V    |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 2000          | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **Recommended Operating Conditions**

| Parameter | Min  | Тур | Max | Unit |

|-----------|------|-----|-----|------|

| VDD       | 4.5  | 5   | 5.5 | V    |

| REF       | 2.5  | 5   | VDD | V    |

| VIO       | 1.71 | 3.3 | VDD | V    |

#### **Thermal Information**

| Package Type | θυΑ | <b>Ө</b> лс | Unit |

|--------------|-----|-------------|------|

| MSOP10       |     |             | °C/W |

www.3peakic.com.cn 6 / 23 Rev.Pre.1

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

All test conditions: VDD = 5 V, VIO = 1.71 V to 5 V, TA =  $-40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                  | Test Co         | ndition                                                | Min          | Тур   | Max        | Unit  |  |

|----------------------------|-----------------|--------------------------------------------------------|--------------|-------|------------|-------|--|

| AC Accuracy                |                 |                                                        |              |       |            |       |  |

| ONE                        | 6 4111          | REF=5 V                                                | 87           | 92    |            | dB    |  |

| SNR                        | fin=1 kHz       | REF=3 V                                                | 85.5         | 90    |            | dB    |  |

| CINAD                      | £ 4 1.1 1       | REF=5 V                                                |              | 89    |            | dB    |  |

| SINAD                      | fin=1 kHz       | REF=3 V                                                |              | 89    |            | dB    |  |

| Dumania Danas              | f:4 kH-         | REF=5 V                                                |              | 92    |            | dB    |  |

| Dynamic Range              | fin=1 kHz       | REF=3 V                                                |              | 90    |            | dB    |  |

| THD                        | fin=1 kHz       | REF=5 V                                                |              | -91   |            | dB    |  |

| SFDR                       | fin=1 kHz       | REF=5 V                                                |              | -104  |            | dB    |  |

| IMD                        |                 | fin1=255 kHz,<br>fin2=285 kHz,<br>Ain1&Ain2=-7<br>dBFS |              | NA    |            | dB    |  |

| Resolution                 | NO missing code |                                                        | 16           |       |            | Bits  |  |

| DC Accuracy                |                 |                                                        |              |       |            |       |  |

| DNL                        | REF=5 V         |                                                        | -1           | ±0.5  | 1          | LSB   |  |

| DINL                       | REF=3 V         |                                                        |              | ±0.8  |            | LOD   |  |

| INL                        | REF=5 V         |                                                        | -3           | ±1    | 3          | LSB   |  |

| 1112                       | REF=3 V         |                                                        |              | ±1.5  |            | LOD   |  |

| Transition Noise           | REF=5 V         |                                                        |              | 0.6   |            | LSB   |  |

| Transition (Voice          | REF=3 V         |                                                        |              | 1     |            |       |  |

| Gain Error                 |                 |                                                        |              | ±5    |            | LSB   |  |

| Gain Error Drift           |                 |                                                        |              | ±0.35 |            | ppm/C |  |

| Zero Code Error            |                 |                                                        | -1.3         | ±0.08 | 1.3        | mV    |  |

| Zero Code Error<br>Drift   |                 |                                                        |              | ±0.35 |            | ppm/C |  |

| Power Supply Sensitivity   | AVDD +/-5%      |                                                        |              | ±1.5  |            | LSB   |  |

| Analog Input               |                 |                                                        |              |       |            |       |  |

| Voltage Range              | IN+ - IN-       |                                                        | -VREF        |       | VREF       | V     |  |

| Common-Mode<br>Input Range |                 |                                                        | VREF/2 - 0.1 |       | VREF/2+0.1 |       |  |

| Operating Input            | IN+             |                                                        | -0.1         |       | VREF+0.1   | V     |  |

| Voltage                    | IN-             |                                                        | -0.1         |       | VREF+0.1   | V     |  |

| Analog Input               |                 |                                                        |              | 75    |            | dB    |  |

| CMRR                       |                              |                          |            |                                                |         |     |

|----------------------------|------------------------------|--------------------------|------------|------------------------------------------------|---------|-----|

| Leakage Current<br>at 25°C |                              |                          |            | 1                                              |         | nA  |

| Input<br>Capacitance       |                              |                          |            | 34                                             |         | pF  |

| Throughput                 |                              |                          |            |                                                |         |     |

| Conversion Rate            |                              |                          | 0          |                                                | 0.6     | MHz |

| Acquisition Time           |                              |                          | 850        | 890                                            |         | ns  |

| Conversion Time            |                              |                          |            | 780                                            | 820     | ns  |

| Transient<br>Response      |                              |                          |            | 890                                            |         | ns  |

| Reference                  |                              |                          |            |                                                |         |     |

| REFERENCE<br>Voltage Range |                              |                          | 2.5        |                                                | vcc     | V   |

| REFERENCE<br>Load Current  | 1 MSPS, REF=5 V              |                          |            | 130                                            |         | uA  |

| Sampling Dynami            | cs                           |                          |            |                                                |         |     |

| -3 dB BW                   |                              |                          |            | 20                                             |         | MHz |

| Aperture Delay             |                              |                          |            | 4                                              |         | ns  |

| Digital Input              |                              |                          |            |                                                |         |     |

| VIH                        |                              |                          | 0.7*VDD    |                                                |         | V   |

| VIL                        |                              |                          |            |                                                | 0.3*VDD | V   |

| IIH                        | input current                |                          | -2         |                                                | 2       | uA  |

| IIL                        | input current                |                          | -2         |                                                | 2       | uA  |

| Digital Output             |                              |                          | T          |                                                |         |     |

| Data Format                |                              |                          | S          | erial 16bit straight bina                      | ary     |     |

| Pipeline Delay             |                              |                          |            | esults available immed<br>completed conversion | -       |     |

| VOH                        | Output Logic High<br>Voltage | current<br>source=500 uA | VDRIVE-0.2 |                                                |         | V   |

| VOL                        | Output Logic Low<br>Voltage  | current sink=500<br>uA   |            |                                                | 0.2     | V   |

| Power Supply               |                              |                          |            |                                                |         |     |

| VDD                        |                              |                          | 4.5        |                                                | 5.5     | V   |

| VIO                        |                              |                          | 1.8        |                                                | VDD     | V   |

| Standby Current            |                              |                          |            | 3000                                           |         | uA  |

| VDD Current                | operating                    | fs=1 kHz                 | 2.4        | 3                                              | 3.6     | mA  |

| (lavcc)                    | operating                    | fs=600 kHz               | 3.2        | 4                                              | 4.8     | mA  |

<sup>(1) 100%</sup> tested at  $T_A = 25$ °C.

### **Timing Requirements**

All test conditions: VDD = 5 V, VIO = 1.71 V to 5 V,  $TA = -40^{\circ}C$  to +125°C, unless otherwise noted.

| Parameter                                                                | Symbol   | Min  | Тур | Max | Unit |

|--------------------------------------------------------------------------|----------|------|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data                                 | ,        |      |     | -10 |      |

| Available                                                                | tconv    | 500  |     | 710 | ns   |

| Acquisition Time                                                         | tacq     | 290  |     |     | ns   |

| Time Between Conversions                                                 | tcyc     | 1000 |     |     | ns   |

| CNV Pulse Width (CS Mode)                                                | tсnvн    | 10   |     |     | ns   |

| SCK Period (CS Mode)                                                     | tsck     |      |     |     | ns   |

| VIO Above 4.5 V                                                          |          | 10.5 |     |     | ns   |

| VIO Above 3 V                                                            |          | 12   |     |     | ns   |

| VIO Above 2.7 V                                                          |          | 13   |     |     | ns   |

| VIO Above 2.3 V                                                          |          | 15   |     |     | ns   |

| SCK Period (Chain Mode)                                                  | tscк     |      |     |     | ns   |

| VIO Above 4.5 V                                                          |          | 11.5 |     |     | ns   |

| VIO Above 3 V                                                            |          | 13   |     |     | ns   |

| VIO Above 2.7 V                                                          |          | 14   |     |     | ns   |

| VIO Above 2.3 V                                                          |          | 16   |     |     | ns   |

| SCK Low Time                                                             | tsckl    | 4.5  |     |     | ns   |

| SCK High Time                                                            | tscкн    | 4.5  |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                   | thsdo    | 3    |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                     | tospo    |      |     |     |      |

| VIO Above 4.5 V                                                          |          |      |     | 9.5 | ns   |

| VIO Above 3 V                                                            |          |      |     | 11  | ns   |

| VIO Above 2.7 V                                                          |          |      |     | 12  | ns   |

| VIO Above 2.3 V                                                          |          |      |     | 14  | ns   |

| CNV or SDI Low to SDO D15 MSB Valid (CS Mode)                            | ten      |      |     |     |      |

| VIO Above 3 V                                                            |          |      |     | 10  | ns   |

| VIO Above 2.3 V                                                          |          |      |     | 15  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) | tois     |      |     | 20  | ns   |

| SDI Valid Setup Time from CNV Rising Edge                                | tssdicnv | 5    |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)      | thsdicnv | 2 |    | ns |

|---------------------------------------------------------|----------|---|----|----|

| SDI Valid Hold Time from CNV Rising Edge (Chain Mode)   | thsdicnv | 0 |    | ns |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)  | tssckcnv | 5 |    | ns |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)   | thsckcnv | 5 | 7  | ns |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode) | tssdisck | 2 |    | ns |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)  | thsdisck | 3 |    | ns |

| SDI High to SDO High (Chain Mode with Busy Indicator)   | tdsdosdi |   | 15 | ns |

### **Detailed Description**

#### **Overview**

The TPC5160 is a 16-bit successive approximation register (SAR) ADC. The device is capable to convert analog input into digital output without latency or pipeline delay, so it is ideal for multiple-channel applications.

When a conversion is initiated, the analog input is sampled on internal capacitor, and then converted based on charge redistribution with an internal clock. During conversion, the input is disconnected from the internal capacitor.

After conversion, the device reconnects the sampling capacitors to input pins, and enters the acquisition phase.

#### **Functional Block Diagram**

#### **Feature Description**

#### **Analog Input**

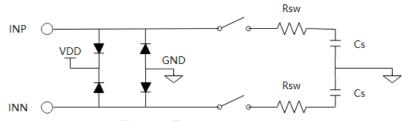

The following figure is the equivalent input sampling circuit. The sampling switch is represented by a resistance in series with the ideal switch. The electrostatic discharge (ESD) protection diodes from both

analog inputs are also shown in the Figure.

Figure 1. Equivalent Input Sampling Circuit

#### Reference

The device operates with an external reference voltage. During the conversion process, internal capacitors are switched onto the reference terminal, and a dynamic charge is required. The switching frequency is proportional to the internal conversion clock frequency. A reference driver circuit is required to support the dynamic charge so that the noise and linearity performance of the device is not degraded.

#### **ADC Transfer Function**

The device is a unipolar, differential input device, and the output is in twos complement format. The transfer equation is shown in the following table:

| Description                 | Analog Input | Digital output Code (Hex) |

|-----------------------------|--------------|---------------------------|

| Full-scale range            | 2*VREF       | -                         |

| Least Significant Bit (LSB) | 2*VREF/65536 | -                         |

| Positive full scale         | VREF – 1 LSB | 7FFF                      |

| Midscale                    | 0 V          | 0000                      |

| Midscale – 1 LSB            | 0 – 1LSB     | FFFF                      |

| Negative full scale         | -VREF        | 8000                      |

www.3peakic.com.cn 11 / 23 Rev.Pre.1

#### **Device Function Modes**

The device offers  $\overline{\text{CS}}$  mode and Daisy-chain mode for interfacing with the host.

The mode in which the device operates depends on the SDI level when the CNV rising edge occurs. The device operates in  $\overline{CS}$  mode if SDI is high at the CNV rising edge. If SDI is low at the CNV rising edge, or if SDI and CNV are connected, the device operates in daisy-chain mode.

In  $\overline{CS}$  mode, the device is compatible with SPI hosts. This interface can use a 3-wire or 4-wire interface. The 3-wire interface uses the CNV, SCK, and SDO signals, and minimizes the wiring connections, and is useful for isolation applications. The 4-wire interface using the SDI, CNV, SCK, and SDO signals, allows the user to sample the analog input independent of the serial interface timing, and is useful to control an individual device while having multiple similar devices on board.

In daisy-chain mode, multiple devices can be cascaded on a single data line similar to a shift register. This mode is useful to reduce component count and signal traces on the board.

In both modes, the device can either operate with or without a busy indicator, where the busy indicator is a bit preceding the output data bits that can be used to interrupt the digital host and trigger the data transfer.

#### **CS** Mode

The device operates in  $\overline{CS}$  mode if SDI is high at the CNV rising edge. There are four different interface options available in this mode: 3-wire  $\overline{CS}$  mode without a busy indicator, 3-wire  $\overline{CS}$  mode with a busy indicator, 4-wire  $\overline{CS}$  mode without a busy indicator, and 4-wire  $\overline{CS}$  mode with a busy indicator.

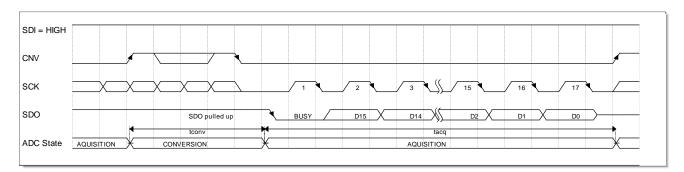

#### 3-wire $\overline{CS}$ Mode without Busy Indicator

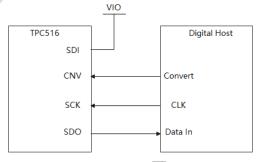

This mode is useful when a single ADC is connected to an SPI-compatible digital host.

In this mode, SDI can be connected to VIO. A CNV rising edge samples the input signal, causes the device to enter a conversion phase, and SDO is forced to 3-state. Conversion is done with an internal clock and continues regardless of the state of CNV. So CNV can be pulled low then to select other devices on the board.

However, CNV must return and hold high before the conversion time elapses. A high level on CNV at the end of the conversion ensures the device does not generate a busy indicator.

Figure 2. Connection Diagram: 3-Wire  $\overline{\text{CS}}$  Mode without Busy Indicator

www.3peakic.com.cn 12 / 23 Rev.Pre.1

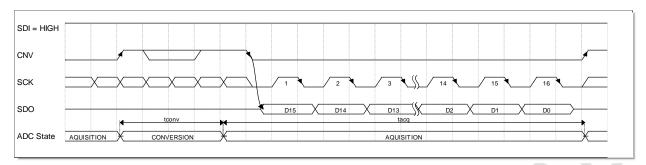

Figure 3. Timing Diagram: 3-Wire  $\overline{\text{CS}}$  Mode without Busy Indicator

On the CNV falling edge, SDO comes out of 3-state and the device outputs the MSB of the data at first, and then low data bits on subsequent SCK falling edges.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 16th SCK falling edge or when CNV goes high, whichever occurs first.

#### 3-wire $\overline{CS}$ Mode with a Busy Indicator

This mode is useful when a single ADC is connected to an SPI-compatible digital host and an interrupt-driven data transfer is required.

In this mode, SDI can be connected to VIO. A CNV rising edge samples the input signal, causes the device to enter a conversion phase, and SDO is forced to 3-state.

Conversion is done with an internal clock and continues regardless of the state of CNV. So CNV can be pulled low then to select other devices on the board.

A pull-up resistor on the SDO pin ensures that  $\overline{\text{IRQ}}$  pin of the digital host is held high when SDO is in 3-state. However, CNV must be pulled low before conversion time elapses. A low level of CNV at the end of conversion ensures the device generates a busy indicator.

Figure 4. Connection Diagram: 3-Wire  $\overline{\text{CS}}$  Mode with a Busy Indicator

www.3peakic.com.cn 13 / 23 Rev.Pre.1

Figure 5. Timing Diagram: 3-Wire  $\overline{\text{CS}}$  Mode with a Busy Indicator

When the conversion is complete, the device enters an acquisition state. SDO comes out of 3-state, and outputs a busy indicator bit (low level). This feature provides a high-to-low transition on the  $\overline{\text{IRQ}}$  pin of the digital host.

Then the data bits are clocked out on the subsequent SCLK falling edges, MSB first.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 17th SCK falling edge or when CNV goes high, whichever occurs first.

#### 4-wire $\overline{\text{CS}}$ Mode without Busy Indicator

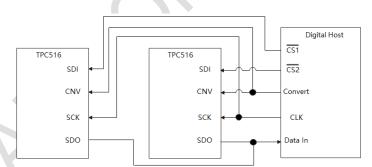

This mode is useful when one or more ADCs are connected to an SPI-compatible digital host. Following is the connection diagram of the two ADCs.

In this mode, SDI is controlled by the digital host and functions as  $\overline{\text{CS}}$ .

Figure 6. Connection Diagram: Two ADCs with 4-Wire CS Mode without Busy Indicator

Figure 7. Timing Diagram: Two ADCs with 4-Wire CS Mode without Busy Indicator

www.3peakic.com.cn 14 / 23 Rev.Pre.1

When SDI is high, a CNV rising edge samples the input signal, causes the device to enter a conversion phase, and forces SDO to 3-state.

In this mode, CNV must be held high from the start of the conversion until all data bits are read.

Conversion is done with the internal clock regardless of the state of SDI. So SDI (functioning as  $\overline{CS}$ ) can be pulled low to select other devices on the board.

However, SDI must return and hold high before the conversion time elapse. A high level on SDI at the end of the conversion ensures the device does not generate a busy indicator.

On the SDI falling edge, SDO comes out of 3-state and the device outputs the MSB of the data at first, and then low data bits on subsequent SCK falling edges.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 16th SCK falling edge or when SDI goes high, whichever occurs first.

When multiple devices are connected on the same data bus, the SDI of the second device (functioning as  $\overline{CS}$  for the second device) can go low after the first device data are read, and the SDO of the first device is in 3-state.

Care must be taken so that CNV and SDO of the devices are not low together during the read cycle.

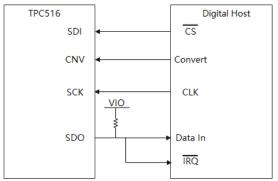

#### 4-wire $\overline{\text{CS}}$ Mode with a Busy Indicator

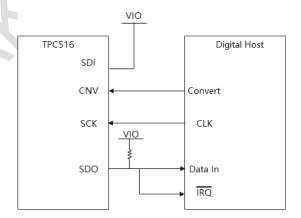

This mode is most useful when a single ADC is connected to a digital host and an interrupt-driven data transfer is desired.

In this mode, SDI is controlled by the digital host and functions as  $\overline{\text{CS}}$ .

A pull-up resistor on SDO pin ensures that  $\overline{IRQ}$  pin of the digital host is held high when SDO is in 3-state. When SDI is high, a CNV rising edge samples the input signal, causes the device to enter a conversion phase, and forces SDO to 3-state.

In this mode, CNV must be held high from the start of the conversion until all data bits are read.

Conversion is done with the internal clock regardless of the state of SDI. So, SDI (functioning as  $\overline{CS}$ ) can be pulled low to select other devices on the board.

However, CNV must be pulled low before conversion time elapses. A low level of CNV at the end of conversion ensures the device generates a busy indicator.

Figure 8. Connection Diagram: 4-Wire  $\overline{\text{CS}}$  Mode with a Busy Indicator

www.3peakic.com.cn 15 / 23 Rev.Pre.1

Figure 9. Timing Diagram: 4-Wire  $\overline{CS}$  Mode with a Busy Indicator

When the conversion is complete, the device enters an acquisition state. SDO comes out of 3-state, and outputs a busy indicator bit (low level). This feature provides a high-to-low transition on the  $\overline{\text{IRQ}}$  pin of the digital host.

Then the data bits are clocked out on the subsequent SCLK falling edges, MSB first.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 17th SCK falling edge or when SDI goes high, whichever occurs first. Care must be taken so that CNV and SDO of the devices are not low together during the read cycle.

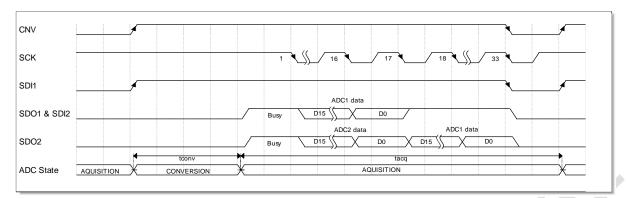

#### **Daisy-Chain Mode**

Daisy-chain mode is selected if SDI is low at CNV rising edge or if SDI and CNV are connected.

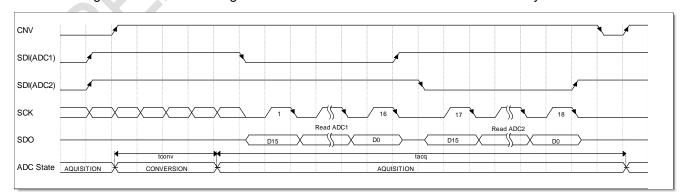

#### **Daisy-Chain Mode without Busy Indicator**

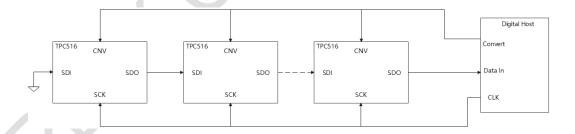

This mode is useful in applications where the digital host has limited interfacing capability with multiple ADCs. In this mode, the CNV pins of all ADCs in the chain are connected and are controlled by a single pin of the digital host. The SCK pins are also connected and controlled by a single pin of the digital host.

Figure 10. Connection Diagram: Daisy-Chain Mode without Busy Indicator

www.3peakic.com.cn 16 / 23 Rev.Pre.1

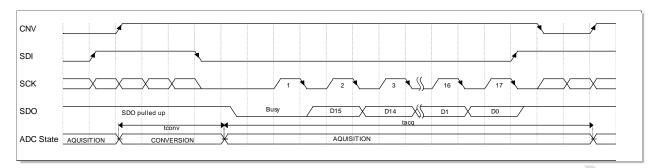

Figure 11. Timing Diagram: Daisy-Chain Mode without Busy Indicator

The SDO pin is driven low when SDI and CNV are both low.

A CNV rising edge with SDI low selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase.

In this mode, CNV must remain high from the start of the conversion until all data bits are read. When started, the conversion continues with an internal clock, regardless of the state of SCK.

However, SCK must be low at the CNV rising edge so that the device does not generate a busy indicator at the end of the conversion.

At the end of the conversion, every ADC in the chain outputs the MSB bit of the conversion result on its own SDO pin. The internal shift register of each ADC latches the data available on its SDI pin and shifts out the next bit of data on its SDO pin on every subsequent SCK falling edge.

Therefore, the digital host receives the data of ADC N at first (MSB first), followed by the data of ADC N–1, and so on. A total of 16 x N SCK falling edges are required to capture the outputs of all N devices in the chain. The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

#### Daisy-Chain Mode with a Busy Indicator

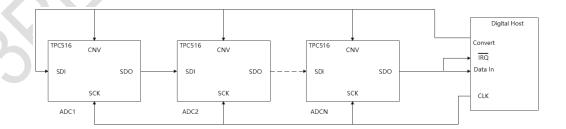

This mode is useful in applications where the digital host has limited interfacing capability with multiple ADCs, and an interrupt-driven data transfer is desired.

In this mode, the CNV pins of all ADCs in the chain are connected and are controlled by a single pin of the digital host. The SCK pins are also connected and controlled by a single pin of the digital host.

Figure 12. Connection Diagram: Daisy-Chain Mode with a Busy Indicator

www.3peakic.com.cn 17 / 23 Rev.Pre.1

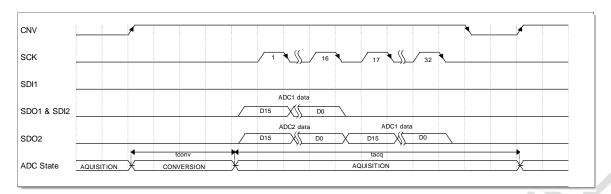

Figure 13. Timing Diagram: Daisy-Chain Mode with a Busy Indicator

The SDO pin is driven low when SDI and CNV are both low.

A CNV rising edge with SDI low selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase.

In this mode, CNV must remain high from the start of the conversion until all data bits are read. When started, the conversion continues with an internal clock, regardless of the state of SCK.

However, SCK must be high at the CNV rising edge so that the device generates a busy indicator at the end of the conversion.

At the end of conversion, every ADC in the chain forces its SDO pin high, providing a low-to-high transition on the  $\overline{IRQ}$  pin of the digital host. The internal shift register of each ADC latches the data available on its SDI pin and shifts out the next bit of data on its SDO pin on every subsequent SCK falling edge. Therefore, the digital host receives the interrupt signal followed by the data of ADC N (MSB first), and then the data of ADC N–1, and so on. A total of  $(16 \times N) + 1$  SCK falling edges are required to capture the outputs of all N devices in the chain. The busy indicator bits of ADC 1 to ADC N–1 do not propagate to the next device in the chain.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

www.3peakic.com.cn 18 / 23 Rev.Pre.1

#### **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

The input driver and the reference driver circuits are two important circuits to maximize the performance of a high-precision, SAR ADC. Some general principles should be followed for designing these circuits.

#### **Typical Application**

### Layout

#### **Layout Guideline**

Both input capacitors and output capacitors must be placed to the device pins as close as possible.

It is recommended to bypass the input pin to ground with a 0.1 µF bypass capacitor.

It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

The exposed pad must be connected to the PCB ground plane directly, the copper area must be as large as possible.

#### **Layout Example**

www.3peakic.com.cn 19 / 23 Rev.Pre.1

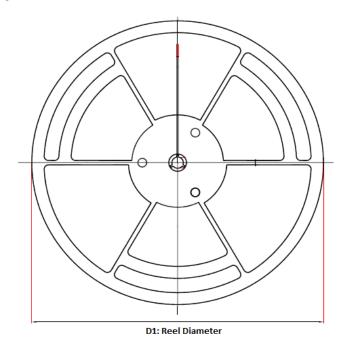

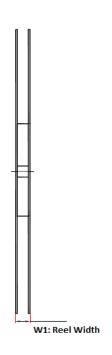

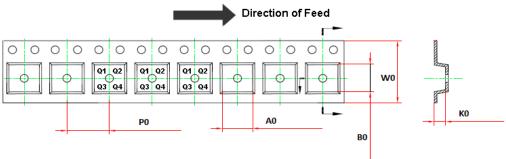

# **Tape and Reel Information**

| Order Number | Package | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|--------------|---------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPC5160-VS2R | MSOP10  | 330        | 17.6       | 5.2        | 3.3        | 1.5        | 8          | 12         | Q1               |

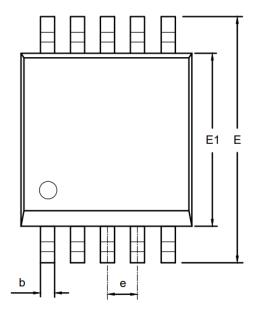

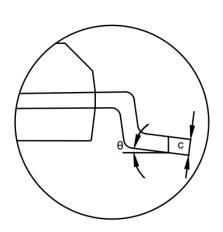

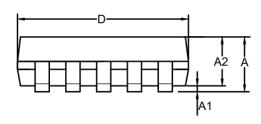

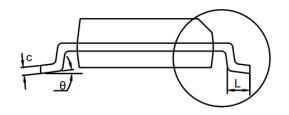

# Package Outline Dimensions MSOP10

#### NOTES

- 1. Do not include mold flash or protrusion.

- 2. This drawing is subject to change without notice.

| Symbol |       | ensions<br>Ilimeters | Dimensions<br>In Inches |                |  |  |

|--------|-------|----------------------|-------------------------|----------------|--|--|

|        | MIN   | MAX                  | MIN                     | MAX            |  |  |

| Α      | 0.800 | 1.100                | 0.031                   | 0.043          |  |  |

| A1     | 0.050 | 0.150                | 0.002                   | 0.006          |  |  |

| A2     | 0.750 | 0.950                | 0.030                   | 0.037          |  |  |

| b      | 0.180 | 0.280                | 0.007                   | 0.011          |  |  |

| С      | 0.090 | 0.230                | 0.004                   | 0.009          |  |  |

| D      | 2.900 | 3.100                | 0.114                   | 0.122          |  |  |

| E      | 4.700 | 5.100                | 0.185                   | 0.201<br>0.122 |  |  |

| E1     | 2.900 | 3.100                | 0.114                   |                |  |  |

| е      | 0.500 | 0 BSC                | 0.020 BSC               |                |  |  |

| L      | 0.400 | 0.800                | 0.016                   | 0.031          |  |  |

| θ      | 0     | 8°                   | 0                       | 8°             |  |  |

|        |       |                      |                         |                |  |  |

### **Order Information**

| Order Number | Operating Temperature<br>Range | Package | Marking<br>Information | MSL  | Transport Media,<br>Quantity | Eco Plan |  |

|--------------|--------------------------------|---------|------------------------|------|------------------------------|----------|--|

| TPC5160-VS2R | −40 to 125°C                   | MSOP10  | 5160                   | MSL1 | Tape and Reel, 3000          | Green    |  |

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

**♣** 3PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All other trademarks are the property of their respective owners.