## RTD2120-series

8051 Embedded Micro-Controller for Monitor

Fully Technology Revision Version 1.06 Last updated: 2007/4/3

## **Revision History**

| Rev. | Description                                                             | Date      |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| 1.02 | 1. CLKO2( XFR FF01[1] ) default value 1 à 0                             | 2006/2/9  |  |  |  |  |  |  |  |

|      | 2. PLL_TEST(XFR FF10[7] ) à PLL_STA                                     |           |  |  |  |  |  |  |  |

|      | 3. revise the "Reset table"                                             |           |  |  |  |  |  |  |  |

| 1.03 | 1. revise the SFR table à delete address 93, B3                         | 2006/8/1  |  |  |  |  |  |  |  |

|      | 2. add PWM description                                                  |           |  |  |  |  |  |  |  |

|      | 3. add power supply current                                             |           |  |  |  |  |  |  |  |

|      | 4. add description "All NC pin must be left unconnected or be connected |           |  |  |  |  |  |  |  |

|      | to GND."                                                                |           |  |  |  |  |  |  |  |

| 1.04 | 1. added RTD2120K, QFP44 pin config.                                    | 2007/1/16 |  |  |  |  |  |  |  |

|      | 2. added RTD2120K, QFP44 pin description.                               |           |  |  |  |  |  |  |  |

| 1.05 | 1. added reset pulse minimum length is 16 MCU clk cycle (page-10)       | 2007/2/9  |  |  |  |  |  |  |  |

| 1.06 | 1. modified WDT block diagram                                           | 2007/4/3  |  |  |  |  |  |  |  |

#### Overview

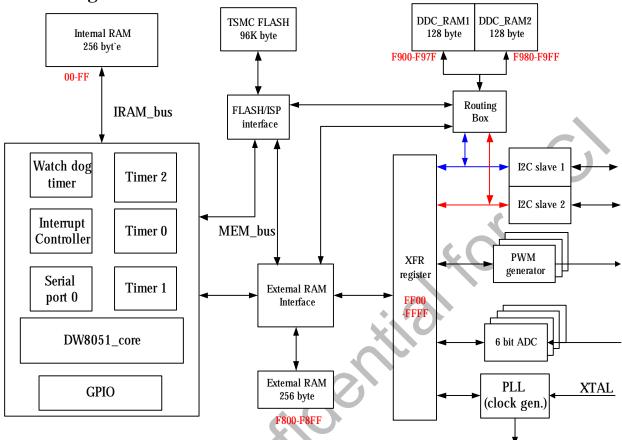

This chip is the micro-processor of LCD monitor. It uses the Designware DW8051 of Synopsys as the 8051 core of this chip and is compatible with other industry 8051 series. Also, 96Kbyte FLASH with 8 bit bus is embedded in this chip which is licensed from TSMC 0.18um e-FLASH process. Here we use the package of PLCC44/LQFP48/QFP44 if we would like to have a discrete MCU controller or we make a multi-chip package with our LCD monitor controller to form one chip package to save the cost of package and PCB material.

#### **Features**

- I Operating voltage range: 3.0V to 3.6V

- 8051 core, CPU operating frequency up to 50MHz

- I 4 clocks per machine cycle

- **l** 256-byte internal RAM

- 512-byte external data RAM, including 256-byte DDC RAM(128-byte x 2) and 256-byte general purpose RAM

- 96K-byte flash memory, 64k for program and 32k for saving parameter

- I Two DDC ports compliant with VESA DDC1/2B/2Bi/CI

- I Three channels of PWM DAC with programmable frequency from 100K to 100Hz

- Watchdog timer with programmable interval

- Three 16-bit counters/timers (T0, T1, and T2)

- I One PLL to provide programmable operating frequency and clock output, 2 clock output ports

- I One full-duplex serial port

- I Six interrupt sources with 2 external interrupts

- I Four channels of 6-bit ADC

- Hardware In System Programming(ISP) capability, no boot code required

- Built-in Low voltage reset circuit

- I Embedded 1.8V regulator

- I Code protection

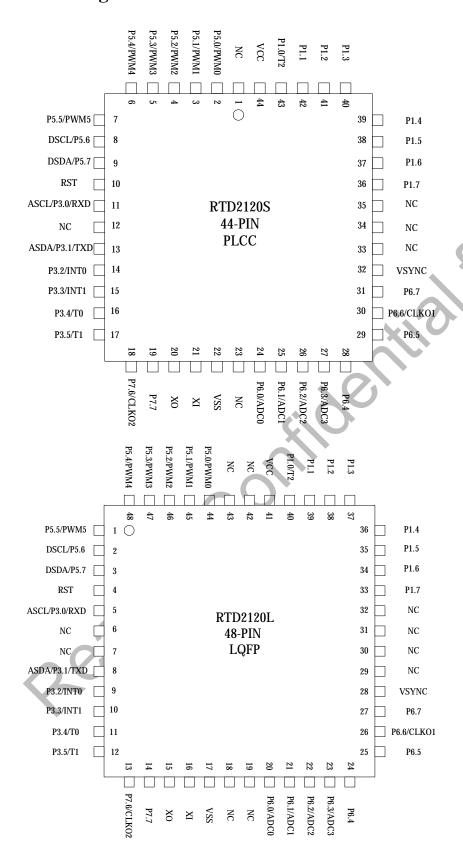

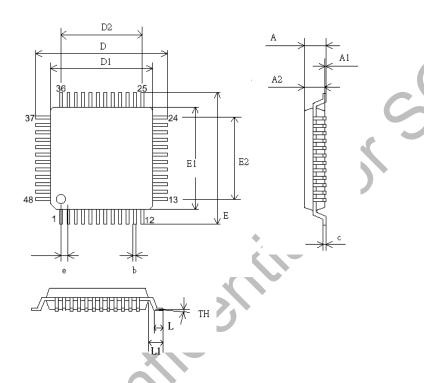

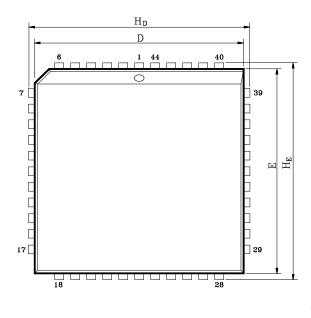

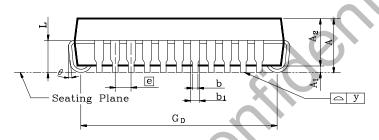

- Available in 44-pin PLCC, 44-pin QFP or 48-pin LQFP package

# **Pin Configurations**

|               |    | P5.4/PWM4  | P5.3/PWM3 | P5.2/PWM2 | P5.1/PWM1 | P5.0/PWM0 | NC   | VCC      | P1.0/T2  | P1.1     | P1.2     | P1.3 |    |            |

|---------------|----|------------|-----------|-----------|-----------|-----------|------|----------|----------|----------|----------|------|----|------------|

|               |    | 44         | 43        | 42        | 41        | 40        | 39   | 38       | 37       | 36       | 35       | 34   |    |            |

| P5.5/PWM5     | 1  | $\bigcirc$ |           |           |           |           |      |          |          |          |          |      | 33 | P1.4       |

| DSCL/P5.6     | 2  |            |           |           |           |           |      |          |          |          |          |      | 32 | P1.5       |

| DSDA/P5.7     | 3  |            |           |           |           |           |      |          |          |          |          |      | 31 | P1.6       |

| RST           | 4  |            |           |           |           |           |      |          |          |          |          |      | 30 | P1.7       |

| ASCL/P3.0/RXD | 5  |            |           |           |           | RT        | D21  | 20K      |          |          |          |      | 29 | NC         |

| NC            | 6  |            |           |           |           | 4         | 4-PI |          |          |          |          |      | 28 | NC         |

| ASDA/P3.1/TXD | 7  |            |           |           |           |           | QFI  | )        |          |          |          |      | 27 | NC         |

| P3.2/INT0     | 8  |            |           |           |           |           |      |          |          |          |          |      | 26 | VSYNC      |

| P3.3/INT1     | 9  |            |           |           |           |           |      |          |          |          |          |      | 25 | P6.7       |

| P3.4/T0       | 10 |            |           |           |           |           |      |          |          |          |          |      | 24 | P6.6/CLKO1 |

| P3.5/T1       | 11 |            |           |           |           |           |      |          |          |          |          |      | 23 | P6.5       |

|               |    | 12         | 13        | 14        | 15        | 16        | 17   | 18       | 19       | 20       | 21       | 22   |    |            |

|               |    | P7.6/CLKC  | P7.7      | XO        | XI        | VSS       | NC   | P6.0/ADC | P6.1/ADC | P6.2/ADC | P6.3/ADC | P6.4 |    |            |

## **Block Diagram**

Segrificate C.C.

# **Pin Description**

| P     | in No. |     | Name                                    | I/O  | Internal | Default     | Pin Type         | Description                                   |

|-------|--------|-----|-----------------------------------------|------|----------|-------------|------------------|-----------------------------------------------|

| PI CC | LQFP   | QFP |                                         |      | Pull     | output      |                  |                                               |

| 44    | 48     | 44  |                                         |      | Up/Down  | value       |                  |                                               |

| 2     | 44     | 40  | P5.0/PWM0                               | I/O  |          | 1(P5.0)     | Open<br>Drain    | General purpose I/O /<br>PWM0 output          |

| 3     | 45     | 41  | P5.1/PWM1                               | I/O  |          | 1(P5.1)     | Open<br>Drain    | General purpose I/O / PWM1 output             |

| 4     | 46     | 42  | P5.2/PWM2                               | I/O  |          | 1(P5.2)     | Open<br>Drain    | General purpose I/O / PWM2 output             |

| 5     | 47     | 43  | P5.3/PWM3                               | I/O  |          | 1(P5.3)     | Open<br>Drain    | General purpose I/O /<br>PWM3 output          |

| 6     | 48     | 44  | P5.4/PWM4                               | I/O  |          | 1(P5.4)     | Open<br>Drain    | General purpose I/O /<br>PWM4 output          |

| 7     | 1      | 1   | P5.5/PWM5                               | I/O  |          | 1(P5.5)     | Open<br>Drain    | General purpose I/O /<br>PWM5 output          |

| 8     | 2      | 2   | P5.6/DSCL                               | I/O  |          | 1(P5.6)     | Open<br>Drain    | General purpose I/O /<br>DVI DDC SCL          |

| 9     | 3      | 3   | P5.7/DSDA                               | I/O  | 4        | 1(P5.7)     | Open             | General purpose I/O /                         |

|       |        |     | 10,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1, 0 | . 0      | 1(2 (), / ) | Drain            | DVI DDC SDA                                   |

| 10    | 4      | 4   | RST                                     | I    | Down     | 0           | Input            | High active RESET                             |

| 11    | 5      | 5   | ASCL/P3.0/RXD                           | I/O  | 1        | 1(ASCL)     | Open<br>Drain    | ADC DDC SCL /<br>General purpose I/O /<br>RXD |

| 13    | 8      | 7   | ASDA/P3.1/TXD                           | I/O  | -        | 1(ASDA)     | Open<br>Drain    | ADC DDC SDA /<br>General purpose I/O /<br>TXD |

| 14    | 9      | 8   | P3.2/INT0                               | I/O  |          | 1(P3.2)     | Standard<br>8051 | General purpose I/O /<br>External interrupt 0 |

| 15    | 10     | 9   | P3.3/INT1                               | I/O  |          | 1(P3.3)     | Standard<br>8051 | General purpose I/O /<br>External interrupt 1 |

| 16    | 11     | 10  | P3.4/T0                                 | I/O  |          | 1(P3.4)     | Standard<br>8051 | General purpose I/O /<br>Timer 0              |

| 17    | 12     | 11  | P3.5/T1                                 | I/O  |          | 1(P3.5)     | Standard<br>8051 | General purpose I/O /<br>Timer 1              |

| 18    | 13     | 12  | P7.6/CLKO2                              | I/O  | Up       | 1           | Push-Pull        |                                               |

| 19    | 14     | 13  | P7.7                                    | I/O  | Up       | 1           | Push-Pull        | General purpose I/O                           |

| 20    | 15     | 14  | XO                                      | О    |          |             |                  | Crystal out                                   |

| 21    | 16     | 15  | XI                                      | I    |          |             |                  | Crystal in                                    |

| 22    | 17     | 16  | VSS                                     |      |          |             |                  | Ground                                        |

| P    | in No. |     | Name       | I/O | Internal        | Default         | Pin Type                       | Description                               |

|------|--------|-----|------------|-----|-----------------|-----------------|--------------------------------|-------------------------------------------|

| PLCC | LQFP   | QFP |            |     | Pull<br>Up/Down | output<br>value |                                |                                           |

| 24   | 20     | 18  | P6.0/ADC0  | I/O | Up              | 1(P6.0)         | Push-Pull                      | General purpose I/O /<br>ADC 0 input      |

| 25   | 21     | 19  | P6.1/ADC1  | I/O | Up              | 1(P6.1)         | Push-Pull                      | General purpose I/O /<br>ADC 1 input      |

| 26   | 22     | 20  | P6.2/ADC2  | I/O | Up              | 1(P6.2)         | Push-Pull                      | General purpose I/O /<br>ADC 2 input      |

| 27   | 23     | 21  | P6.3/ADC3  | I/O | Up              | 1(P6.3)         | Push-Pull                      |                                           |

| 28   | 24     | 22  | P6.4       | I/O | Up              | 1               | Push-Pull                      | General purpose I/O                       |

| 29   | 25     | 23  | P6.5       | I/O | Up              | 1               | Push-Pull                      | General purpose I/O                       |

| 30   | 26     | 24  | P6.6/CLKO1 | I/O | Up              | 1(P6.6)         | Push-Pull                      | General purpose I/O /<br>Clock out 1      |

| 31   | 27     | 25  | P6.7       | I/O | Up              | 1               | Push-Pull                      | General purpose I/O                       |

| 32   | 28     | 26  | VSYNC      | I   | Down            | 0               | Input                          | VSYNC input                               |

| 36   | 33     | 30  | P1.7       | I/O | .0              | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 37   | 34     | 31  | P1.6       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 38   | 35     | 32  | P1.5       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 39   | 36     | 33  | P1.4       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 40   | 37     | 34  | P1.3       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 41   | 38     | 35  | P1.2       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 42   | 39     | 36  | P1.1       | I/O |                 | 1               | Standard<br>8051/<br>Push-Pull | General purpose I/O                       |

| 43   | 40     | 37  | P1.0/ET2   | I/O |                 | 1(P1.0)         | Standard<br>8051/<br>Push-Pull | General purpose I/O /<br>External Timer 2 |

| 44   | 41     | 38  | VCC        |     |                 |                 |                                | Power                                     |

Note: All NC pin must be left unconnected or be connected to GND.

## DW8051 micro-processor

The DW8051 contained in RTD2120 is compatible with industry standard 803x/805x and provides the following design features and enhancements to the standard 8051 microcontroller:

## 1. High speed architecture

Compared to standard 8051, the DW8051 processor core provides increased performance by executing instructions in a 4-clock bus cycle, as opposed to the 12-clock bus cycle in the standard 8051. The shortened bus timing improves the instruction execution rate for most instructions by a factor of three over the standard 8051 architectures. The average speed improvement for the entire instruction set is approximately 2.5X.

## 2. Stretch Memory Cycles

The stretch memory cycle feature enables application software to adjust the speed of data memory access. The DW8051 can execute the MOVX instruction in as little as 2 instruction cycles. However, it is sometimes desirable to stretch this value; for example, to access slow memory or slow memory-mapped peripherals such as UARTs or LCDs.

The three LSBs of the Clock Control Register (at SFR location 8Eh) control the stretch value. You can use stretch values between zero and seven. A stretch value of zero adds zero instruction cycles, resulting in MOVX instructions executing in two instruction cycles. A stretch value of seven adds seven instruction cycles, resulting in MOVX instructions executing in nine instruction cycles. The stretch value can be changed dynamically under program control.

By default, the stretch value resets to one (three cycle MOVX). For full-speed data memory access, the software must set the stretch value to zero. The stretch value affects only data memory access. The only way to reduce the speed of program memory (ROM) access is to use a slower clock.

#### 3. Dual Data Pointers

The DW8051 employs dual data pointers to accelerate data memory block moves. The standard 8051 data pointer (DPTR) is a 16-bit value used to address external data RAM or peripherals. The DW8051 maintains the standard data pointer as DPTR0 at SFR locations 82h and 83h. It is not necessary to modify code to use DPTR0.

The DW8051 adds a second data pointer (DPTR1) at SFR locations 84h and 85h. The SEL bit in the DPTR Select register, DPS (SFR 86h), selects the active pointer. When SEL = 0, instructions that use the DPTR will use DPL0 and DPH0. When SEL = 1, instructions that use the DPTR will use DPL1 and DPH1. SEL is the bit 0 of SFR location 86h. No other bits of SFR location 86h are used.

All DPTR-related instructions use the currently selected data pointer. To switch the active pointer, toggle the SEL bit. The fastest way to do so is to use the increment instruction (INC DPS). This requires only one instruction to switch from a source address to a destination address, saving application code from having to save source and destination addresses when doing a block move.

Using dual data pointers provides significantly increased efficiency when moving large blocks of data.

#### 4. Timer Rate Control

One important difference exists between the RTD2120 and 80C32 regarding timers. The original 80C32 used a 12 clock per cycle scheme for timers and consequently for some serial baud rates(depending on the mode). The RTD2120 architecture normally runs using 4 clocks per cycle. However, in the area of timers, it will default to a 12 clock per cycle scheme on a reset. This allows existing code with real—time dependencies such as baud rates to operate properly. If an application needs higher speed timers or serial baud rates, the timers can be set to run at the 4 clock rate.

The Clock Control register (CKCON – 8Eh) determines these timer speeds. When the relevant CKCON bit is a logic 1, the device uses 4 clocks per cycle to generate timer speeds. When the control bit is set to a zero, the device uses 12 clocks for timer speeds. The reset condition is a 0. CKCON.5 selects the speed of Timer 2. CKCON.4 selects Timer 1 and CKCON.3 selects Timer zero. Note that unless a user desires very fast timing, it is unnecessary to alter these bits. Note that the timer controls are independent.

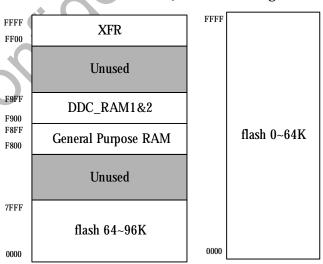

## **Memory Organization**

#### Internal Data memory

- **l** 256 bytes of internal RAM

- 1 128 bytes of Special Function Register (SFR)

#### External Data memory

- 1 128 bytes of External Special Function Register (XFR)

- 256 bytes of DDCRAM(128-bytex2)

- 1 256 bytes of general purpose RAM

- I 32k bytes of flash for EDID data and other parameters

#### External Program memory

- I 64k bytes of flash for program memory

- I The program content can not be read out unless user mass erase the flash first.

#### **Internal Data Memory**

# FF Internal RAM SFR Indirect addressing Direct addressing 7F Internal RAM Direct/Indirect addressing 00

## External Data Memory External Program Memory

## Reset

There are five reset sources in RTD2120, as described below:

- I RST pin

- The external reset is high active and its pulse width must be larger than 16 mcu clock cycles. The RST pin can reset the whole chip of RTD2120.

- Low voltage reset(LVR) and power on reset(POR)

The LVR and POR monitor the power status of RTD2120. The same as external reset, the LVR and POR will reset the whole chip of RTD2120 when triggered.

- Software reset

To activate software reset, set FF39[1](SOF\_RST). When software reset is triggered, it will reset all modules except debug mode.

- I Watchdog timer(WDT)

- The watchdog timer generates reset when it is overflowed. The watchdog timer resets almost the same modules as software reset except itself(watchdog timer module).

- In System Programing(ISP) reset

- ISP reset will generate when entering ISP mode. Compared to Watchdog timer reset, ISP mode resets almost the same modules as Watchdog timer except itself(ISP module).

|                | Debug mode<br>module | Watchdog timer module |   | ISP module and other modules |

|----------------|----------------------|-----------------------|---|------------------------------|

| RST pin        | 0                    | 0                     | 0 | 0                            |

| LVR & POR      | 0                    | 0                     | 0 | 0                            |

| Software reset | X                    | 0                     | 0 | 0                            |

| WDT reset      | X                    | X                     | 0 | X                            |

| ISP reset      | X                    | X                     | 0 | X                            |

Note: O = Reset, x = No effect

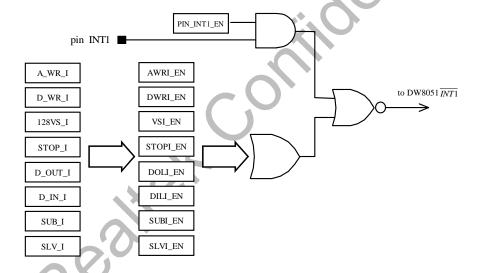

## Interrupt

Six interrupts are provided in RTD2120. Four of these are generated automatically by internal operation: timer 0, timer 1, timer 2 and the serial port interrupt. The other two interrupts are triggered by external pins: INT0 and INT1. Moreover, the DDC and IIC interrupts are connected to DW8051  $\overline{INT1}$  source as the following figure.

#### Timer/Counter

RTD2120 has three timers/counters: T0, T1 and T2. T0 and T1 are fully compatible to timer/counter in standard 8051's. Like timer2 in 8052, T2 of RTD2120 has three operating modes: 16-bit timer/counter with capture, 16-bit auto-reload timer/counter and Baud rate generator. However, T2 of RTD2120 does not support "Timer2 output enable(T2OE)" and "downcount enable(DCEN)". The SFRs associated with Timer2 are listed below.

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Addr |

|----------|-------|-------|-------|-------|-------|-------|-------|--------|------|

| T2CON    | TF2   | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | C/T2  | CP/RL2 | C8h  |

| RCAP2L   |       |       |       |       |       |       |       |        | CAh  |

| RCAP2H |  |  |  |  | CBh |

|--------|--|--|--|--|-----|

| TL2    |  |  |  |  | CCh |

| TH2    |  |  |  |  | CDh |

## 1. 16-bit timer/counter with capture

The Timer 2 capture mode is the same as the 16-bit timer/counter with the addition of the capture registers and control signals. If EXEN2 = 0, Timer2 is a 16-bit timer/counter. The C/T2 bit determines whether the 16-bit counter counts osc cycles (divided by 4 or 12), or high-to-low transitions on the P1.0 pin. The TR2 bit enables the counter. When the count increments from FFFFh, the TF2 flag is set.

The CP/RL2 bit in the T2CON SFR enables the capture feature. When CP/RL2 = 1, a high-to-low transition on P1.1 when EXEN2 = 1 causes the Timer 2 value to be loaded into the capture registers (RCAP2L and RCAP2H).

## 2. 16-bit timer/counter with auto-reload

When CP/RL2 = 0, Timer 2 is configured for the auto-reload mode. Control of counter input is the same as for the other 16-bit counter modes. When the count increments from FFFFh, Timer 2 sets the TF2 flag and the starting value is reloaded into TL2 and TH2. The software must preload the starting value into the RCAP2L and RCAP2H registers. When Timer 2 is in auto-reload mode, a reload can be forced by a high-to-low transition on the P1.1 pin, if enabled by EXEN2 = 1.

## 3. Baud rate generator

Setting either RCLK or TCLK to 1 configures Timer 2 to generate baud rates for Serial Port 0 in serial mode 1 or 3. In baud rate generator mode, Timer 2 functions in auto-reload mode. However, instead of setting the TF2 flag, the counter overflow generates a shift clock for the serial port function. As in normal auto-reload mode, the overflow also causes the preloaded start value in the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers. When either TCLK = 1 or RCLK = 1, Timer 2 is forced into auto-reload operation, regardless of the state of the CP/RL2 bit. When operating as a baud rate generator, Timer 2 does not set the TF2 bit. In this mode, a Timer 2 interrupt can only be generated by a high-to-low transition on the P1.1 pin setting the EXF2 bit, and only if enabled by EXEN2 = 1.

The counter time base in baud rate generator mode is osc/2. To use an external clock source, set C/T2 to 1 and apply the desired clock source to the P1.0 pin.

## **Special Function Registers(SFR)**

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Value<br>(Hex) | Addr<br>(Hex) |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------|---------------|

| SP       |       |       |       |       |       |       |       |       | 07                      | 81            |

| DPL0     |       |       |       |       |       |       |       |       | 00                      | 82            |

| DPH0     |       |       |       |       |       |       |       |       | 00                      | 83            |

| DPL1     |       |       |       |       |       |       |       |       | 00                      | 84            |

| DPH1     |       |       |       |       |       |       |       |       | 00                      | 85            |

| DPS      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | SEL   | 00                      | 86            |

| PCON     | SMOD0 |       | 1     | 1     | GF1   | GF0   | STOP  | IDLE  | 30                      | 87            |

| TCON     | TF1   | TR1   | TF0   | TR0   | IE1   | IT1   | IE0   | IT0   | 00                      | 88            |

| TMOD     | GATE  | C/T   | M1    | M0    | GATE  | C/T   | M1    | M0    | 00                      | 89            |

| TL0      |       |       |       |       |       |       |       |       | 00                      | 8A            |

| Dagistan        | D:4 7           | D:4 6           | D:4 5           | D:4 4           | D:4 2           | D:4 2           | D:4 1           | D:4 0           | Reset          | Addr          |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|---------------|

| Register        | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1           | Bit 0           | Value (Hex)    | (Hex)         |

| TL1             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | 8B            |

| TH0             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | 8C            |

| TH1             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | 8D            |

| CKCON           |                 |                 | T2M             | T1M             | T0M             | MD2             | MD1             | MD0             | 01             | 8E            |

| SPC_FNC         | 0               | 0               | 0               | 0               | 0               | 0               | 0               | WRS             | 00             | 8F            |

| P1              | P1.7            | P1.6            | P1.5            | P1.4            | P1.3            | P1.2            | P1.1            | P1.0            | FF             | 90            |

| MPAGE           |                 |                 |                 |                 |                 |                 |                 |                 | 00             | 92            |

| <del>P1_R</del> | <del>P1.7</del> | <del>P1.6</del> | <del>P1.5</del> | <del>P1.4</del> | <del>P1.3</del> | <del>P1.2</del> | <del>P1.1</del> | P1.0            | <del>F</del> F | 93            |

| SCON0           | SM0             | SM1             | SM2             | REN             | TB8             | RB8             | TI              | RI              | 00             | 98            |

| SBUF0           |                 |                 |                 |                 |                 |                 |                 |                 | 00             | 99            |

| P2              | P2.7            | P2.6            | P2.5            | P2.4            | P2.3            | P2.2            | P2.1            | P2.0            | 00             | A0            |

| IE              | EA              | 0               | ET2             | ES0             | ET1             | EX1             | ET0             | EX0             | 00             | A8            |

| P3              | P3.7            | P3.6            | P3.5            | P3.4            | P3.3            | P3.2            | P3.1            | P3.0            | FF             | B0            |

| <del>P3_R</del> | <del>P3.7</del> | <del>P3.6</del> | <del>P3.5</del> | <del>P3.4</del> | <del>P3.3</del> | <del>P3.2</del> | <u>P3.1</u>     | <del>P3.0</del> | <del>FF</del>  | <del>B3</del> |

| IP              | 1               | 0               | PT2             | PS0             | PT1             | PX1             | PT0             | PX0             | 80             | B8            |

| T2CON           | TF2             | EXF2            | RCLK            | TCLK            | EXEN2           | TR2             | C/T2            | CP/RL2          | 00             | C8            |

| RCAP2L          |                 |                 |                 |                 |                 |                 |                 |                 | 00             | CA            |

| RCAP2H          |                 |                 |                 |                 |                 |                 |                 |                 | 00             | CB            |

| TL2             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | CC            |

| TH2             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | CD            |

| PSW             | CY              | AC              | F0              | RS1             | RS0             | OV              | F1              | P               | 00             | D0            |

| ACC             |                 |                 |                 |                 |                 |                 |                 |                 | 00             | E0            |

| В               |                 |                 |                 | X               |                 |                 |                 |                 | 00             | F0            |

# **External Special Function Registers(XFR)**

# Pin Share

| Register:: | :Pin_share0 |            |             | 0xFF00                          |  |  |  |  |  |

|------------|-------------|------------|-------------|---------------------------------|--|--|--|--|--|

|            |             |            |             |                                 |  |  |  |  |  |

| Name       | Bits        | Read/Write | Reset State | Comments                        |  |  |  |  |  |

| Reserved   | 7           |            | 0           | Reserved                        |  |  |  |  |  |

| IIC2E      | 6           | R/W        | 1           | 0: Pin "P5.6/DSCL" is P5.6, Pin |  |  |  |  |  |

|            |             |            |             | "P5.7/DSDA" is P5.7             |  |  |  |  |  |

|            |             |            |             | 1: Pin "P5.6/DSCL" is DSCL, Pin |  |  |  |  |  |

|            |             |            |             | "P5.7/DSDA" is DSDA             |  |  |  |  |  |

| PWM5E      | 5           | R/W        | 0           | 0: Pin "P5.5/PWM5" is P5.5      |  |  |  |  |  |

|            |             |            |             | 1: Pin "P5.5/PWM5" is PWM5      |  |  |  |  |  |

| PWM4E      | 4           | R/W        | 0           | 0: Pin "P5.4/PWM4" is P5.4      |  |  |  |  |  |

|            |             |            |             | 1: Pin "P5.4/PWM4" is PWM4      |  |  |  |  |  |

| PWM3E      | 3           | R/W        | 0           | 0: Pin "P5.3/PWM3" is P5.3      |  |  |  |  |  |

|            |             |            |             | 1: Pin "P5.3/PWM3" is PWM3      |  |  |  |  |  |

| PWM2E      | 2           | R/W        | 0           | 0: Pin "P5.2/PWM2" is P5.2      |  |  |  |  |  |

|            |             |            |             | 1: Pin "P5.2/PWM2" is PWM2      |  |  |  |  |  |

| PWM1E | 1 | R/W | 0 | 0: Pin "P5.1/PWM1" is P5.1<br>1: Pin "P5.1/PWM1" is PWM1 |

|-------|---|-----|---|----------------------------------------------------------|

| PWM0E | 0 | R/W | 0 | 0: Pin "P5.0/PWM0" is P5.0<br>1: Pin "P5.0/PWM0" is PWM0 |

| Register:         | :Pin_share1 |            |             | 0xFF01                                                                                                                                |

|-------------------|-------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Name              | Bits        | Read/Write | Reset State | Comments                                                                                                                              |

| A_DDC_PIN_<br>SEL | 7           | R/W        | 0           | O: ADC DDC ports are connected to ASDA/ASCL  1: ADC DDC ports are connected to DSDA/DSCL  O: ADC DDC ports are connected to DSDA/DSCL |

| D_DDC_PIN_<br>SEL | 6           | R/W        | 1           | 0: DVI DDC ports are connected to ASDA/ASCL 1: DVI DDC ports are connected to DSDA/DSCL                                               |

| Reserved          | 5:3         |            | 0           | Reserved                                                                                                                              |

| PIN_INT1_E<br>N   | 2           | R/W        | 1           | Pin "P3.3/INT1" connect to 8051 INT1 enable 0: disable 1: enable when Pin "P3.3/INT1" is used as GPIO, this bit must be 0.            |

| CLKO2E            | 1           | R/W        | 0           | 0: Pin "P7.6/CLKO2" is P7.6<br>1: Pin "P7.6/CLKO2" is CLKO2                                                                           |

| ПС1Е              | 0           | R/W        | 1           | 0: Pin "ASCL/P3.0/Rxd" is P3.0/RXD, Pin "ASDA/P3.1/Txd" is P3.1/TXD 1: Pin "ASCL/P3.0/Rxd" is ASCL, Pin "ASDA/P3.1/Txd" is ASDA       |

| Register::Pin_share2 |      |            |             | 0xFF02                                                      |

|----------------------|------|------------|-------------|-------------------------------------------------------------|

| Name                 | Bits | Read/Write | Reset State | Comments                                                    |

| Reserved             | 7:5  |            | 0           | Reserved                                                    |

| CLK01E               | 4    | R/W        | 0           | 0: Pin "P6.6/CLKO1" is P6.6<br>1: Pin "P6.6/CLKO1" is CLKO1 |

| ADC3E                | 3    | R/W        | 0           | 0: Pin "P6.3/ADC3" is P6.3<br>1: Pin "P6.3/ADC3" is ADC3    |

| ADC2E                | 2    | R/W        | 0           | 0: Pin "P6.2/ADC2" is P6.2<br>1: Pin "P6.2/ADC2" is ADC2    |

| ADC1E                | 1    | R/W        | 0           | 0: Pin "P6.1/ADC1" is P6.1<br>1: Pin "P6.1/ADC1" is ADC1    |

| ADC0E                | 0    | R/W        | 0           | 0: Pin "P6.0/ADC0" is P6.0<br>1: Pin "P6.0/ADC0" is ADC0    |

# I/O port

Each I/O pin of RTD2120 can drive/sink 4mA and the internal pull up/down circuit can drive/sink 10uA.

All pins have 5V tolerance except four ADC pins: "P6.0/ADC0", "P6.1/ADC1", "P6.2/ADC2" and "P6.3/ADC3".

| Register::Port5_output_enable |      |            | 0xFF03      |                                               |  |

|-------------------------------|------|------------|-------------|-----------------------------------------------|--|

| Name                          | Bits | Read/Write | Reset State | Comments                                      |  |

| P57OE                         | 7    | R/W        | 0           | 0: P5.7 is input pin 1: P5.7 is output pin    |  |

| P56OE                         | 6    | R/W        | 0           | 0: P5.6 is input pin<br>1: P5.6 is output pin |  |

| P55OE                         | 5    | R/W        | 0           | 0: P5.5 is input pin<br>1: P5.5 is output pin |  |

| P54OE                         | 4    | R/W        | 0           | 0: P5.4 is input pin<br>1: P5.4 is output pin |  |

| P53OE                         | 3    | R/W        | 0           | 0: P5.3 is input pin<br>1: P5.3 is output pin |  |

| P52OE                         | 2    | R/W        | 0           | 0: P5.2 is input pin<br>1: P5.2 is output pin |  |

| P510E                         | 1    | R/W        | 0           | 0: P5.1 is input pin<br>1: P5.1 is output pin |  |

| P50OE                         | 0    | R/W        | 0           | 0: P5.0 is input pin<br>1: P5.0 is output pin |  |

| Register::Port6_output_enable |      |            | 0xFF04      |                                               |

|-------------------------------|------|------------|-------------|-----------------------------------------------|

| Name                          | Bits | Read/Write | Reset State | Comments                                      |

| P67OE                         | 7    | R/W        | 0           | 0: P6.7 is input pin<br>1: P6.7 is output pin |

| P66OE                         | 6    | R/W        | 0           | 0: P6.6 is input pin 1: P6.6 is output pin    |

| P65OE                         | 5    | R/W        | 0           | 0: P6.5 is input pin<br>1: P6.5 is output pin |

| P64OE                         | 4    | R/W        | 0           | 0: P6.4 is input pin<br>1: P6.4 is output pin |

| P63OE                         | 3    | R/W        | 0           | 0: P6.3 is input pin<br>1: P6.3 is output pin |

| P62OE                         | 2    | R/W        | 0           | 0: P6.2 is input pin<br>1: P6.2 is output pin |

| P61OE                         | 1    | R/W        | 0           | 0: P6.1 is input pin<br>1: P6.1 is output pin |

| P60OE                         | 0    | R/W        | 0           | 0: P6.0 is input pin 1: P6.0 is output pin    |

| Register::Port7_output_enable |      |            |             | 0xFF05                                     |

|-------------------------------|------|------------|-------------|--------------------------------------------|

| Name                          | Bits | Read/Write | Reset State | Comments                                   |

| P77OE                         | 7    | R/W        | 0           | 0: P7.7 is input pin 1: P7.7 is output pin |

| P76OE    | 6   | R/W | 0 | 0: P7.6 is input pin 1: P7.6 is output pin |

|----------|-----|-----|---|--------------------------------------------|

| Reserved | 5:0 |     | 0 | Reserved                                   |

| Register::Port1_pad_type |      |            |             | 0xFF09                                                   |

|--------------------------|------|------------|-------------|----------------------------------------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                                                 |

| P17_PPO                  | 7    | R/W        | 0           | 0:P1.7 is standar 8051 I/O<br>1:P1.7 is Push-Pull output |

| P16_PPO                  | 6    | R/W        | 0           | 0:P1.6 is standar 8051 I/O<br>1:P1.6 is Push-Pull output |

| P15_PPO                  | 5    | R/W        | 0           | 0:P1.5 is standar 8051 I/O<br>1:P1.5 is Push-Pull output |

| P14_PPO                  | 4    | R/W        | 0           | 0:P1.4 is standar 8051 I/O<br>1:P1.4 is Push-Pull output |

| P13_PPO                  | 3    | R/W        | 0           | 0:P1.3 is standar 8051 I/O<br>1:P1.3 is Push-Pull output |

| P12_PPO                  | 2    | R/W        | 0           | 0:P1.2 is standar 8051 I/O<br>1:P1.2 is Push-Pull output |

| P11_PPO                  | 1    | R/W        | 0           | 0:P1.1 is standar 8051 I/O<br>1:P1.1 is Push-Pull output |

| P10_PPO                  | 0    | R/W        | 0           | 0:P1.0 is standar 8051 I/O<br>1:P1.0 is Push-Pull output |

| Register: | :Port50_pin | _reg       | _           | 0xFF50                     |

|-----------|-------------|------------|-------------|----------------------------|

| Name      | Bits        | Read/Write | Reset State | Comments                   |

| Reserved  | 7:1         |            | 0           | Reserved                   |

| P50       | 0           | R/W        | 1           | Input/output value of P5.0 |

| Register: | Port51_pin | 0xFF51     |             |                            |

|-----------|------------|------------|-------------|----------------------------|

| Name      | Bits       | Read/Write | Reset State | Comments                   |

| Reserved  | 7:1        |            | 0           | Reserved                   |

| P51       | 0          | R/W        | 1           | Input/output value of P5.1 |

| Register::Port52_pin_reg |      |            |             | 0xFF52                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P52                      | 0    | R/W        | 1           | Input/output value of P5.2 |

| Register::Port53_pin_reg |      |            |             | 0xFF53                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P53                      | 0    | R/W        | 1           | Input/output value of P5.3 |

| Register | ::Port54_pin | _reg       | 02          | xFF54                      |   |

|----------|--------------|------------|-------------|----------------------------|---|

| Name     | Bits         | Read/Write | Reset State | Comments                   | C |

| Reserved | 7:1          |            | 0           | Reserved                   |   |

| P54      | 0            | R/W        | 1           | Input/output value of P5.4 |   |

| Register::Port55_pin_reg |      |            |             | 0xFF55                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P55                      | 0    | R/W        | 1           | Input/output value of P5.5 |

| Register::Port56_pin_reg |      |            | 0xFF56      |                            |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  | (          | 0           | Reserved                   |

| P56                      | 0    | R/W        | 1           | Input/output value of P5.6 |

| Register::Port57_pin_reg |      |            |             | 0xFF57                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P57                      | 0    | R/W        | 1           | Input/output value of P5.7 |

| Register::Port60_pin_reg |      |            |             | 0xFF58                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P60                      | 0    | R/W        | 1           | Input/output value of P6.0 |

| Register::Port61_pin_reg |      |            |             | 0xFF59                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P61                      | 0    | R/W        | 1           | Input/output value of P6.1 |

| Register | ::Port62_pin | _reg       | 0:          | xFF5A                      |   |

|----------|--------------|------------|-------------|----------------------------|---|

| Name     | Bits         | Read/Write | Reset State | Comments                   | C |

| Reserved | 7:1          |            | 0           | Reserved                   |   |

| P62      | 0            | R/W        | 1           | Input/output value of P6.2 |   |

| Register | r::Port63_pin | _reg       | 0xFF5B      |                            |

|----------|---------------|------------|-------------|----------------------------|

| Name     | Bits          | Read/Write | Reset State | Comments                   |

| Reserved | 7:1           |            | 0           | Reserved                   |

| P63      | 0             | R/W        | 1           | Input/output value of P6.3 |

| Register: | :Port64_pin | _reg       |             | 0xFF5C                     |

|-----------|-------------|------------|-------------|----------------------------|

| Name      | Bits        | Read/Write | Reset State | Comments                   |

| Reserved  | 7:1         | (          | 0           | Reserved                   |

| P64       | 0           | R/W        | 1           | Input/output value of P6.4 |

| Register::Port65_pin_reg |      |            |             | 0xFF5D                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P65                      | 0    | R/W        | 1           | Input/output value of P6.5 |

| Register::Port66_pin_reg |      |            |             | 0xFF5E                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P66                      | 0    | R/W        | 1           | Input/output value of P6.6 |

| Register::Port67_pin_reg |      |            |             | 0xFF5F                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P67                      | 0    | R/W        | 1           | Input/output value of P6.7 |

| Registe  | r::Port76_pin | ı_reg      | 02          | xFF60                      |   |

|----------|---------------|------------|-------------|----------------------------|---|

| Name     | Bits          | Read/Write | Reset State | Comments                   | C |

| Reserved | 7:1           |            | 0           | Reserved                   |   |

| P76      | 0             | R/W        | 1           | Input/output value of P7.6 |   |

| Register::Port77_pin_reg |      |            |             | 0xFF61                     |

|--------------------------|------|------------|-------------|----------------------------|

| Name                     | Bits | Read/Write | Reset State | Comments                   |

| Reserved                 | 7:1  |            | 0           | Reserved                   |

| P77                      | 0    | R/W        | 1           | Input/output value of P7.7 |

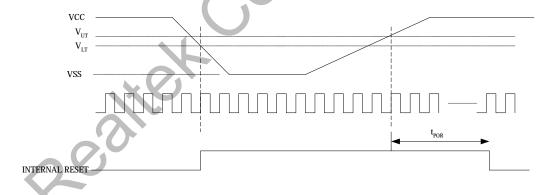

## Low Voltage Reset & Power on Reset

When the voltage level of power supply is below  $V_{LT}$ , the low voltage reset(LVR) generates a chip reset signal. After the power supply is above  $V_{UT}(2.6V)$ , LVR remain in reset state for 65536 X'tal cycle( $t_{POR}$ ) to guarantee the chip exit reset condition.

| Register::LVR_control |      |            |             | 0xFF0A   |

|-----------------------|------|------------|-------------|----------|

| Name                  | Bits | Read/Write | Reset State | Comments |

| VLT      | 7:6 | R/W | 0  | low_threshold_voltage |

|----------|-----|-----|----|-----------------------|

|          |     |     |    | 00:1.8V               |

|          |     |     |    | 01:2.0V               |

|          |     |     |    | 10:2.2V               |

|          |     |     |    | 11:2.4V               |

| reserved | 5:0 |     | 00 | reserved              |

## A/D Converter

RTD2120 has embedded 4 channels of analog-to-digital converter. The ADCs convert analog input voltage on the four A/D input pins to four 6-bit digital data stored in XFRs (FF0C~FF0F) sequentially.

The ADC conversion range is from GND to VDD and the conversion is linear and monotonic with no missing codes. To start A/D conversion, set STRT\_ADC(FF0B[7]) = 1 and the conversion will be complete in less than 12 us for 4 channels.

| Register::ADC_control |      |            |             | 0xFF0B                                                                                                                       |

|-----------------------|------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Name                  | Bits | Read/Write | Reset State | Comments                                                                                                                     |

| STRT_ADC              | 7    | R/W        | 0           | Write 1 to start the A/D conversion. Auto clear when A/D Conversion has been completed.  0:A/D Conversion has been completed |

| ADC_TEST              | 6    | R/W        | 0           | 1:A/D Conversion is not completed yet 0: Normal operation 1: ADC test mode                                                   |

| reserved              | 5:3  | R/W        | 0           | Reserved                                                                                                                     |

| BIAS_ADJ              | 2:1  | R/W        | <b>)</b> 1  | ADC bias current adjust 00: 15u 01: 20u 10: 25u 11: 30u                                                                      |

| CK_SEL                | 0    | R/W        | 0           | Inverse ADC input clock pos/neg 0: pos 1: neg                                                                                |

| Register::ADC0_convert_result |      |            |             | 0xFF0C                 |

|-------------------------------|------|------------|-------------|------------------------|

| Name                          | Bits | Read/Write | Reset State | Comments               |

| ADC0_CONV<br>_DATA            | 7:2  | R          | 3F          | Converted data of ADC0 |

| reserved                      | 1:0  |            | 00          |                        |

Register::ADC1\_convert\_result 0xFF0D

| Name               | Bits | Read/Write | Reset State | Comments               |

|--------------------|------|------------|-------------|------------------------|

| ADC1_CONV<br>_DATA | 7:2  | R          | 3F          | Converted data of ADC1 |

| reserved           | 1:0  |            | 00          |                        |

| Register::ADC2_convert_result |      |            |             |                        | 0xFF0E |

|-------------------------------|------|------------|-------------|------------------------|--------|

| Name                          | Bits | Read/Write | Reset State | Comments               |        |

| ADC2_CONV<br>_DATA            | 7:2  | R          | 3F          | Converted data of ADC2 | 6      |

| reserved                      | 1:0  |            | 00          |                        | 4      |

| Register::ADC3_convert_result |      |            |             | 0xFF0F                 |

|-------------------------------|------|------------|-------------|------------------------|

| Name                          | Bits | Read/Write | Reset State | Comments               |

| ADC3_CONV<br>_DATA            | 7:2  | R          | 3F          | Converted data of ADC3 |

| reserved                      | 1:0  |            | 00          |                        |

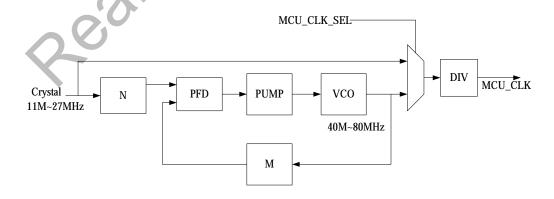

## **PLL**

RTD2120 contains a PLL to make the whole chip operate at higher or lower speed for different demands. After reset, RTD2120 uses crystal frequency as the system clock. User can program the PLL to operate at the desired frequency and select system clock to PLL output by setting MCU\_CLK\_SEL. RTD2120 will switch system clock to PLL output only when PLL is stable. Moreover, the divider is glitch free so user can modify its value at any time. For normal operation, user must choose the crystal whose frequency is between 11M and 27MHz . Besides, VCO frequency must be programmed between 40M and 80MHz.

Note: Fvco = Xtal \*(M/N), where M=M\_code+1, N=N\_code+1.

| Register::PLL_control |      |            | 0xFF10      |                                                                     |

|-----------------------|------|------------|-------------|---------------------------------------------------------------------|

| Name                  | Bits | Read/Write | Reset State | Comments                                                            |

| PLL_STA               | 7    | R          | 1           | PLL status 0: normal operation 1: PLL abnormal or PLL power down    |

| DVSET                 | 6:5  | R/W        | 2           | Test mode vctrl set<br>11(0.8v)<br>10(1.0v)<br>01(1.2v)<br>00(1.4v) |

| reserved              | 4:3  |            | 0           |                                                                     |

| WD_RST                | 2    | R/W        | 0           | 0: No effect<br>1: Watchdog reset                                   |

| WD_SET                | 1    | R/W        | 0           | 0: No effect<br>1: Watchdog set                                     |

| PWDN_PLL              | 0    | R/W        | 1           | 0: normal operation 1: power down PLL                               |

| Regist   | er::PLL_filter | _control   |             | 0xFF11                       |

|----------|----------------|------------|-------------|------------------------------|

| Name     | Bits           | Read/Write | Reset State | Comments                     |

| reserved | 7:4            |            | 0           |                              |

| VR       | 3:2            | R/W        | 0           | Loop filter resister         |

|          |                |            | CA          | 00: 16.32k                   |

|          |                |            | X \         | 01: 19.12k                   |

|          |                |            |             | 10: 21.92k                   |

|          |                |            |             | 11: 24.72k                   |

| PLL_IP   | 1:0            | R/W        | 2           | Charge Pump current          |

|          |                |            |             | Ich=5u+bit[1]*10u+ bit[0]*5u |

| Register::PLL_M_N_DIV |      |            | 0xFF12      |                                                     |

|-----------------------|------|------------|-------------|-----------------------------------------------------|

| Name                  | Bits | Read/Write | Reset State | Comments                                            |

| M_CODE                | 7:4  | R/W        | 1           | Actual M = M_CODE+1                                 |

| N_CODE                | 3:2  | R/W        | 0           | Actual N = N_CODE+1                                 |

| DIV                   | 1:0  | R/W        | 0           | Divider value<br>00:1<br>01:1/2<br>10:1/4<br>11:1/8 |

# 3.3V to 1.8V Regulator

|                    | max | typ | min |

|--------------------|-----|-----|-----|

| Input voltage(V)   |     |     | 2   |

| Output current(mA) | 80  |     |     |

| Register::regulator_control |      |            | 0xFF13      |                                                                                                         |

|-----------------------------|------|------------|-------------|---------------------------------------------------------------------------------------------------------|

| Name                        | Bits | Read/Write | Reset State | Comments                                                                                                |

| reserved                    | 7:5  |            | 0           |                                                                                                         |

| VBG                         | 4:3  | R/W        | 1           | bandgap voltage select<br>00: 1.14v<br>01: 1.20v<br>10: 1.27v<br>11: 1.34v                              |

| V_SEL                       | 2:0  | R/W        | 4           | Regulator 1.8v voltage select 000: 2.22 001: 2.12 010: 2.0 011: 1.9 100: 1.8 101: 1.7 110: 1.6 111: 1.5 |

## **DDC**

RTD2120 has two DDC ports for both D-sub and DVI interface. The external master can access DDC\_RAM1(F900~F97F) through pin ASDL and ASDA by ADC DDC channel or DDC\_RAM2 (F980~F9FF) through pin DSDL and DSDA by DVI DDC channel. Besides, the DDC\_RAM1 and DDC\_RAM2 can be combined together to form a 256-bytes DDC\_RAM for just ADC/DVI DDC slave by setting DDCRAM\_SIZ (FF26[1:0]).

The DDC of RTD2120 is compliant with VESA DDC standard. Both DDC slaves are in DDC1 mode after reset. When a high to low transition is detected on ASCL/DSCL pin, the DDC slave will enter DDC2 transition mode. The DDC slave can revert to DDC1 mode if the SCL signal keeps unchanged for 128 VSYNC periods in DDC2 transition mode and RVT\_A\_DDC1\_EN / RVT\_D\_DDC1\_EN = 1. In DDC2 transition mode, the DDC slave will lock in DDC2 mode if a valid control byte is received. Furthermore, user can force the DDC slave to operate DDC2 mode by setting A\_DDC2 / D\_DDC2 = 1.

(Refers to the VESA "Display Data Channel Standard" for detailed)

| Register::        | ADC_DDC | _enable    | 0xFF20      |                                                                                                               |

|-------------------|---------|------------|-------------|---------------------------------------------------------------------------------------------------------------|

| Name              | Bits    | Read/Write | Reset State | Comments                                                                                                      |

| A_DDC_ADD<br>R    | 7:5     | R/W        | 0           | ADC DDC Channel Address Least<br>Significant 3 Bits<br>(The default DDC channel address MSB 4<br>Bits is "A") |

| reserved          | 4       |            | 0           | Reserved                                                                                                      |

| A_DDC_W_S<br>TA   | 3       | R/W        | 0           | ADC DDC Write Status (for external DDC access only) It is cleared after write.                                |

| A_DDCRAM<br>_W_EN | 2       | R/W        | 0           | ADC DDC SRAM Write Enable (for external DDC access only)                                                      |

|          |   |     |   | 0: Disable                 |

|----------|---|-----|---|----------------------------|

|          |   |     |   | 1: Enable                  |

| A_DBN_EN | 1 | R/W | 1 | ADC DDC De-bounce Enable   |

|          |   |     |   | 0: Disable                 |

|          |   |     |   | 1: Enable (with crystal/4) |

| A_DDC_EN | 0 | R/W | 0 | ADC DDC Channel Enable Bit |

|          |   |     |   | 0: MCU access Enable       |

|          |   |     |   | 1: DDC channel Enable      |

| Register:          | :ADC_DDC | _control   | 0xFF21      |                                                                                                 |

|--------------------|----------|------------|-------------|-------------------------------------------------------------------------------------------------|

| Name               | Bits     | Read/Write | Reset State | Comments                                                                                        |

| A_DBN_CLK<br>_SEL  | 7:6      | R/W        | 0           | De-bounce clock divider 00: 1/1 reference clock 01: 1/2 reference clock 1X: 1/4 reference clock |

| A_STOP_DB<br>N_SEL | 5:4      | R/W        | 0           | De-bounce sda stage 0X: latch one stage 10: latch two stage 11: latch three stage               |

| A_SYS_CK_S<br>EL   | 3        | R/W        | 0           | De-bounce reference clock 0: crystal clock 1: PLL clock                                         |

| A_DDC2             | 2        | R/W        | 0           | Force to ADC DDC to DDC2 mode 0: Normal operation 1: DDC2 is active                             |

| RST_A_DDC          | 1        | R/W        | 0           | Reset ADC DDC circuit 0: Normal operation 1: reset (auto cleared)                               |

| RVT_A_DDC<br>1_EN  | 0        | R/W        | 0           | ADC DDC revert to DDC1 enable(SCL idle for 128 VSYNC) 0: Disable 1: Enable                      |

| Register: | :DVI_DDC_ | enable     | 0xFF23      |                                             |

|-----------|-----------|------------|-------------|---------------------------------------------|

|           |           | . <u>-</u> |             |                                             |

| Name      | Bits      | Read/Write | Reset State | Comments                                    |

|           |           |            |             |                                             |

| D_DDC_ADD | 7:5       | R/W        | 0           | DVI DDC Channel Address Least               |

| R         |           |            |             | Significant 3 Bits                          |

|           |           |            |             | (The default DDC channel address MSB 4      |

|           |           |            |             | Bits is "A")                                |

| reserved  | 4         |            | 0           | Reserved                                    |

| D_DDC_W_S | 3         | R/W        | 0           | DVI DDC External Write Status (for external |

| TA        |           |            |             | DDC access only)                            |

|           |           |            |             | It is cleared after write.                  |

| D_DDCRAM  | 2         | R/W        | 0           | DVI DDC External Write Enable (for          |

| _W_EN     |           |            |             | external DDC access only)                   |

|           |           |            |             | 0: Disable                                  |

|           |           |            |             | 1: Enable                                   |

| D_DBN_EN  | 1         | R/W        | 1           | DVI DDC Debounce Enable                     |

|           |           |            |             | 0: Disable                                  |

|           |           |            |             | 1: Enable (with crystal/4)                  |

| D_DDC_EN | 0 | R/W | 0 | DVI DDC Channel Enable Switch |

|----------|---|-----|---|-------------------------------|

|          |   |     |   | 0: MCU access Enable          |

|          |   |     |   | 1: External DDC access Enable |

| Register:          | :DVI_DD( | C_control  | 0xFF24      |                                                                                                 |

|--------------------|----------|------------|-------------|-------------------------------------------------------------------------------------------------|

| Name               | Bits     | Read/Write | Reset State | Comments                                                                                        |

| D_DBN_CLK<br>_SEL  | 7:6      | R/W        | 0           | De-bounce clock divider 00: 1/1 reference clock 01: 1/2 reference clock 1X: 1/4 reference clock |

| D_STOP_DB<br>N_SEL | 5:4      | R/W        | 0           | De-bounce sda stage 0X: latch one stage 10: latch two stage 11: latch three stage               |

| D_SYS_CK_S<br>EL   | 3        | R/W        | 0           | De-bounce reference clock 0: crystal clock 1: PLL clock                                         |

| D_DDC2             | 2        | R/W        | 0           | Force to DVI DDC to DDC2 mode 0: Normal operation 1: DDC2 is active                             |

| RST_D_DDC          | 1        | R/W        | 0           | Reset DVI DDC circuit 0: Normal operation 1: reset (auto cleared)                               |

| RVT_D_DDC<br>1_EN  | 0        | R/W        | 0           | DVI DDC revert to DDC1 enable(SCL idle<br>for 128 VSYNC)<br>0: Disable<br>1: Enable             |

| Register::DDCRAM_partition |      |            |             | 0xFF26                                                                                                                                         |

|----------------------------|------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                       | Bits | Read/Write | Reset State | Comments                                                                                                                                       |

| reserved                   | 7:3  |            | 00          | Reserved                                                                                                                                       |

| VS_CON                     | 2    | R/W        | 0           | 0: VSYNC signal is connected to ADC DDC<br>1: VSYNC signal is connected to DVI DDC                                                             |

| DDCRAM_SI<br>Z             | 1:0  | R/W        | 0           | 0x:ADC DDCRAM=128 byte, DVI<br>DDCRAM=128 byte<br>10:ADC DDCRAM=0 byte, DVI<br>DDCRAM=256 byte<br>11:ADC DDCRAM=256 byte, DVI<br>DDCRAM=0 byte |

## **IIC Interface**

| Register::IIC_set_slave | 0xFF27 |

|-------------------------|--------|

|                         |        |

| Name     | Bits | Read/Write | Reset State | Comments                    |

|----------|------|------------|-------------|-----------------------------|

|          |      |            |             |                             |

| IIC_ADDR | 7:1  | R/W        | 37          | IIC Slave Address to decode |

| CH_SEL   | 0    | R/W        | 0           | Channel Select              |

|          |      |            |             | 0: from ADC DDC             |

|          |      |            |             | 1: from DVI DDC             |

| Register::IIC_sub_in |      |            | 0xFF28      |                          |  |

|----------------------|------|------------|-------------|--------------------------|--|

|                      |      |            |             |                          |  |

| Name                 | Bits | Read/Write | Reset State | Comments                 |  |

|                      |      |            |             |                          |  |

| IIC_SUB_AD           | 7:0  | R          | 00          | IIC Sub-Address Received |  |

| DR                   |      |            |             |                          |  |

| Register | Register::IIC_data_in |            |             | 0xFF29            |

|----------|-----------------------|------------|-------------|-------------------|

| Name     | Bits                  | Read/Write | Reset State | Comments          |

| IIC_D_IN | 7:0                   | R          | 00          | IIC data received |

| Register::IIC_data_out |      |            |             | 0xFF2A                     |

|------------------------|------|------------|-------------|----------------------------|

| Name                   | Bits | Read/Write | Reset State | Comments                   |

| IIC_D_OUT              | 7:0  | W          | 00          | IIC data to be transmitted |

| Register: | :IIC_status |            | 0xFF2B      |                                                                                                               |

|-----------|-------------|------------|-------------|---------------------------------------------------------------------------------------------------------------|

| Name      | Bits        | Read/Write | Reset State | Comments                                                                                                      |

| A_WR_I    | 7           | R/W        | 0           | If ADC DDC detects a STOP condition in write mode, this bit is set to "1". Write 0 to clear.                  |

| D_WR_I    | 6           | R/W        | 0           | If DVI DDC detects a STOP condition in write mode, this bit is set to "1". Write 0 to clear.                  |

| 128VS_I   | 5           | R/W        | 0           | In DDC2 Transition mode, SCL idle for 128 VSYNC. Write 0 to clear.                                            |

| STOP_I    | 4           | R/W        | 0           | If IIC detects a STOP condition(slave address must match), this bit is set to "1". Write 0 to clear.          |

| D_OUT_I   | 3           | R          | 0           | If IIC_DATA_OUT loaded to serial-out-<br>byte, this bit is set to "1". Write IIC_data_out<br>(FF2A) to clear. |

| D_IN_I    | 2           | R          | 0           | If IIC_DATA_IN latched, this bit is set to "1". Read IIC_data_in (FF29) to clear.                             |

| SUB_I     | 1           | R/W        | 0           | If IIC_SUB latched, this bit is set to "1" Write 0 to clear.                                                  |

| SLV_I | 0 | R/W | 0 | If IIC_SLAVE latched, this bit is set to "1" |

|-------|---|-----|---|----------------------------------------------|

|       |   |     |   | Write 0 to clear.                            |

| Register::IIC_IRQ_control |      |            |             | 0xFF2C                                                                                                     |

|---------------------------|------|------------|-------------|------------------------------------------------------------------------------------------------------------|

| Name                      | Bits | Read/Write | Reset State | Comments                                                                                                   |

| AWI_EN                    | 7    | R/W        | 0           | 0: Disable the A_WR_I signal as an interrupt source     1: Enable the A_WR_I signal as an interrupt source |

| DWI_EN                    | 6    | R/W        | 0           | O: Disable the D_WR_I signal as an interrupt source     1: Enable the D_WR_I signal as an interrupt source |

| 128VSI_EN                 | 5    | R/W        | 0           | 0: Disable the 128VS_I signal as an interrupt source 1: Enable the 128VS_I signal as an interrupt source   |

| STOPI_EN                  | 4    | R/W        | 0           | O: Disable the STOP_I signal as an interrupt source  1: Enable the STOP_I signal as an interrupt source    |

| DOI_EN                    | 3    | R/W        | 0           | O: Disable the D_OUT_I signal as an interrupt source  1: Enable the D_OUT_I signal as an interrupt source  |

| DII_EN                    | 2    | R/W        | 0           | O: Disable the D_IN_I signal as an interrupt source  1: Enable the D_IN_I signal as an interrupt source    |

| SUBI_EN                   | 1    | R/W        | 0           | O: Disable the SUB_I signal as an interrupt source 1: Enable the SUB_I signal as an interrupt source       |

| SLVI_EN                   | 0    | R/W        | 0           | 0: Disable the SLV_I signal as an interrupt source 1: Enable the SLV_I signal as an interrupt source       |

## **PWM**

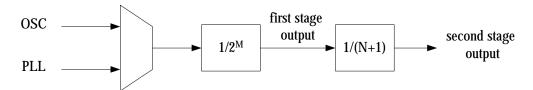

RTD2120 supports 3 channels of PWM DAC. The resolution of each PWM is 8-bit. PWM0, PWM1and PWM2 are connected to DA0, DA1and DA2 respectively. Meanwhile, they can also be connected to DA3, DA4 and DA5 which are programed via PWM\_source\_select register. The figure below represent the PWM clock generator. Based on the clock, we make up the PWM waveform which frequency is 1/256 of the PWM clock.

## PWM clock generator

| Register::PWM_clock_control |      |            | 0xFF30      |                                                            |

|-----------------------------|------|------------|-------------|------------------------------------------------------------|

| Name                        | Bits | Read/Write | Reset State | Comments                                                   |

| PWM_EN                      | 7    | R/W        | 0           | 0: Disable PWM output 1: Enable PWM output                 |

| PWM0_CK                     | 6    | R/W        | 0           | 0: Select first stage output 1: Select second stage output |

| PWM1_CK                     | 5    | R/W        | 0           | Select first stage output     Select second stage output   |

| PWM2_CK                     | 4    | R/W        | 0           | Select first stage output     Select second stage output   |

| PWM_CK_SE<br>L              | 3    | R/W        | 0           | PWM clock generator input source 0: Crystal 1: PLL output  |

| reserved                    | 2    |            | 0           | Reserved                                                   |

| PWM_M                       | 1:0  | R/W        | 0           | PWM clock first stage divider                              |

| Register::PWM_divider_N |      |            | 0xFF31      |                                |

|-------------------------|------|------------|-------------|--------------------------------|

| Name                    | Bits | Read/Write | Reset State | Comments                       |

| PWM_N                   | 7:0  | R/W        | 0           | PWM clock Second stage divider |

| Register::PWM0_duty_width |      |            | 0xFF32      |                 |

|---------------------------|------|------------|-------------|-----------------|

| Name                      | Bits | Read/Write | Reset State | Comments        |

| PWM0_DUT                  | 7:0  | R/W        | 0           | PWM0 duty width |

| Register::PWM1_duty_width |      |            | 0xFF33      |                 |

|---------------------------|------|------------|-------------|-----------------|

| Name                      | Bits | Read/Write | Reset State | Comments        |

| PWM1_DUT                  | 7:0  | R/W        | 0           | PWM1 duty width |

| Register: | Register::PWM2_duty_width |            |             | 0xFF34          |

|-----------|---------------------------|------------|-------------|-----------------|

| Name      | Bits                      | Read/Write | Reset State | Comments        |

| PWM2_DUT  | 7:0                       | R/W        | 0           | PWM2 duty width |

| Register::PWM_source_select |      |            |             | 0xFF35                                                                                       |

|-----------------------------|------|------------|-------------|----------------------------------------------------------------------------------------------|

| Name                        | Bits | Read/Write | Reset State | Comments                                                                                     |

| reserved                    | 7:6  |            | 0           | Reserved                                                                                     |

| PWM5_SEL                    | 5:4  | R/W        | 2           | 00: PWM5 is the same as PWM0<br>01: PWM5 is the same as PWM1<br>1x: PWM5 is the same as PWM2 |

| PWM4_SEL                    | 3:2  | R/W        | 1           | 00: PWM4 is the same as PWM0<br>01: PWM4 is the same as PWM1<br>1x: PWM4 is the same as PWM2 |

| PWM3_SEL                    | 1:0  | R/W        | 0           | 00: PWM3 is the same as PWM0<br>01: PWM3 is the same as PWM1<br>1x: PWM3 is the same as PWM2 |

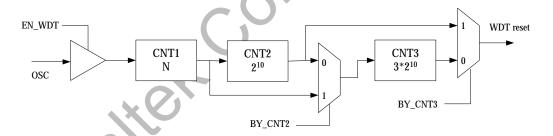

## **Watchdog Timer**